## Development of an FPGA emulator for the RD53B chip

NIHARIKA MITTAL ACME LAB UNIVERSITY OF WASHINGTON

GIT: <u>https://gitlab.com/scotthauck/largehadroncollider</u>

UNIVERSITY of WASHINGTON

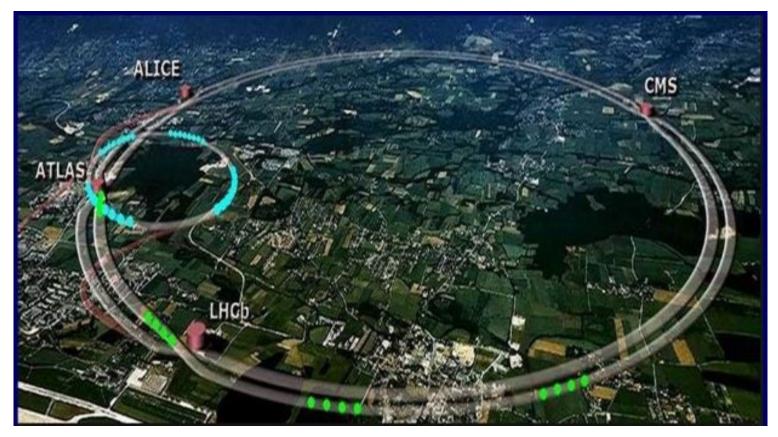

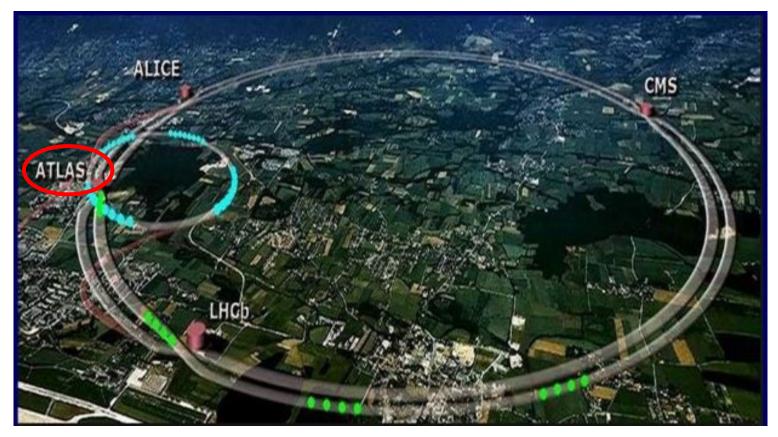

Figure 1: Aerial depiction of Large Hadron Collider and its experiment sites [CERN]

Figure 1: Aerial depiction of Large Hadron Collider and its experiment sites [CERN]

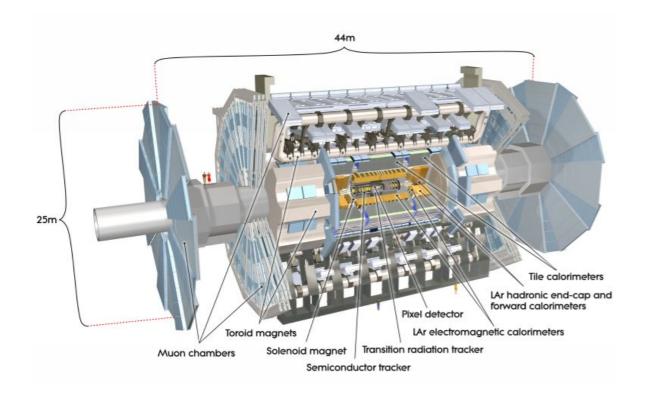

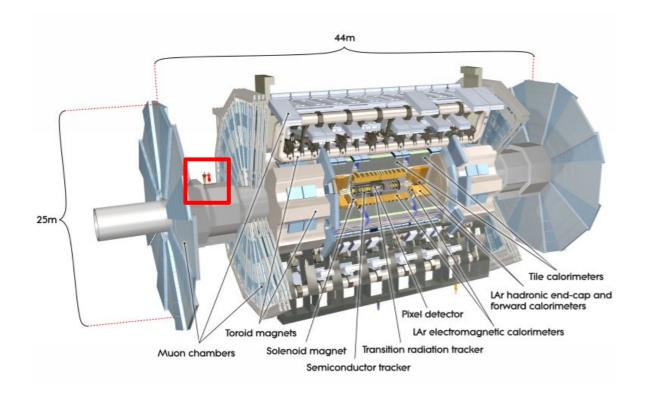

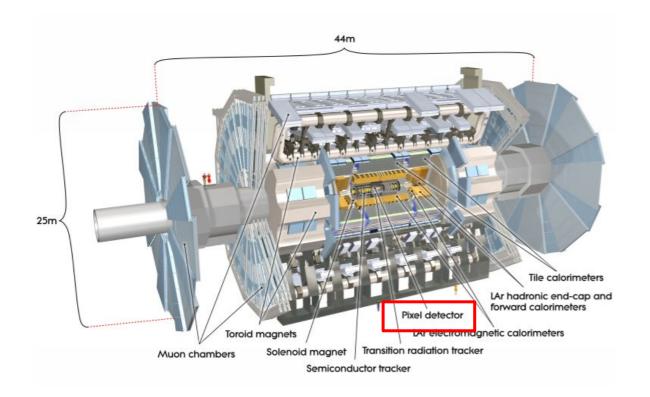

Figure 2: ATLAS detector [CERN]

Figure 2: ATLAS detector [CERN]

Figure 2: ATLAS detector [CERN]

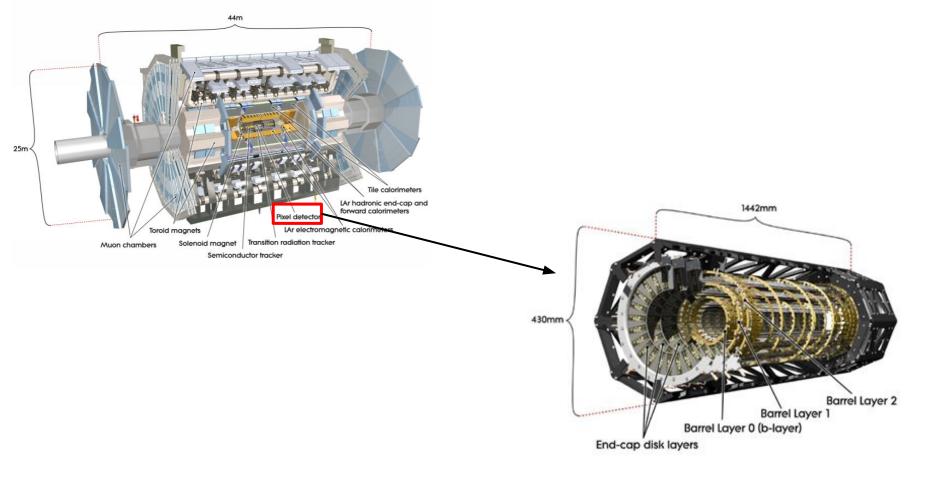

Figure 3: Pixel Detector [CERN]

**Image Source**

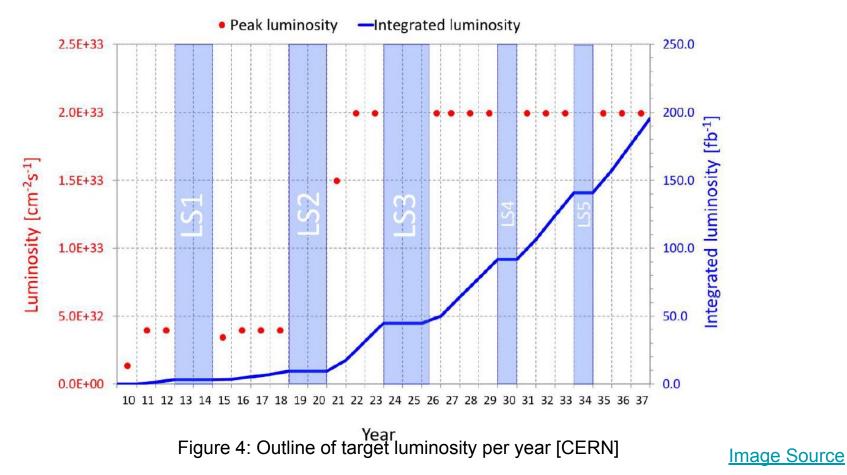

## HL-LHC/ ITk PIXEL UPGRADE

#### **RD53B CHIP**

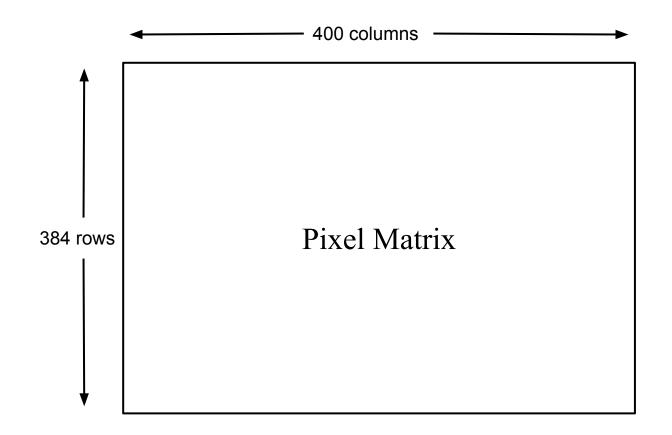

RD53B is a pixel readout chip framework

The design framework is built upon the RD53A framework

|              | RD53A | RD53B  |

|--------------|-------|--------|

| No of pixels | 76800 | 153600 |

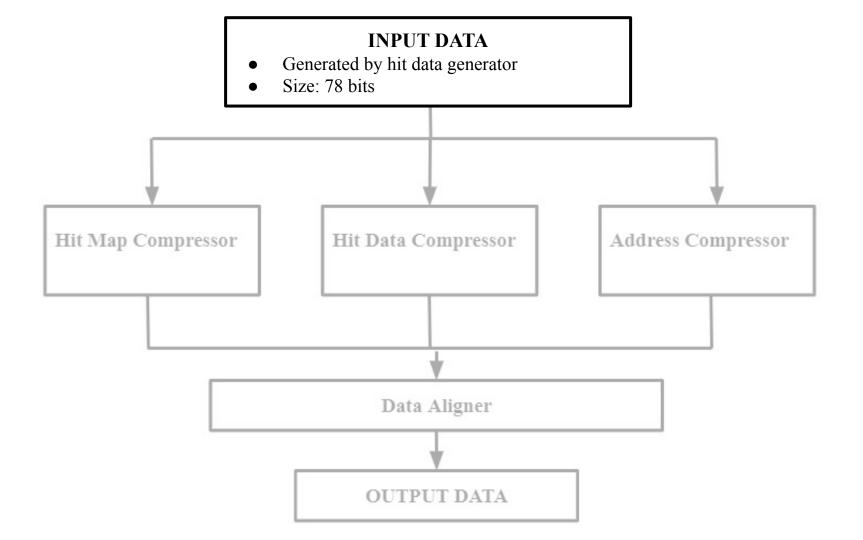

# EMULATOR

Hardware or software that enables one computer system to behave like another computer system

# **EMULATOR**

Hardware or software that enables one computer system to behave like another computer system

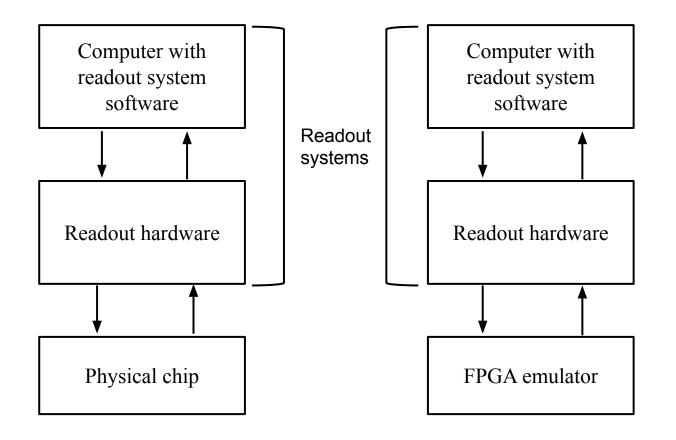

# **RD53B EMULATOR**

Mapping of important features of the RD53B ASIC design onto an FPGA using Verilog HDL to allow communications testing

#### **PURPOSE OF RD53B EMULATOR**

- A flexible model of the RD53B implemented on an FPGA

- Helps in testing/debugging of DAQ (Data Acquisition)

- Helps to debug the RD53B chip

- Produces more "realistic" hit (collision) data

## **Before B there was A**

# **RD53A EMULATOR**

Formats and decodes input

Based on the commands received, generates corresponding data

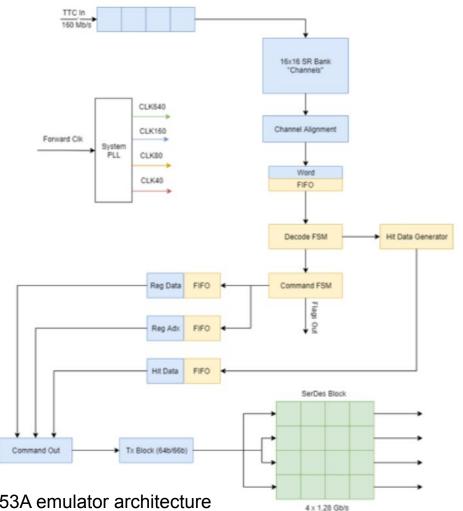

Figure 5: RD53A emulator architecture

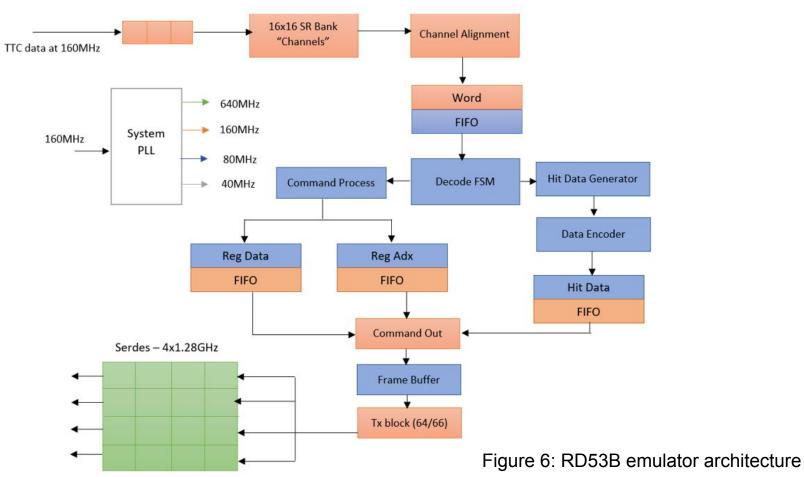

### **RD53B EMULATOR**

### **RD53B EMULATOR**

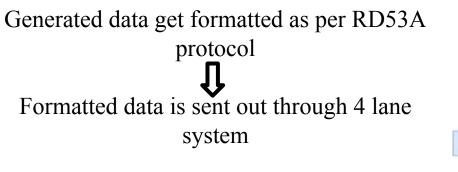

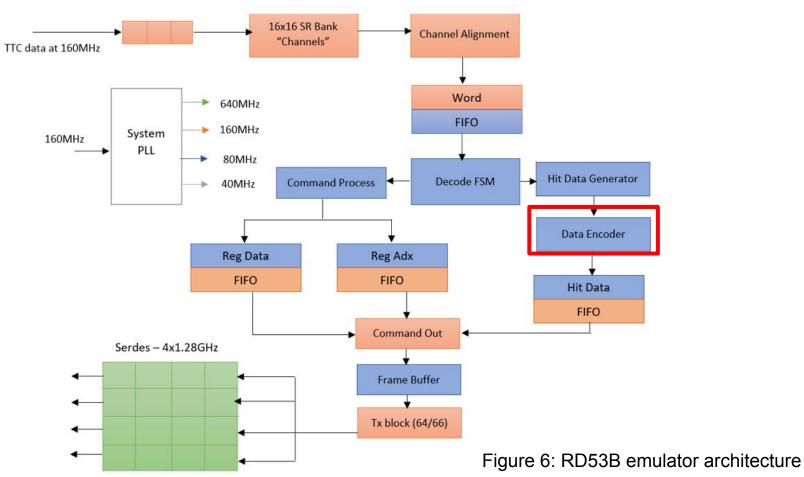

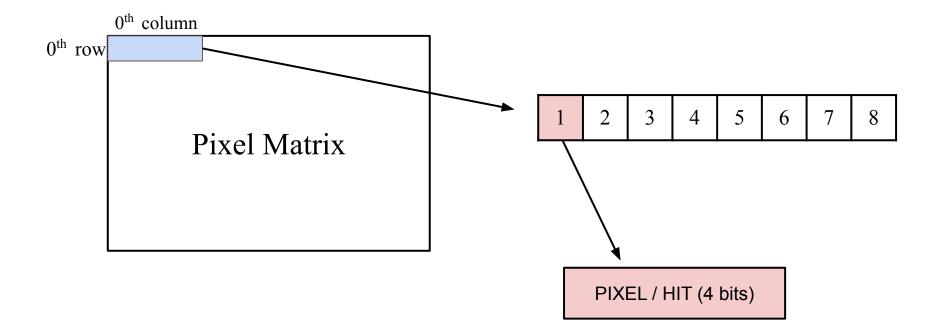

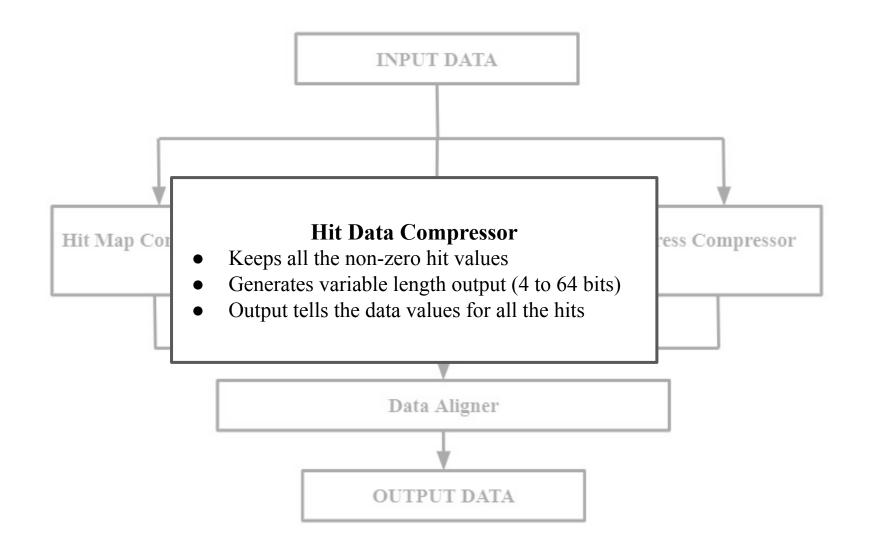

#### **DATA ENCODING**

#### **DATA ENCODING**

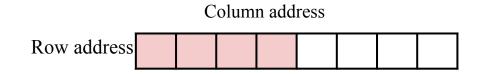

| 6 bits         | 9 bits                     | 1 bit | 16 bits          |  |  |  |

|----------------|----------------------------|-------|------------------|--|--|--|

| Column address | Column address Row address |       | Data of 4 pixels |  |  |  |

| ▲ 32 bits      |                            |       |                  |  |  |  |

| 6 bits         | 9 bits      | 64 bits           |  |  |

|----------------|-------------|-------------------|--|--|

| Column address | Row address | Data of 16 pixels |  |  |

|                | 78 hita     |                   |  |  |

| 6 bits         | 9 bits      | 64 bits           |  |  |

|----------------|-------------|-------------------|--|--|

| Column address | Row address | Data of 16 pixels |  |  |

| <              | 78 bits     |                   |  |  |

| 6 bits         | 9 bits      | 64 bits           |  |  |

|----------------|-------------|-------------------|--|--|

| Column address | Row address | Data of 16 pixels |  |  |

| ◀              | 78 bits     |                   |  |  |

| 6 bits         | 9 bits      | 64 bits           |  |  |

|----------------|-------------|-------------------|--|--|

| Column address | Row address | Data of 16 pixels |  |  |

| <              | 78 bits     |                   |  |  |

| 6 bits         | 9 bits      | 64 bits           |  |  |

|----------------|-------------|-------------------|--|--|

| Column address | Row address | Data of 16 pixels |  |  |

| <              | 78 bits     |                   |  |  |

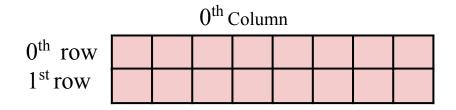

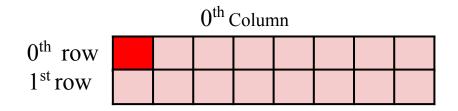

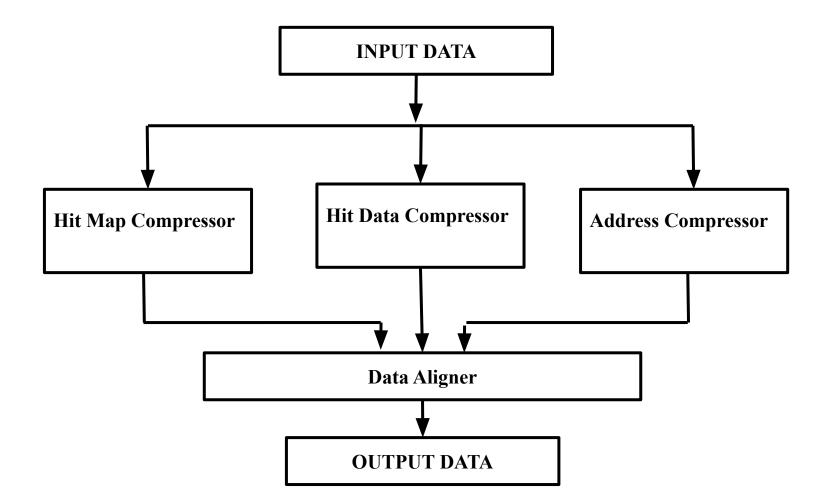

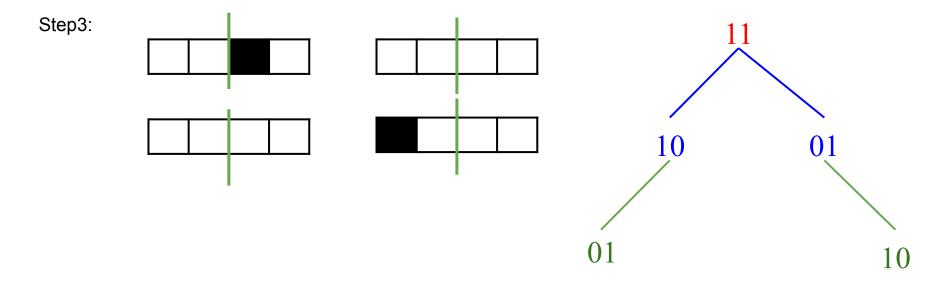

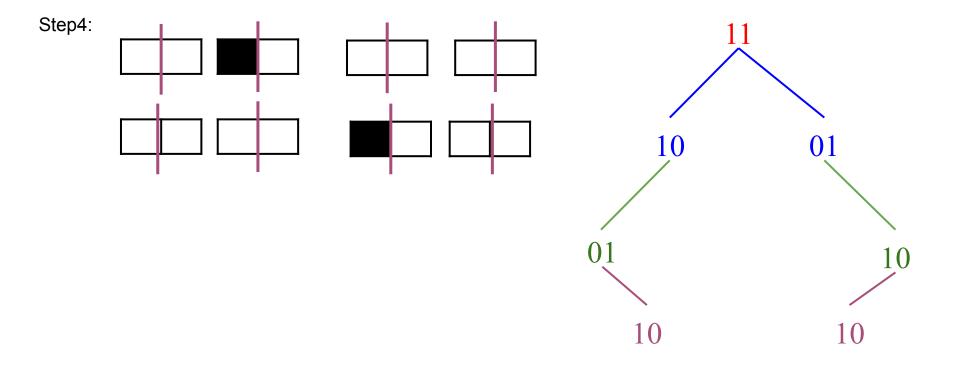

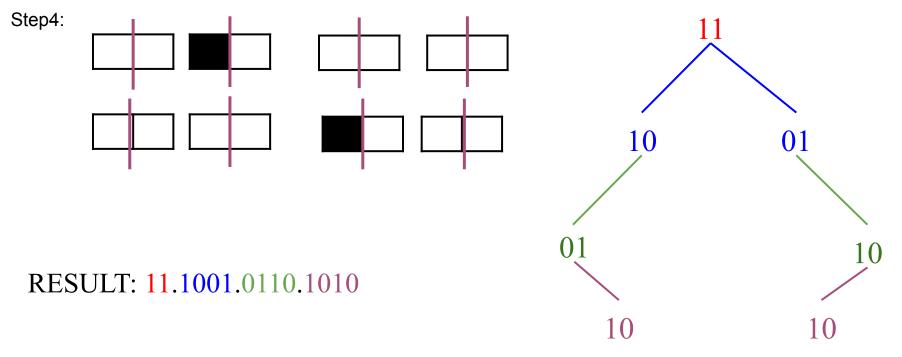

#### **RD53B EMULATOR'S DATA ENCODER**

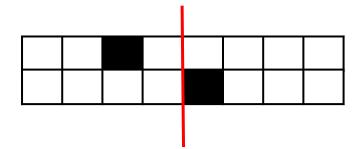

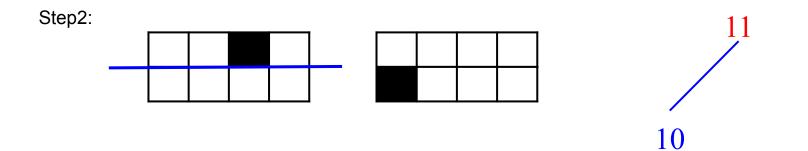

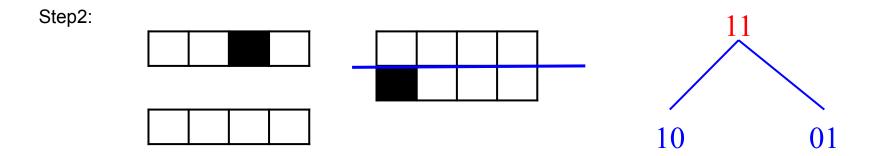

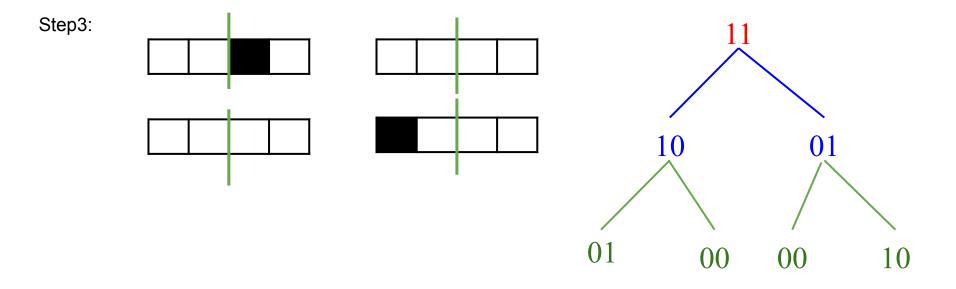

Step1:

1

Step1:

11

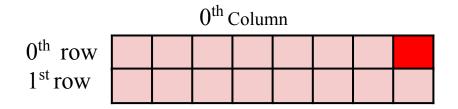

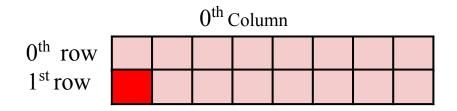

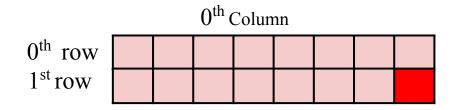

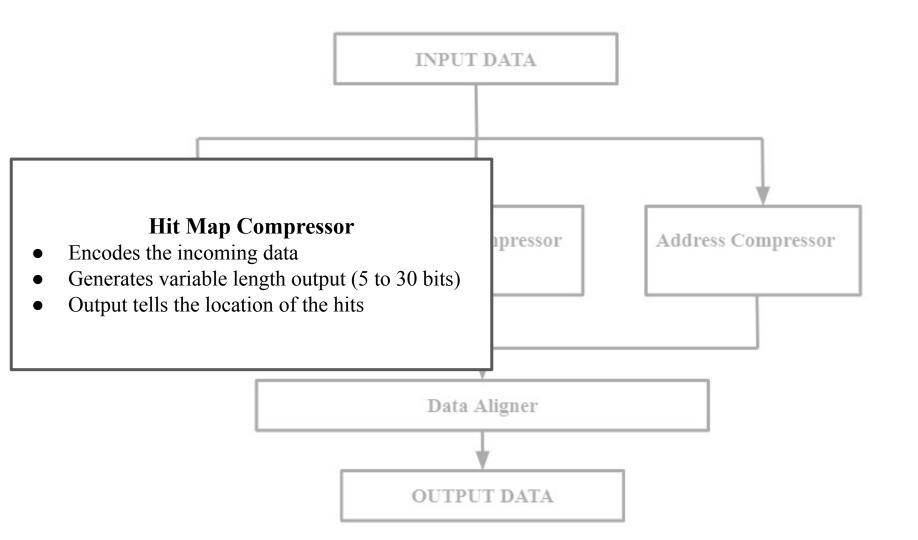

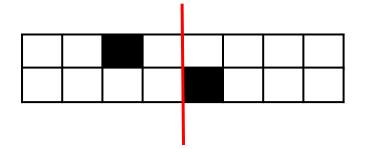

#### **HIT MAP COMPRESSION**

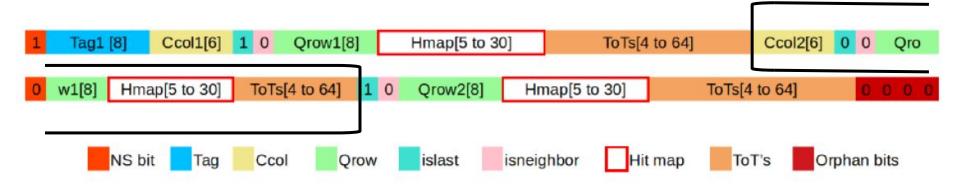

## FINAL STREAM OF DATA

## FINAL STREAM OF DATA

## FINAL STREAM OF DATA

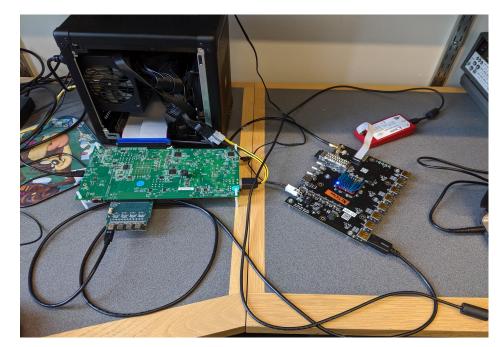

• YARR (Yet Another Rapid Readout)

Figure 7: YARR setup at UW

- YARR (Yet Another Rapid Readout)

- RCE (Reconfigurable Cluster Element)

Figure 8: RCE setup at UW

- YARR (Yet Another Rapid Readout)

- RCE (Reconfigurable Cluster Element)

- FELIX (Front End Link eXchange)

Figure 9: FELIX setup at UW

## CONCLUSION

- Development of RD53B emulator at UW

- Communication between readout systems and RD53B emulator

- Stayed as close to the RD53B specifications as possible, while developing the FPGA based design

## REFERENCES

[1] <u>https://home.cern/</u> "CERN website", CERN, [Online]

[2] <u>https://atlas.cern/discover/detector</u> "CERN atlas website", CERN, [Online]

[3] "<u>Image Source</u>", [Online]

[4] The ATLAS Collaboration, "The RD53A integrated circuit", Memo. CERN-RD53-PUB-17-001, January 30, 2017

[5] "The RD53B Pixel Readout Chip Manual", Version 0.38, April 14, 2020

[6] RD53A Emulator: <u>https://gitlab.com/smithd57/rd53a\_hardware\_emulator\_dev</u>

Thank you Scott and Shih-Chieh Thank you ACME and LBNL team

## **IF FURTHER EXPLANATION NEEDED**

# **RD53B EMULATOR FEATURES**

- Input data is decoded properly using the custom RD53B protocol

- Output data is properly encoded using the aurora 64/66 protocol at 640MHz

- Reading and writing of global registers.

- Hit data is encoded as per the RD53B specifications

- Trigger commands cause the output of sets of encoded hit data

## **RD53B EMULATOR NON-FEATURES**

- Since this is a digital design project any RD53B features that involve analog circuitry such as the pixels have been greatly simplified or removed entirely

- Commands such as 'Clear' and 'Cal' are received by the FPGA but have no effect

- The input clock is not derived from the input stream using clock data recovery but needs to be provided to the system as a separate signal

## **RD53A COMMAND AND THEIR FORMATTING**

| Command     | Encoding                | ID/(A)ddress/(D)ata 5-bit Fields |          |              |          |           |         |  |

|-------------|-------------------------|----------------------------------|----------|--------------|----------|-----------|---------|--|

| ECR         | 2× 0101_1010            |                                  |          |              |          |           |         |  |

| BCR         | $2 \times 0101 \_ 1001$ |                                  |          | 84.          |          |           |         |  |

| Glob. Pulse | $2 \times 0101 \_ 1100$ | ID<3:0>,0                        | D<4:0>   |              |          |           |         |  |

| Cal         | 2× 0110_0011            | ID<3:0>,D15                      | D<14:10> | D<9:5>       | D<4:0>   |           |         |  |

| WrReg       | $2 \times 0110 0110$    | ID<3:0>,0                        | A<8:4>   | A<3:0>,D<15> | D<14:10> | D<9:5>    | D<4:0>  |  |

| WrReg       | 2× 0110_0110            | ID<3:0>,1                        | A<8:4>   | A<3:0>,D<15> | D<14:10> | 9×(D<9:5> | D<4:0>) |  |

| RdReg       | $2 \times 0110 0101$    | ID<3:0>,0                        | A<8:4>   | A<3:0>,0     | 00000    |           |         |  |

| Noop        | 2× 0110_1001            |                                  | 8<br>10  |              | in i     |           |         |  |

| Sync        | 1000_0001_0111_1110     |                                  |          |              |          |           |         |  |

## **RD53B COMMAND AND THEIR FORMATTING**

| Command      | Encoding  |           | (T)ag, (A)ddress or (D)ata 5-bit content |          |           |         |        |           |  |

|--------------|-----------|-----------|------------------------------------------|----------|-----------|---------|--------|-----------|--|

| Sync         | 1000_0001 | 0111_1110 |                                          |          |           |         |        |           |  |

| PLLlock      | 1010_1010 | 1010_1010 |                                          |          |           |         |        |           |  |

| Trigger      | tttt_tttt | Tag[053]  |                                          |          |           |         |        |           |  |

| Read_trigger | 0110_1001 | ID<4:0>   | 00, <b>T</b> <7:5>                       | T<4:0>   |           |         |        |           |  |

| Clear        | 0101_1010 | ID<4:0>   |                                          |          |           |         |        |           |  |

| Global Pulse | 0101_1100 | ID<4:0>   |                                          | 5N 5     | 6N 3      | 2 N     |        |           |  |

| Cal          | 0110_0011 | ID<4:0>   | D<19:15>                                 | D<14:10> | D<9:5>    | D<4:0>  |        |           |  |

| WrReg(0)     | 0110_0110 | ID<4:0>   | 0,A<8:5>                                 | A<4:0>   | D<15:11>  | D<10:6> | D<5:1> | D<0>,0000 |  |

| WrReg(1)     | 0110_0110 | ID<4:0>   | 1,xxxx                                   | XXXXX    | N×(D<9:5> | D<4:0>) |        |           |  |

| RdReg        | 0110_0101 | ID<4:0>   | 0,A<8:5>                                 | A<4:0>   |           | is      |        |           |  |

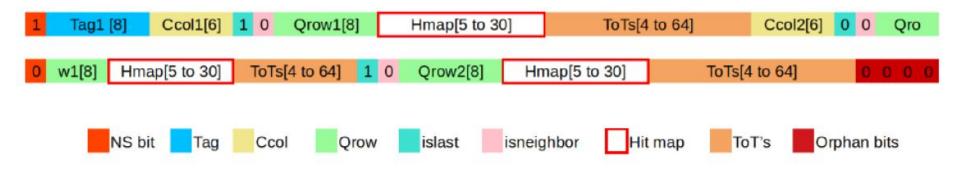

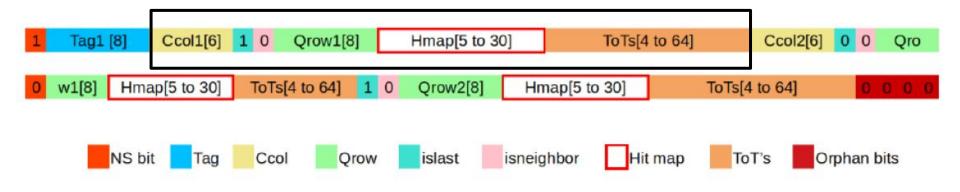

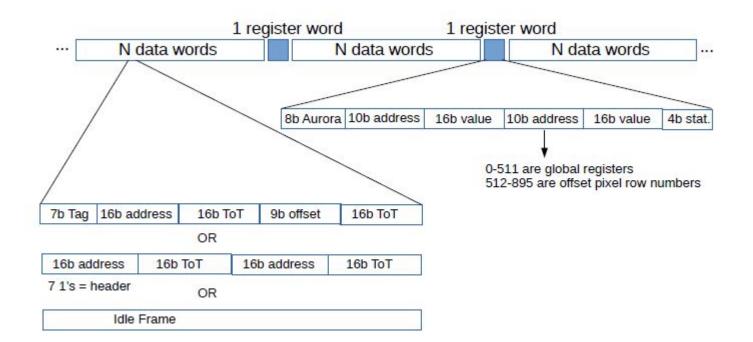

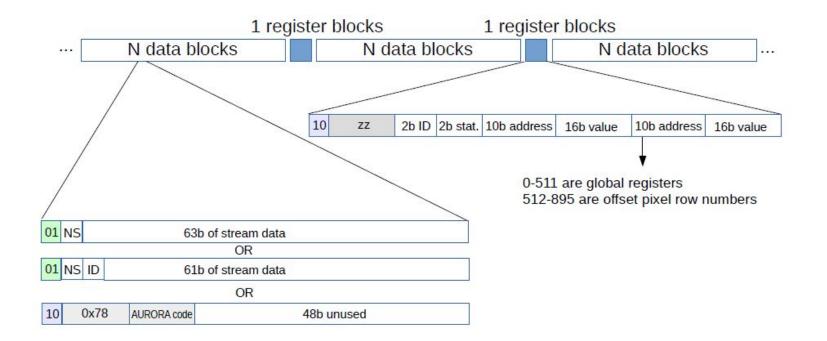

### **RD53A OUTPUT DATA FORMATTING**

### **RD53B OUTPUT DATA FORMATTING**

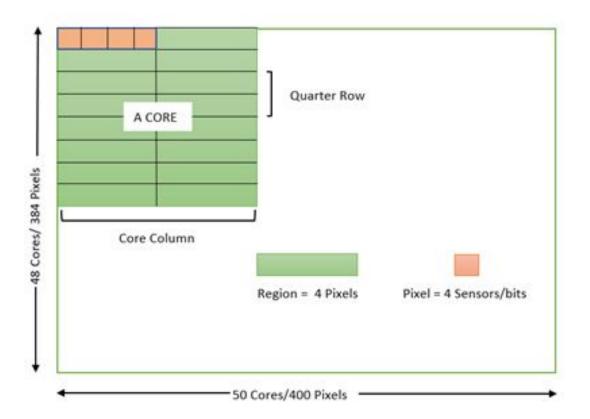

#### **ADDRESSING - RD53A**

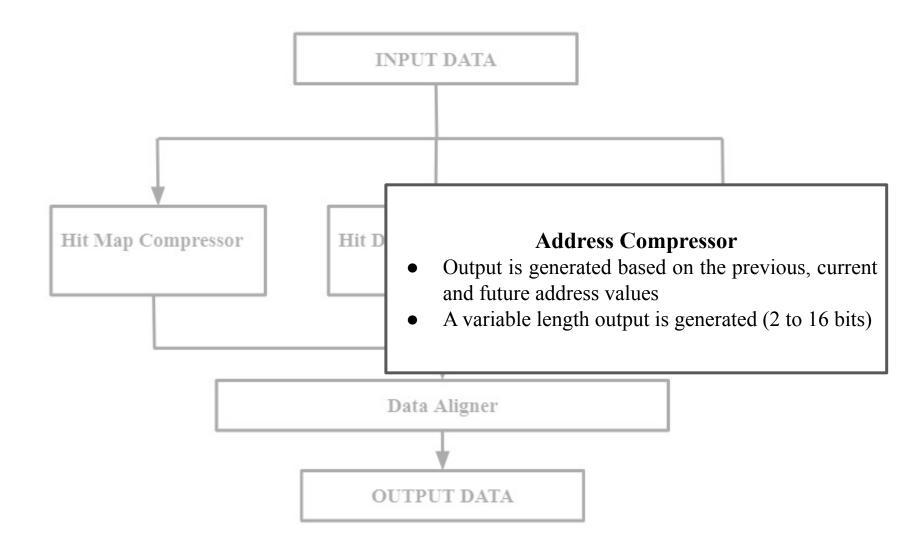

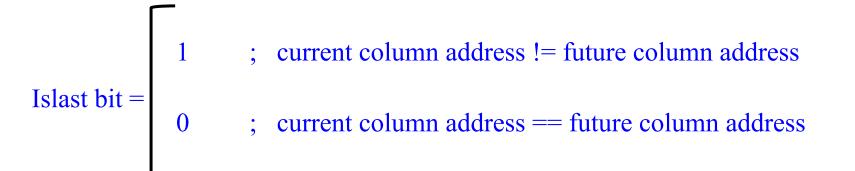

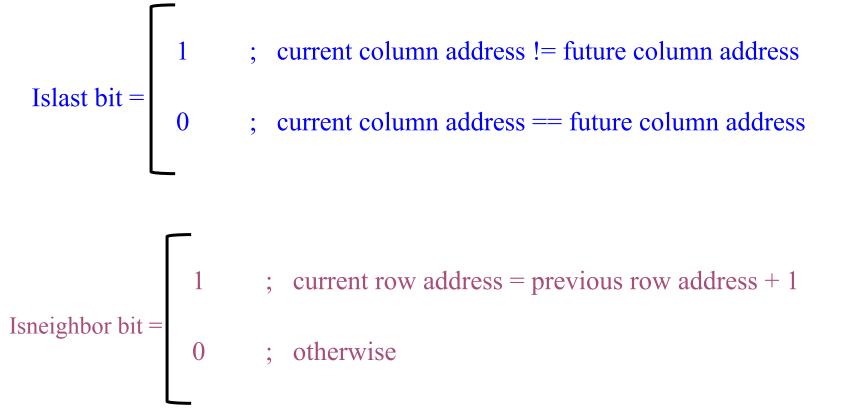

### **ADDRESS COMPRESSOR**

### **ADDRESS COMPRESSOR**

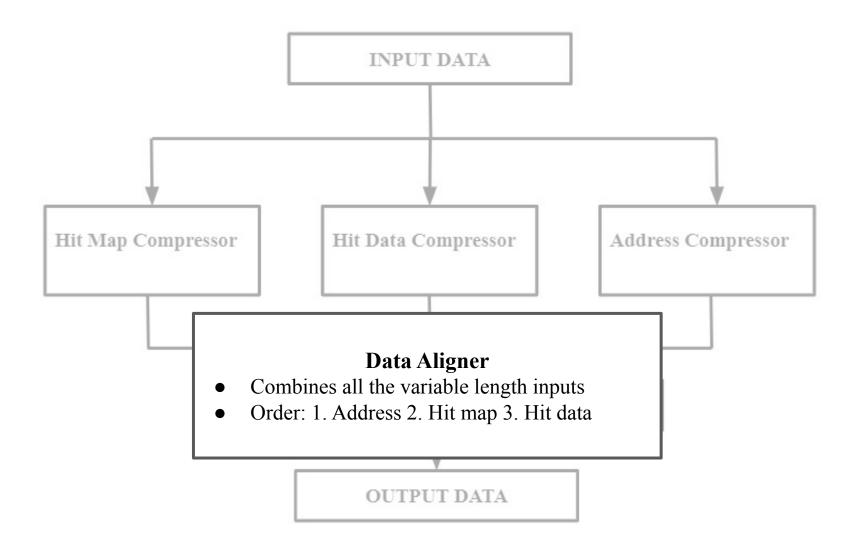

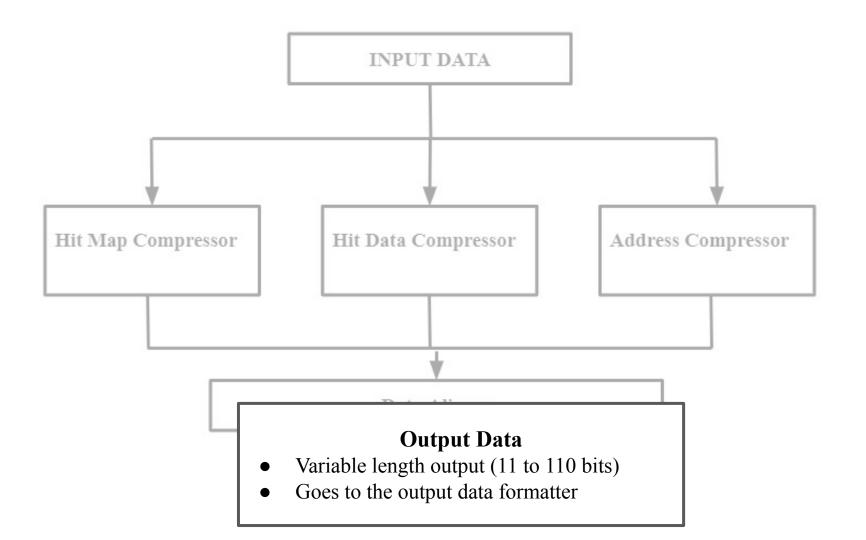

### **DATA ALIGNER**

Address = 110010000000000

Address\_Length = 5

HitMap = 1001110000000000

HitMap\_Length = 6

HitData = 111010000000000

HitData\_Length = 5

```

Shifted_HitMap = HitMap >> Address_Length

= 000001001110000000

```

```

Shifted_HitData = HitData >> (Address_Length + HitMap_Length)

= 0000000000111010

```

Result = Address + Shifted\_HitMap + Shifted\_HitData = 11001.100111.11101.0