\_

# **Topics**

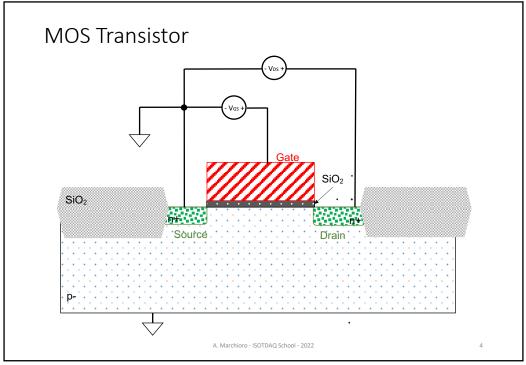

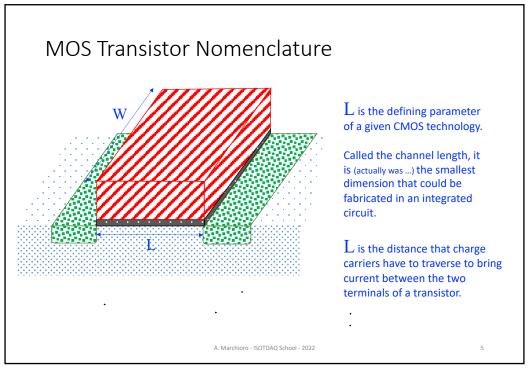

- Refresher: what is a MOS transistor and how does it work?

- Past predictionsHow good are we at "forecasting (imagining?) the future"?

- Revisit the major innovations that allowed VLSI scaling to go-on for 50+ years

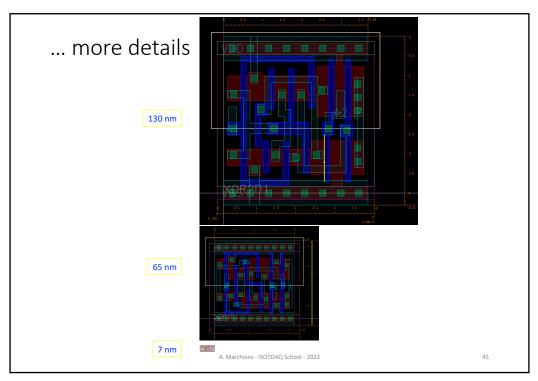

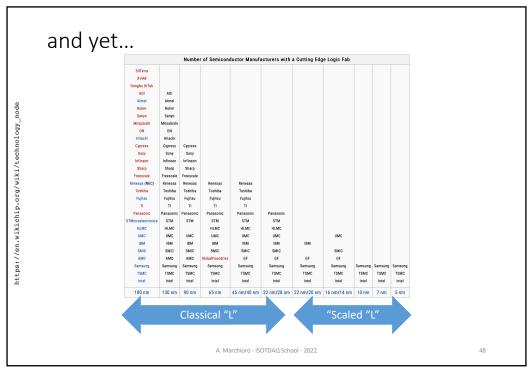

- Sub 10 nm devices are now on the market

- ... and few atomic layers are leftare we approaching the end of the road?

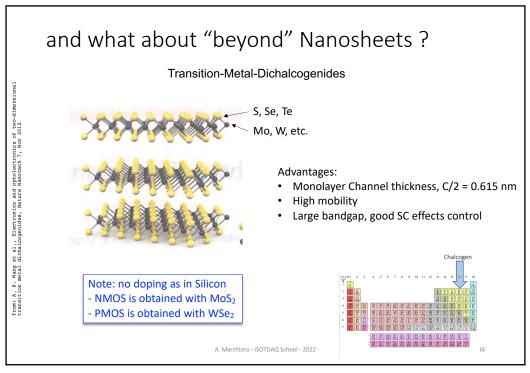

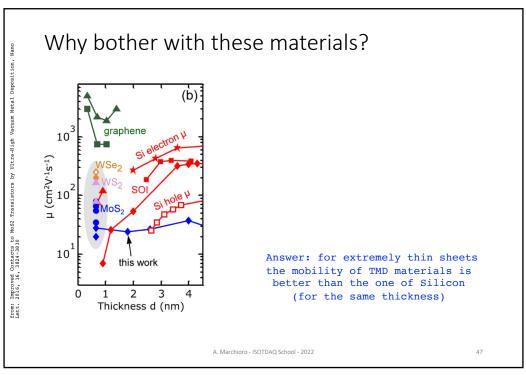

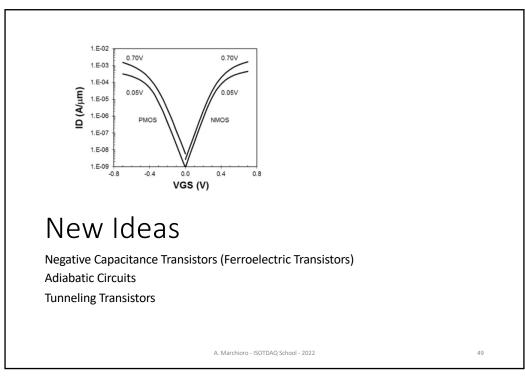

- Possible innovations allowing growth for another generation

- (Several) new devices current research

Innovative circuit from

- What use to make of sub-10nm transistors in HEP

A. Marchioro - ISOTDAQ School - 2022

# Real NMOS Transistor FOFSM340 A Marchioro - ISOTDAQ School - 2022 6

# What do we want from a transistor anyway? (sorry analog engineers...)

- A transistor (a digital transistor) is a device that "should" have the following characteristics:

- works as a switch (on or off)

- three terminals: an input, an output, a control

- makes a "sharp" transition between the two states (open or closed) in a time as short as possible (i.e. carry charge quickly through it)

- no leakage current when off ( $I_{on}/I_{off} > [>] 10^6$ )

- ... while delivering high current when on (drive strongly the load),  $l_{\text{no min}} \simeq 1\text{mA/um}$

- control terminal induces a transition between the two states with a voltage drive ( $V_{tr}$ ) as small as possible:  $P= \frac{1}{2} C \ V_{dd}^2$  (today  $V_{tr} \sim 1/2 \ V_{dd}$ )

- control terminal should not be influenced by input/output terminal(s)

- be physically small (otherwise other "parasitics" ruin the party)

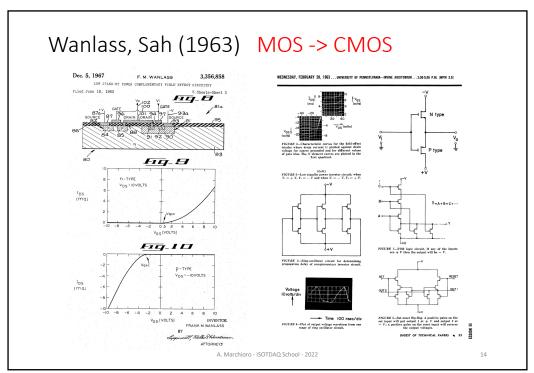

- must have complementary type (i.e. a second type which is turned on when the first is turned off using the same "control").

- "Good analog" characteristics are desirable but by far not necessary or even important for the the majority of applications.

In fact modern deep-submicron devices have "horrible" analog characteristics and analog designers have a hard time to achieve what was "easy" 20 years ago

A. Marchioro - ISOTDAQ School - 2022

7

7

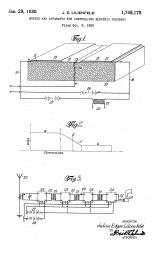

# Lilienfeld (1926)

A. Marchioro - ISOTDAQ School - 2022

## Lilienfeld: right and wrong

Over both of the coatings 11 and 12, the intermediate upper surface portion of the glass 10, and the edge of the foil 13 is provided a film or coating 15 of a compound having the property of acting in conjunction with said metal foil electrode as an element of uni-directional conductivity. That is to say, this coating is to be electrically conductive and possess also the property, when associated with other suitable conductors, of establishing at the surface of contact a considerable drop of potential. The thickness of the film, moreover, is minute and of such a degree that the electrical conductivity therethru would be influenced by applying thereto an electrostatic force. A suitable material for this film and especially suitable in conjunction with aluminum foil, is a compound of copper and sulphur. A convenient way of providing the film over the coatings

The basis of the invention resides apparently in the fact that the conducting layer at the particular point selected introduces a resistance varying with the electric field at this point; and in this connection it may be assumed that the atoms (or molecules) of a conductor are of the nature of bipoles. In order for an electron, therefore, to travel in the electric field, the bipoles are obliged to become organized in this field substantially with their axes parallel or lying in the field of flow. Any disturbance in this organization, as by heat movement, magnetic field, electrostatic cross-field, etc., will serve to increase the resistance of the conductor; and in the instant case, the conductivity of the layer is influenced by the electric field. Owing to the fact that this layer is extremely thin the field is permitted to penetrate the entire volume thereof and thus will change the conductivity throughout the entire cross-section of this conducting portion.

J.E. Lilienfeld patent, page 2

J.E. Lilienfeld patent, page 3

A. Marchioro - ISOTDAQ School - 2022

9

9

# Co. Heil (1935) 108194 ROYAUME DE BELGIQUE ROYAU

# Si and SiO<sub>2</sub> – The chicken and the egg

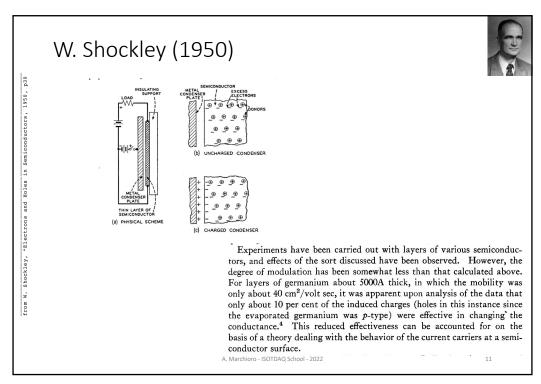

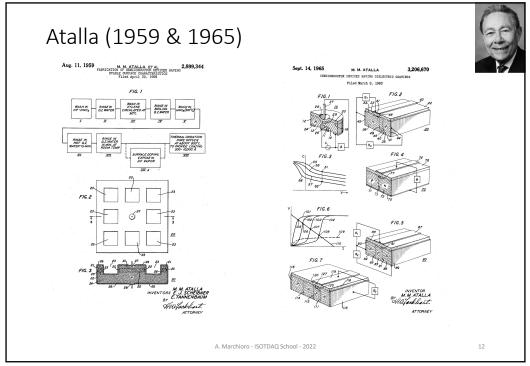

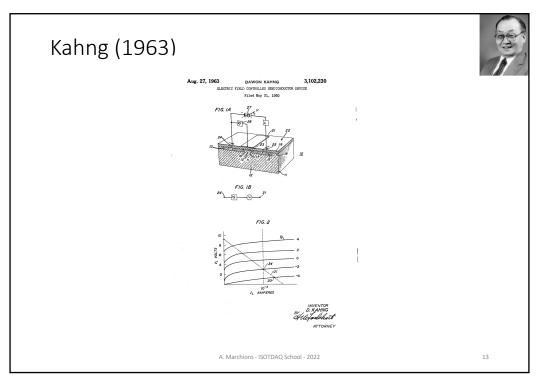

An ideal interface is one where all of the atomic bonds are satisfied through couplings between the two layers. The successful MOSFET is very sensitive to the degree of interface perfection. Silicon dioxide on silicon is the combination of materials that comes closest to this ideal, with only one electrically active imperfection (defect) for every 100000 surface atoms. This is truly remarkable when one realizes that the two materials are so different, the oxide being an amorphous insulator and the silicon a high quality, single crystal, semiconductor. Hans Quiesser, in his exciting book, Conquest of the Microchip [14], describes the early difficulties of surface passivation and writes: "what finally saved the day was that an incredibly stable oxide of silicon can be wrapped around the crystal to protect it." Another historical account, The History of Engineering & Science in the Bell System [15], describes "surface state problems were resolved by an unexpected discovery .... Kahng and Atalla found that silicon and clean, thermally grown SiO<sub>2</sub> interfaces contain sufficiently small surface states to realize a true field effect transistor in silicon." The

A. Marchioro - ISOTDAQ School - 2022

15

15

# Seeff-Asligned Gates MITAL-NITRIDE CXIDE-SILICON FIELD-EFFECT TRANSISTORS, WITH past 34-66. Nined a Cruz Boint MRTAL-NITRIDE CXIDE-SILICON FIELD-EFFECT TRANSISTORS, WITH past 34-66. Nined a Cruz Boint MRTAL-NITRIDE CXIDE-SILICON FIELD-EFFECT TRANSISTORS, WITH past 34-66. Nined a Cruz Boint MRTAL-NITRIDE CXIDE-SILICON FIELD-EFFECT TRANSISTORS, WITH past 34-66. Nined a Cruz Boint MRTAL-NITRIDE CXIDE-SILICON FIELD-EFFECT TRANSISTORS, WITH past 34-66. Nined a Cruz Boint MRTAL-NITRIDE CXIDE-SILICON FIELD-EFFECT TRANSISTORS, WITH past 34-66. Nined a Cruz Boint MRTAL-NITRIDE CXIDE-SILICON FIELD-EFFECT TRANSISTORS, SELF-ALIGORID GATES 1. C. Super all many and past 4 miles of the Cruz Boint MRTAL-NITRIDE CXIDE-SILICON FIELD-EFFECT TRANSISTORS, SELF-ALIGORID GATES 467 MRTAL-NITR

# **Problems and Predictions**

"Prediction is very difficult, especially about the future"

Niels Bohr

A. Marchioro - ISOTDAQ School - 2022

17

17

# Past predictions (1971)

Solid-State Electronics, 1972, Vol. 15, pp. 819-829. Pergamon Press. Printed in Great Britain

# FUNDAMENTAL LIMITATIONS IN MICROELECTRONICS—I. MOS TECHNOLOGY\*

B. HOENEISEN and C. A. MEAD

California Institute of Technology, Pasadena, California 91109, U.S.A.

(Received 11 August 1971; in revised form 8 November 1971)

The minimum channel length of a 2V transistor is  $\approx 0.4 \, \mu \text{m}$ . This length is a factor of 10 smaller than the channel of the smallest present day devices. The mask alignment tolerances required to manufacture such a device are within the capabilities of electron beam pattern generation techniques. Thus we can envision fully dynamic or complementary integrated silicon chips with up to  $\approx 3 \times 10^7$  MOS transistors per cm², operating in the 10 to 30 MHz range, as shown in Fig. 1.

A. Marchioro - ISOTDAQ School - 2022

18

### The foundation paper (1974)

### Design of Ion-Implanted MOSFET's with Very Small Physical Dimensions

ROBERT H. DENNARD, MEMBER, IEEE, FRITZ H. GAENSSLEN, HWA-NIEN YU, MEMBER, IEEE, V. LEO RIDEOUT, MEMBER, IEEE, ERNEST BASSOUS, AND ANDRE R. LEBLANC, MEMBER, IEEE

Classic Paper

This paper considers the design, fabrication, and characterization of very small MOSFET switching devices suitable for digital integrated circuits using dimensions of the order of 1 \( \text{\mathbb{I}}\). Scaling relationships are presented which show how a conventional MOSFET can be reduced in size. An improved small device structure is presented that uses ion implantation to provide shallow source and drain regions and a nonuniform substrate doping profile. One-dimensional models are used to predict the substrate doping profile and the corresponding threshold voltage versus source voltage characteristic. A two-dimensional current transport model is used to predict the relative degree of short-channel effects for different device parameter combinations. Polysilicon-gate MOSFET's with channel lengths as short as 0.5 \( \mu\) were fabricated, and the device characteristics measured and compared with predicted values. The performance improvement expected from using these very small devices in highly miniaturized integrated circuits is projected.

A. Marchioro - ISOTDAQ School - 2022

19

19

Oct.

NO. 5,

SC-9,

# Pre-Dennard Scaling ACREAZING ACREAZING PRADIO CORPORATION OF AMERICA RCA LABORATORIES SPECIAL SCIENTIFIC REPORT INVESTIGATIONS OF FUNDAMENTAL LIMITATIONS DETERMINING THE ULTIMATE SIZE OF MICROSTRUCTURES CONTRACT NO A119/60-00-000 FIEDRACIO CONTRACT NO

### Past predictions (1989)

IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 36, NO. 9, SEPTEMBER 1989

# MOSFET Scaling Limits Determined by Subthreshold Conduction

JOSEPH M. PIMBLEY, MEMBER, IEEE, AND JAMES D. MEINDL, FELLOW, IEEE

mation and ultrathin ( < 50 Å) gate insulators. With vanishingly small ( < 50 Å) junction depth, a 30-Å gate oxide dielectric and a channel acceptor concentration of 2  $\times$  10<sup>18</sup> per cubic centimeter, one may achieve acceptably low subthreshold conduction at effective channel lengths down to 0.06  $\mu m$  at an operating temperature of 300 K.

A. Marchioro - ISOTDAQ School - 2022

21

21

## Past predictions (2001)

# **Device Scaling Limits of Si MOSFETs and Their Application Dependencies**

DAVID J. FRANK, MEMBER, IEEE, ROBERT H. DENNARD, FELLOW, IEEE, EDWARD NOWAK, MEMBER, IEEE, PAUL M. SOLOMON, FELLOW, IEEE, YUAN TAUR, FELLOW, IEEE, AND HON-SUM PHILIP WONG, FELLOW, IEEE

The scale length theory that has been presented here provides a useful framework within which to understand the tradeoff between channel length and short channel effects. Using this theory in conjunction with the various limiting effects, we have projected that bulk-like CMOS should be extendible down to about 14-nm nominal channel length for high-performance logic and  $\sim\!\!35$  nm for very low power applications, with intermediate applications falling in between.

A. Marchioro - ISOTDAQ School - 2022

22

PROCEEDINGS OF THE IEEE, VOL. 89, NO. 3, MARCH 2001

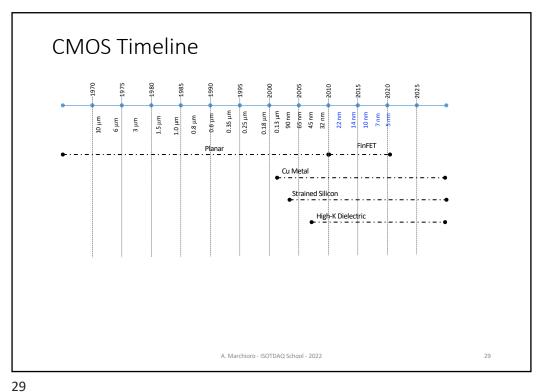

# Brief review of breakthroughs in the last 20 years

- Lithography

- Computational lithography

- Immersion lithography

- EUV

- ٠ ..

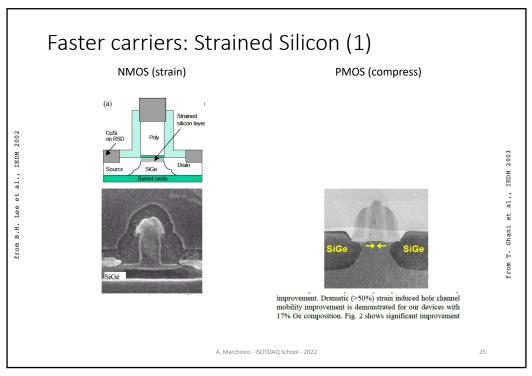

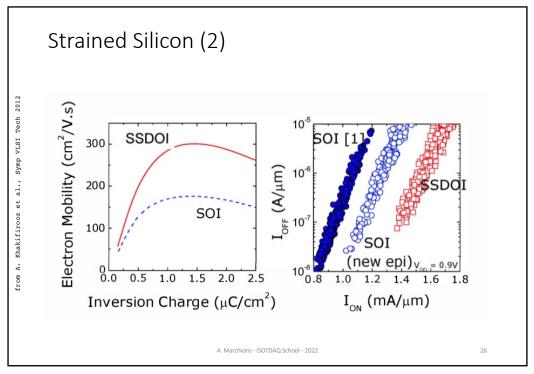

- Strained Silicon

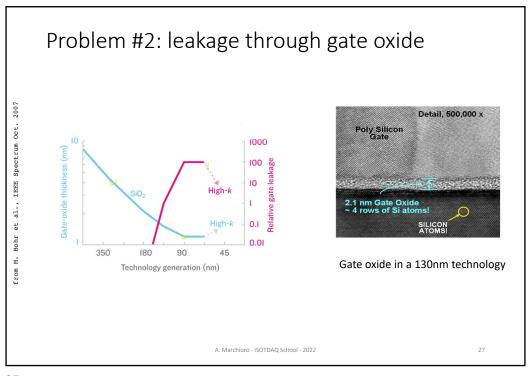

- High-K Metal Gate

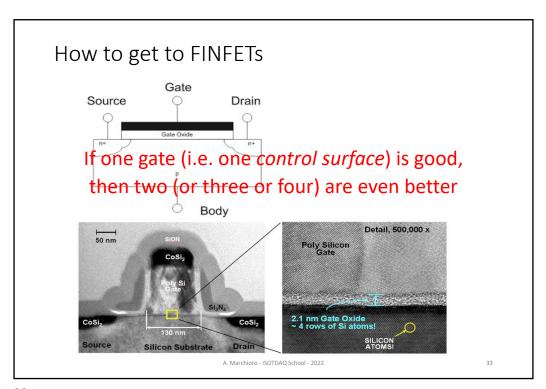

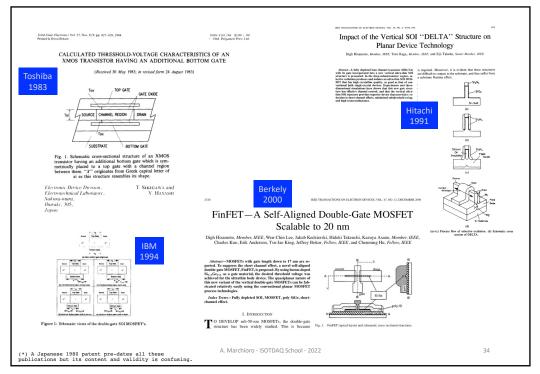

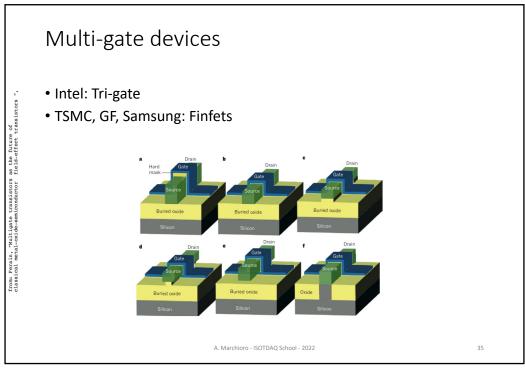

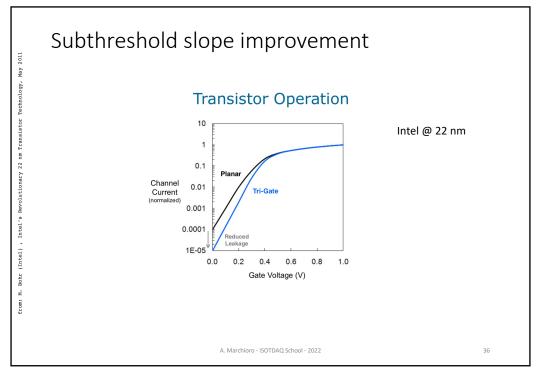

- FinFET

A. Marchioro - ISOTDAQ School - 2022

23

23

# What is actually "wrong" with infinite scaling?

- The 1974 Scaling theory (Dennard et al.) essentially looked at the transistor as a two-dimensional (planar) structure.

- This worked ok up until about 2010

- Classical scaling is only as good as one manages to keep effects in the third dimension ("short channel effects") small, but it fails to describe the behavior of a MOS device when all dimensions are reduced, and doping are increased, and voltages are not reduced (enough).

A. Marchioro - ISOTDAQ School - 2022

30

# Raising from the surface

A. Marchioro - ISOTDAQ School - 2022

31

31

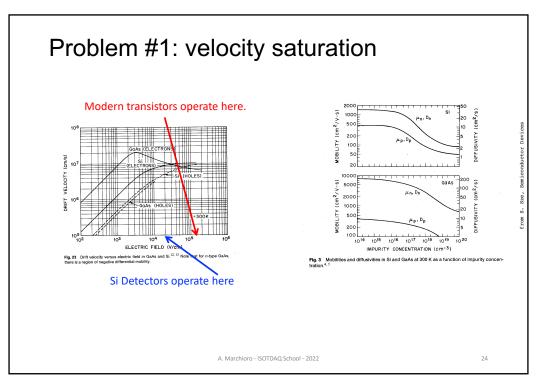

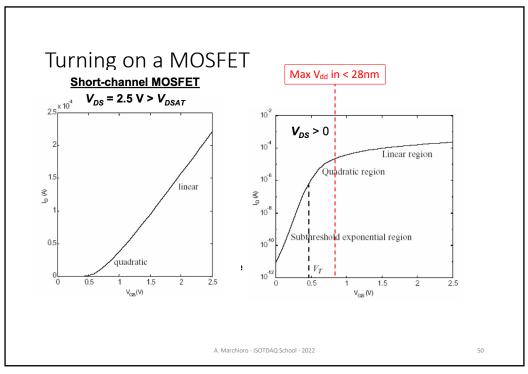

### Short channel effects

- When the channel (L) of a MOSFETS becomes shorter than about .35 um, the following phenomena start appearing:

- Velocity Saturation

- Hot Carrier Degradation

- Drain Induced Barrier Lowering (DIBL)

- V<sub>t</sub> dependence on L

- ...

A. Marchioro - ISOTDAQ School - 2022

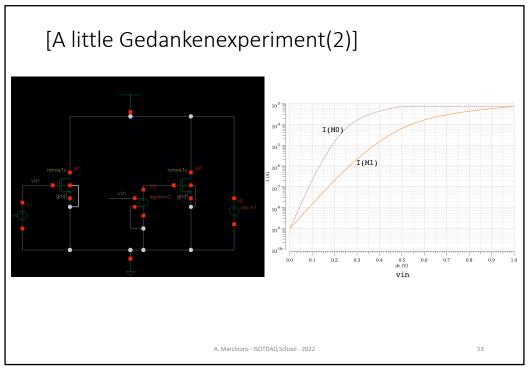

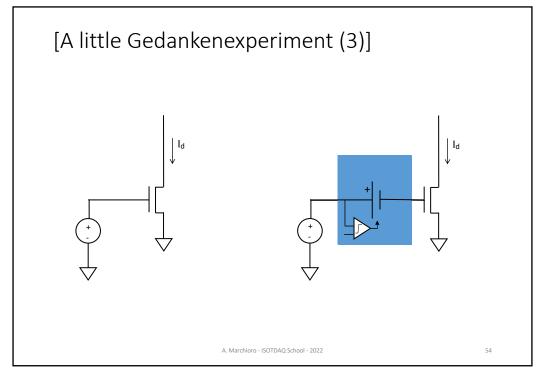

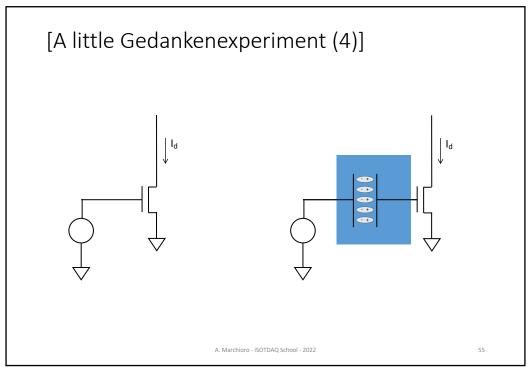

[A little Gedankenexperiment (1)]

A. Marchiero - ISOTDAQ School - 2022

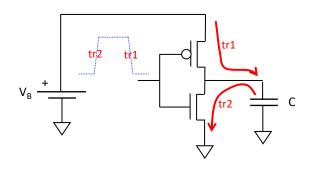

# Adiabatic Logic Circuit

A. Marchioro - ISOTDAQ School - 2022

58

# CMOS Logic: charging and discharging capacitors

A. Marchioro - ISOTDAQ School - 2022

59

59

# Charging a Capacitor

A capacitor charged from a battery has a total charge:

$$Q=C\ *\ V_B$$

• The energy stored on a capacitor C is instead:

$$E_C = \frac{1}{2}C * V_B^2$$

and the energy required to charge it is:

$$E = (C * V_B) * V_B = C * V_B^2$$

A. Marchioro - ISOTDAQ School - 2022

6/17/22

# Charging capacitors with minimal effort

1/2 V<sub>B</sub> + C

$$E_C = \frac{1}{2}C V_B^2$$

$$E_C = \frac{1}{2} C V_B^2$$

$$E_{wasted} = \frac{1}{2}C V_B^2$$

$$E_{wasted} = \frac{1}{2}C\left(\frac{V_B}{2}\right)^2 + \frac{1}{2}C\left(\frac{V_B}{2}\right)^2$$

$$= \frac{1}{4}CV_B^2$$

A. Marchioro - ISOTDAQ School - 2022

61

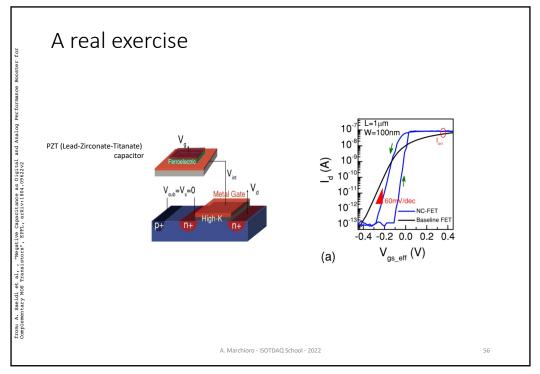

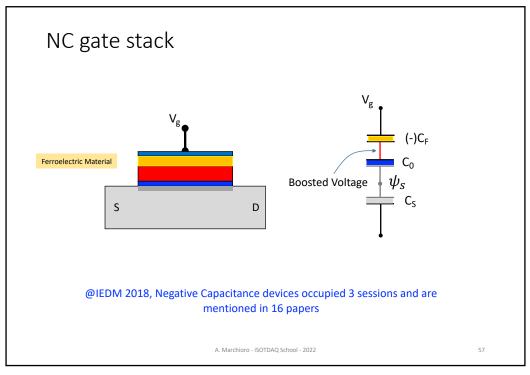

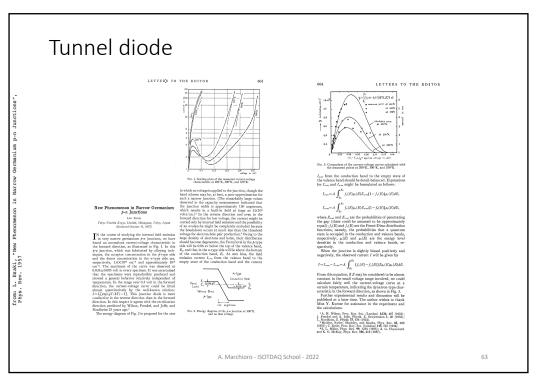

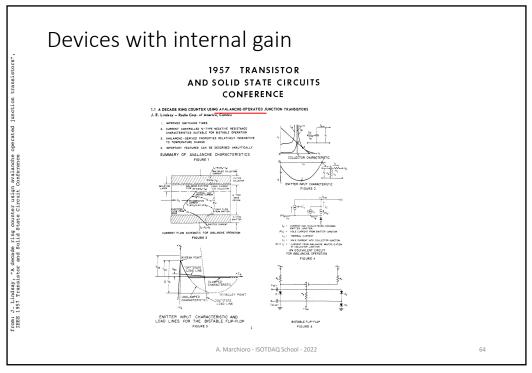

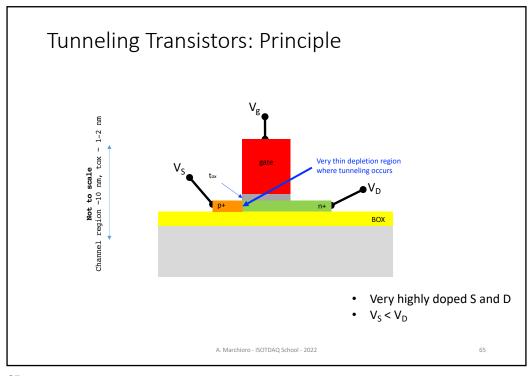

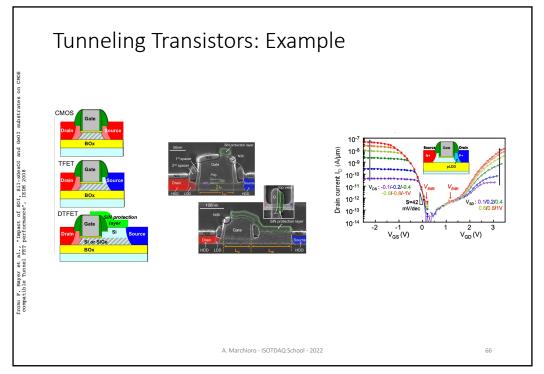

Other non-Boltzmann limited devices

A. Marchioro - ISOTDAQ School - 2022

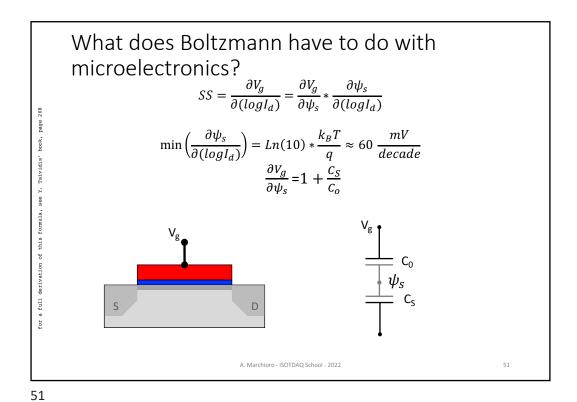

# Summary: low supply voltage devices

- Currently with devices powered between 0.8 and 1.2 V, we use about 400-500 mV (~70-80 mV/dec \* 6 dec) to turn them on.

- If one could reduce reduce the "transition region" to about 50 mV (SS  $\sim$  50/6 = 8-10 mV/dec)

- Then it would be conceivable to have a digital logic supply at 150 mV therefore saving:

```

Power saving: (1.0)^2 / (0.15)^2 = 44 times

```

(i.e. you could recharge your mobile phone less than once per month)

A. Marchioro - ISOTDAQ School - 2022

67

67

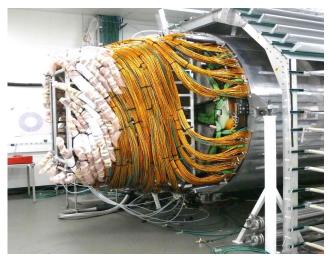

### ... and for the CMS tracker...

... in fact the CMS tracker used 2.5V transistors. If we could use 0.25V transistors the savings in power would be  $(2.5)^2 / (0.25)^2 = 100$  times less cables!!!

A. Marchioro - ISOTDAQ School - 2022

68

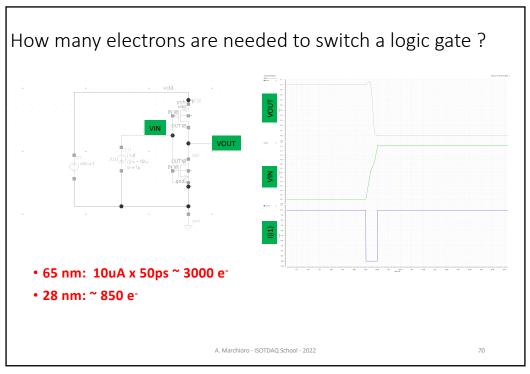

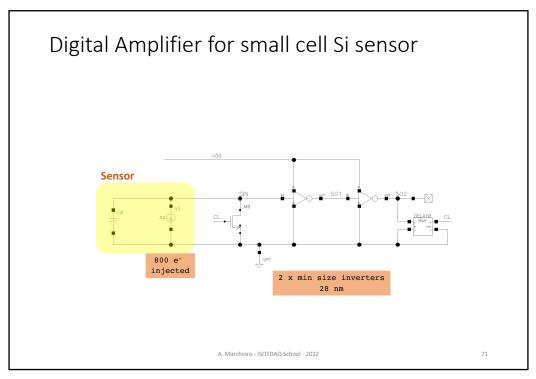

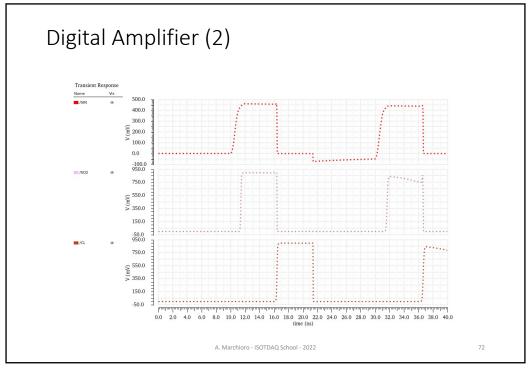

### And what about 5 nm?

- A 5 nm "transistor" switches with < ~100 e- input signal

- That is the signal produced by a MIP particle in about 1um of silicon

Significant issues still exist in the integration of an appropriate sensor with very low parasitic capacitances (intrinsic and extrinsic), but from the point of view of the sensing electronics, it may well be possible to design a pixelized detector with sufficiently small cells to be read out entirely by simple inverters.

A. Marchioro - ISOTDAQ School - 2022

73

73

Conclusions

A. Marchioro - ISOTDAQ School - 2022

## Take home message

- "Brute-force" growth (was called "scaling") is being replaced by "more-sweat" growth

- More sweat also implies more investments, much more investments (especially human)!

- But lots of opportunities are still open for creative designers.

- Much functionality can still be added to instrumentation for physics and other sciences

- The impact of "digital" is still very small in HEP, replace "quantity" of data with "quality" of data

- Beware, gain in analog may even be < 1

- More exotic technologies (TSVs, 3D, wafer stacking, adv. packaging...) but become available also for low-volume, but history teaches that one should bet on mainstream opportunities

- New engineering "structures" may be mandatory to exploit the above!

A. Marchioro - ISOTDAQ School - 2022

75

75

# Thank you

A. Marchioro - ISOTDAQ School - 2022