# Development of a Fast Timing ASIC for Large-area SiPM Array Readout

Mingxin Wang, Weihao Wu

**TRIDENT** Collaboration

Shanghai Jiao Tong University

Real Time Conference 2024, April 22

- Introduction

- Design of the SiPM array readout ASIC

- Status and plans

- Summary

- Introduction

- Design of the SiPM array readout ASIC

- Status and plans

- Summary

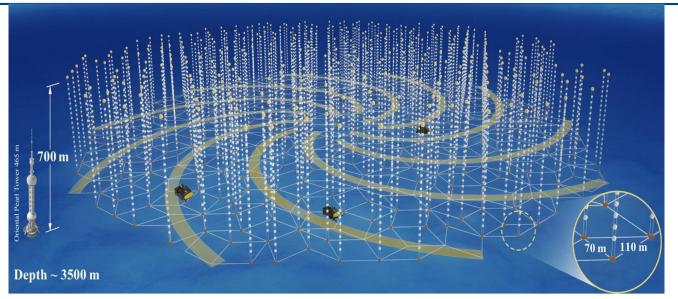

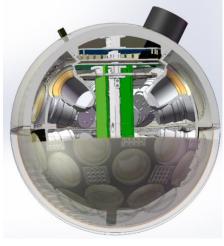

#### **TRopIcal DEep-sea Neutrino Telescope**

TRIDENT: a next-generation multi-cubic-kilometer neutrino

telescope

- ~1200 strings, ~20 DOMs / string

- **TRIDENT pathfinder experiment** was completed in 2021.

- The details of the pathfinder experiment are presented in *Nat. Astro.* 10.1038/s41550-023-02087-6 (2023).

- TRIDENT phase-1 has started since 2022.

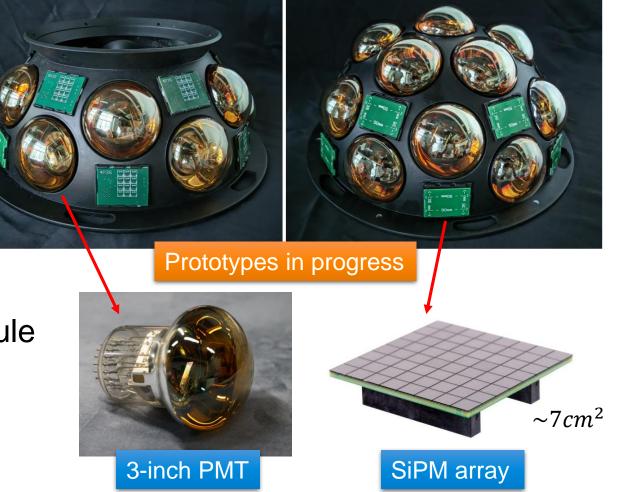

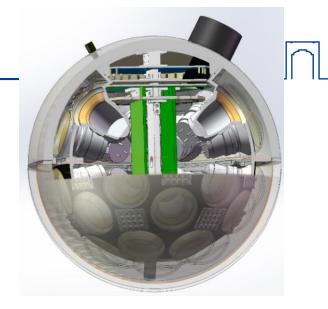

#### **TRIDENT Hybrid Optical Module**

- **hDOM:** hybrid PMT + SiPM optical module

- 31 3-inch PMTs: waveform

- 24 SiPM arrays: hit time

- Large photon collection area + highprecision time resolution

#### Challenges of High-precision Time Measurement for SiPM Arrays

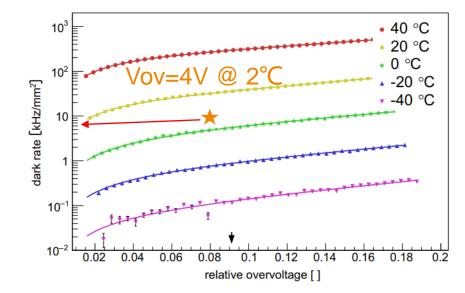

- Dark rate: ~5 kHz /  $mm^2$  @ 2 ~ 4 °C

- Reduced by an order at deep sea

- Trigger scheme with PMTs

- Time walk correction

. . .

- Time-over-Threshold (ToT) method

- Correction with PMT data

Hamamatsu S13360-3050CS

$RelativeOvervoltage = \frac{BiasVoltage - BreakdownVoltage}{BreakdownVoltage}$

$$\sigma_{tot}^2 = \sigma_{jitter}^2 + \sigma_{walk}^2 + \sigma_{digitizer}^2$$

A. N. Otte, et al., NIM A (2017)

#### 7

#### Challenges of High-precision Time Measurement for SiPM Arrays

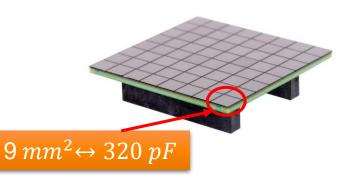

- Trade-off between signal-to-noise ratio and dark rate

- Small number of Cherenkov photons

- Single photon detection sensitivity  $\rightarrow$  limited amplitude

- Large input capacitance (~20 nF)

- Limited bandwidth and rise time

- Limited space and power supply

- Cost of submarine cables

$\sigma_{t} \approx \frac{RiseTime \times NoiseRMS}{Amplitude}$  $\sigma_{tot}^{2} = \sigma_{jitter}^{2} + \sigma_{walk}^{2} + \sigma_{digitizer}^{2}$

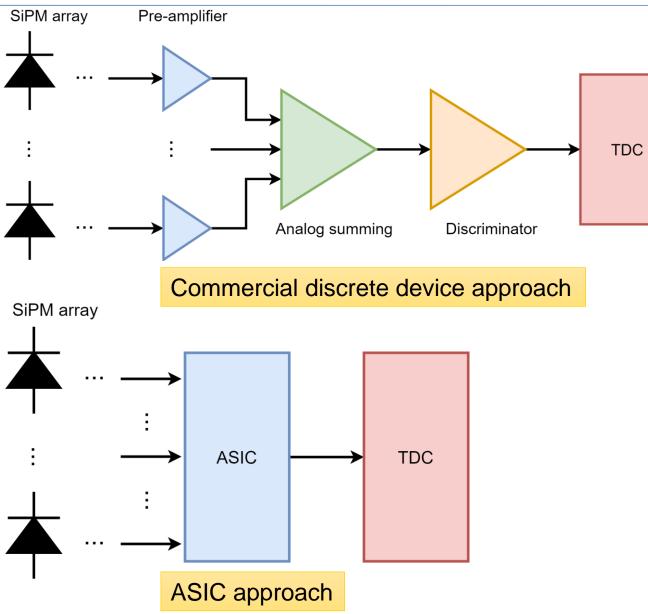

#### **SiPM Array Readout Scheme**

- The commercial discrete device approach is detailed in *arXiv:2403.02948.*

- The single photon time resolution (SPTR) of a 4 × 4 SiPM (Hamamatsu S13360-3050PE) array (12 × 12 mm<sup>2</sup>) is ~300 ps full width at half maximum (FWHM) with a power consumption of ~100 mW.

- Compared to the discrete device approach, this ASIC has the advantages of higher integration and lower power consumption.

#### Introduction

- Design of the SiPM array readout ASIC

- Status and plans

- Summary

#### **Requirements for the ASIC**

- SPTR < 300 ps FWHM

- Input channel number: 16

- Number of wires connected to the FPGA: as few as possible

- Limited space and number of IOs

- Power consumption: < 10 mW/channel

#### **Some SiPM Readout ASICs**

| ASIC      | SPTR in ps FWHM  | Power in<br>mW/ch | Input conditions         |

|-----------|------------------|-------------------|--------------------------|

| NINO      | 160              | 27                | S13360-3050CS, Vov=10V   |

| HRFlexToT | 263              | 3.5               | S13360-3050CS, Vov=4V    |

| FlexToT   | 390              | 11                | S13360-3050CS, Vov=4V    |

| PETIROC2A | 190              | 6                 | S13360-3050CS, Vov=7V    |

| STiC3     | 150              | 25                | S13360-1350CS            |

| TOFPET2   | 306              | 8.2               | S13361-3050AE-04, Vov=4V |

| DIET      | ~94 (3 PE input) | 3.3               | ARRAYJ-30020-64P, Vov=5V |

- These ASICs are not fully applicable to deep-water neutrino telescope experiments.

- High power consumption: NINO, etc.

- Readout dead time: PETIROC2A, TOFPET2, etc.

- Insufficient timing performance: FlexToT, etc.

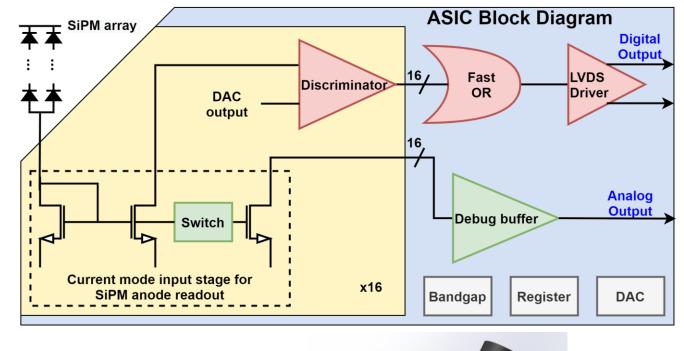

#### **ASIC Concept**

- Each input channel is connected to a small SiPM array (e.g. 2p4s).

- SiPM HV tuning

- Core modules are optimized for fast timing.

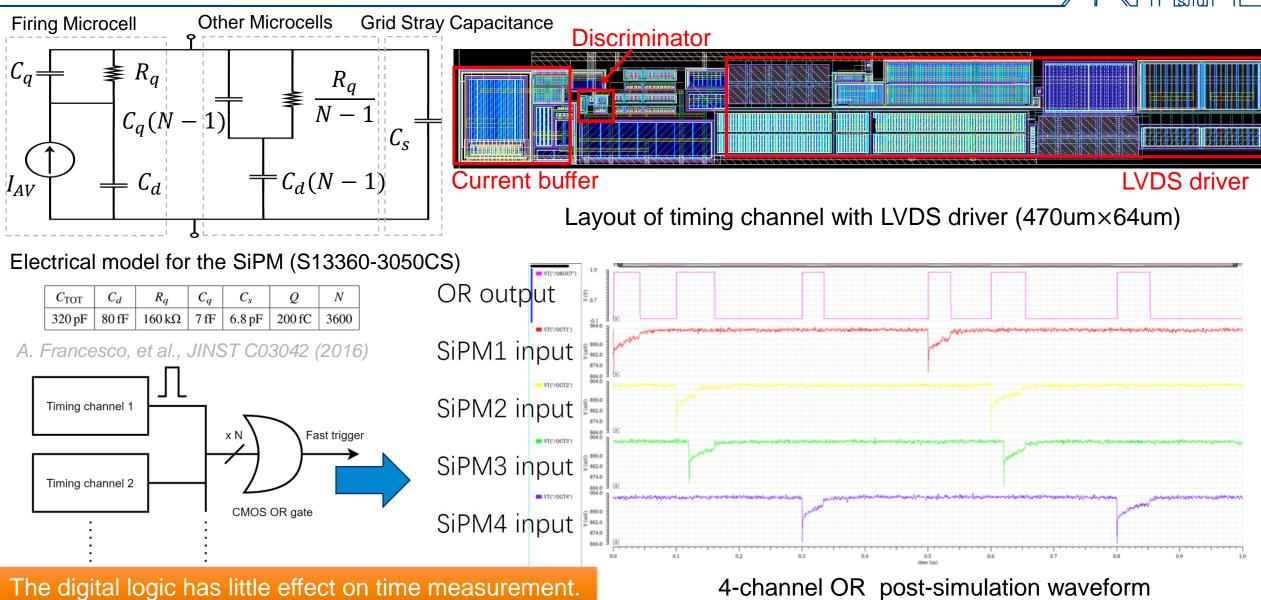

- Summing: one OR gate combines discriminator outputs.

- Reduced readout channel number

- CMOS 180 nm technology, VDD = 1.8 V

- This presentation focuses on prototyping and comparing different schemes.

- Input stage, discriminator, etc.

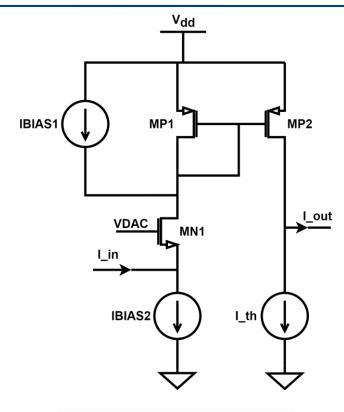

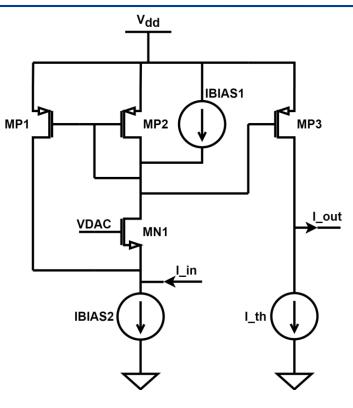

#### **Core Module – Input Stage**

Common gate stage

Negative feedback common gate stage

- 2 current buffer architectures are designed.

- CG has better time performance.

- NFBCG has lower input resistance.

- Alleviate the pile-up effect

- VDAC SiPM bias voltage tuning

- Power consumption: ~3 mW

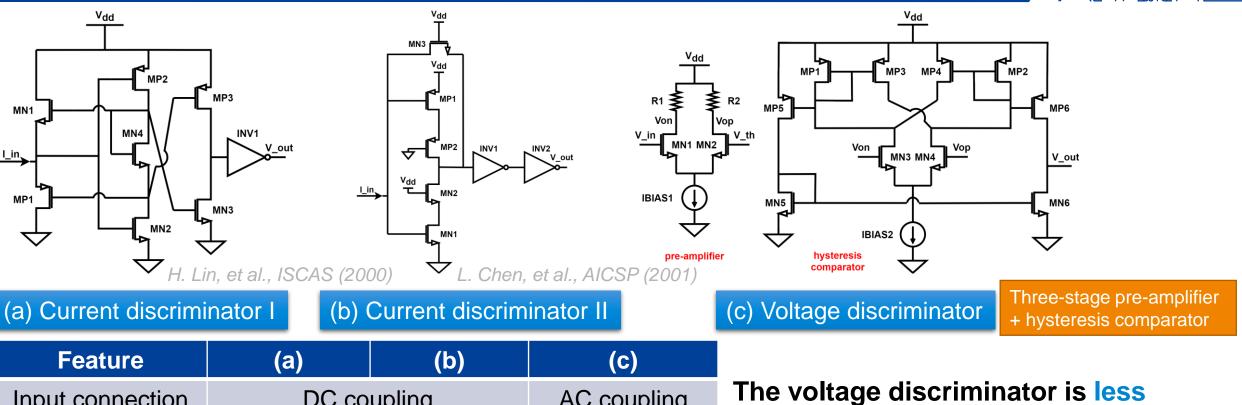

#### **Core Module – Discriminator**

MN1

MP1

l\_in

AC coupling DC coupling Input connection 1.9 ns Propagation delay 0.56 ns 0.47 ns Static power 0.6 mW 0.4 mW 3.1 mW consumption  $187 \ um^2$  $336 \ um^2$  $6000 \ um^2$ Area Pre-simulation results @ 27°C, TT corner, Vdd=1.8V

affected by process-voltagetemperature variations but has higher area and power consumption.

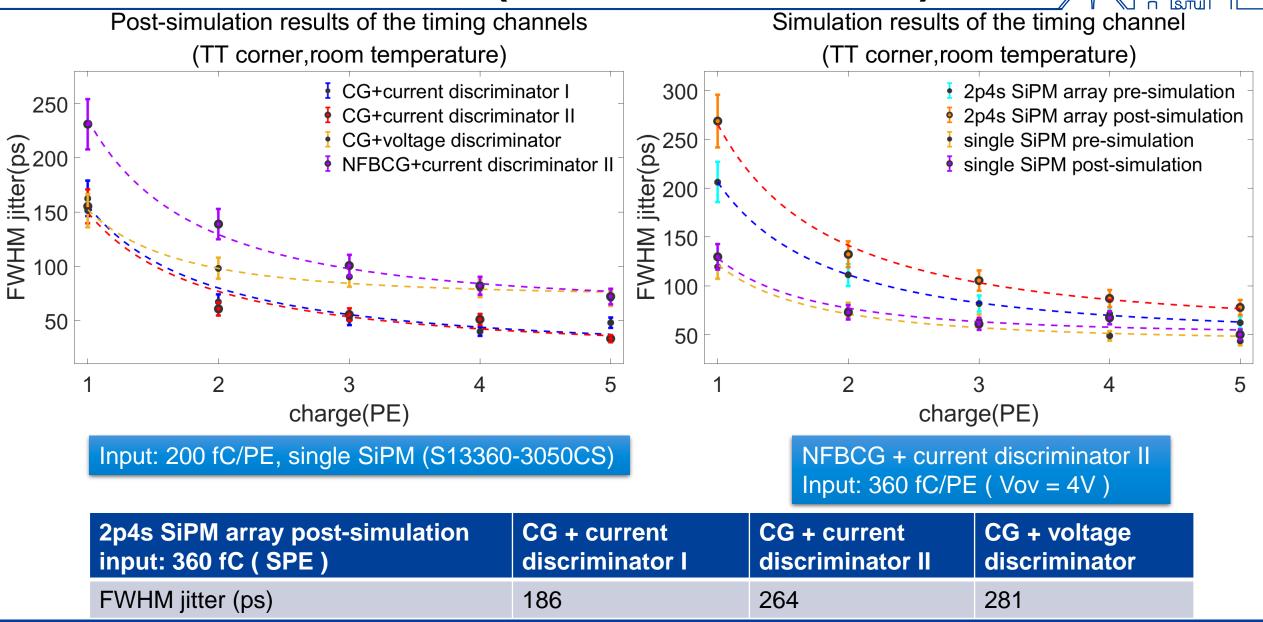

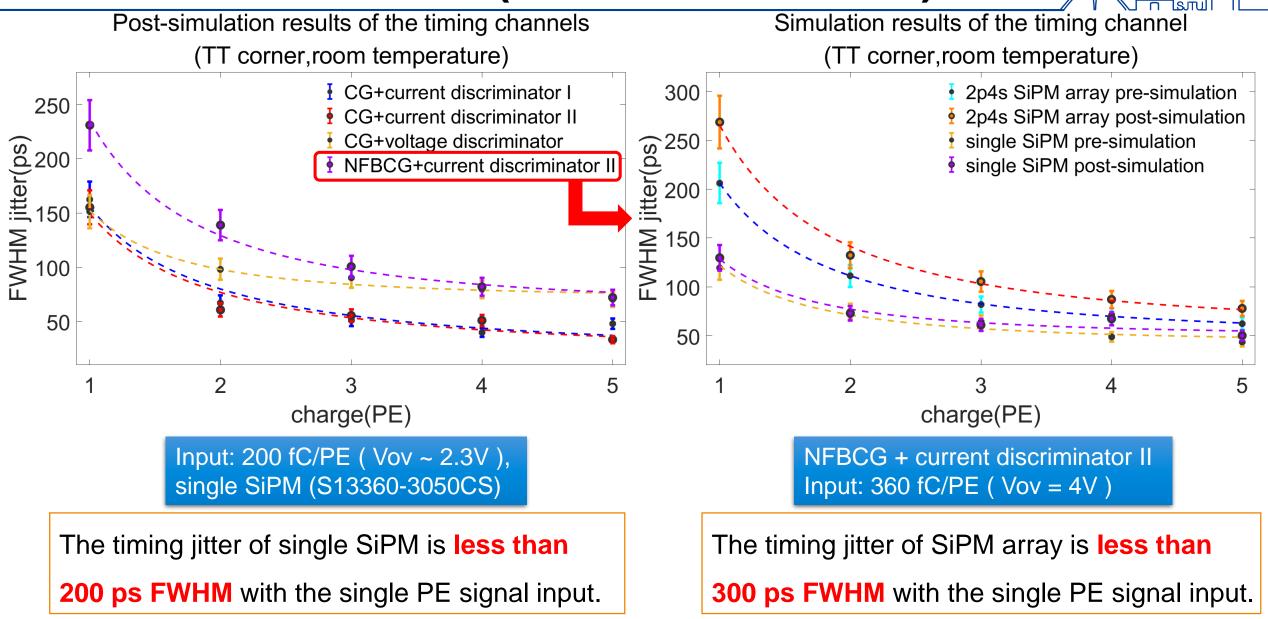

#### **ASIC Performance (simulation results)**

#### **ASIC Performance (simulation results)**

- Introduction

- Design of the SiPM array readout ASIC

- Status and plans

- Summary

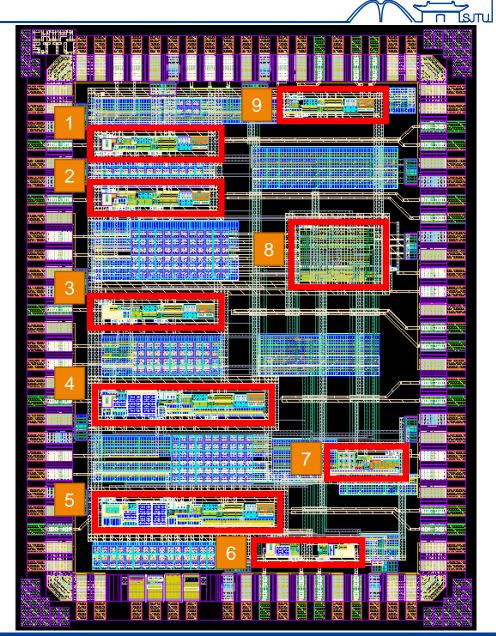

### Chip 1 Layout

- Chip 1 has 84 pins,  $1.92 \times 2.56 mm^2$

- (1) CG + current discriminator I + LVDS driver

- (2) CG + current discriminator II + LVDS driver

- (3) NFBCG + current discriminator II + LVDS driver

- (4) CG + voltage discriminator + LVDS driver

- (5) CG (ESD modified version) + voltage discriminator + LVDS driver

- (6) Input stages + debug buffer

- (7) Bandgap

- (8) Bias

- (9) Standalone LVDS driver

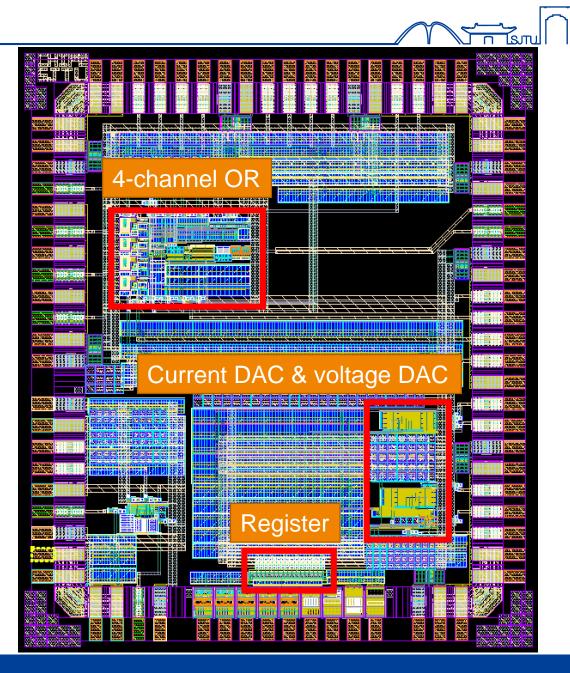

#### Chip 2 Layout

- Chip 2 has 72 pins,  $1.84 \times 2.16 mm^2$

- 4 timing channels + fast OR + LVDS driver

- 8-bit current DAC

- 8-bit voltage DAC

- Registers related to DAC configuration

- 2 ASICs for prototype verification have been designed and will be fabricated in May, 2024.

- Introduction

- Design of the SiPM array readout ASIC

- Status and plans

- Summary

#### Summary

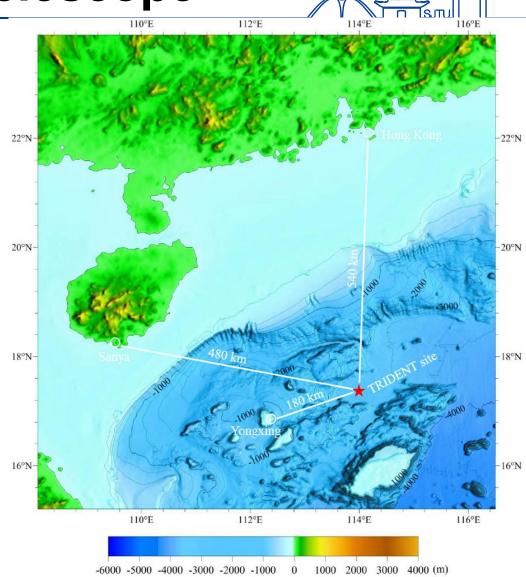

- TRIDENT is a next-generation neutrino telescope planned to be constructed in the South China Sea.

- A fast timing ASIC for SiPM array readout is under development.

- The first version of the prototype ASIC has been designed and will be fabricated in May, 2024.

- Post-simulations show that the timing jitter is less than 200 ps FWHM

@ Single PE input, with power consumption < 10 mW/channel.

## Backup

#### **ASIC Performance (simulation results)**