# Study of single-slope ADC using FPGA TDC for streaming readout data acquisition

T.N. Takahashi, S. Ajimura, Y. Igarashi<sup>A</sup>, S. Ota, N. Kobayashi, R. Honda<sup>A</sup>, S.Y. Ryu

RCNP, Osaka University  $^A$  KEK IPNS

Outline

- Introduction

- Motivation

- Single-slope ADC

- Ongoing studies

- Summary

## Introduction

24th IEEE Real Time Conference, ICISE, Quy Nhon, Vietnam, 22-26, April, 2024 **2/15**

- Software

- NestDAQ (talk by Igarashi)

- Frontend electronics

- TDC module : AMANEQ, clock sync. : MIKUMARI and LACCP (talk by Honda)

- Application

- J-PARC, Grand Raiden in RCNP (talk by Igarashi, and Ota)

- Standardization

- SPADI-Alliance (talk by Ota)

## Motivation : To extend applicable field of streaming DAQ

## What we have already achieved : free-streaming TDC

- Hit arrival time

- Charge measurement using Time-over-Threshold (ToT)

- Still issues: pulse pile up, linearity

## Charge measurement without dead time ⇒ challenging!

- High-speed waveform digitizers

- Commercially available but expensive

## Single-slope ADC (SS-ADC) as a cost-effective circuit

24th IEEE Real Time Conference, ICISE, Quy Nhon, Vietnam, 22-26, April, 2024

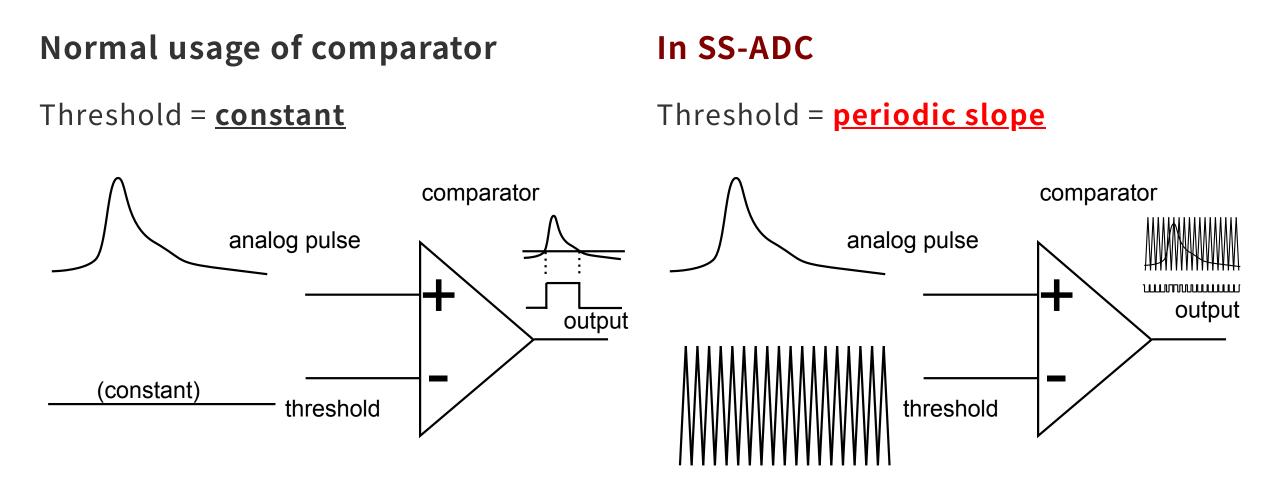

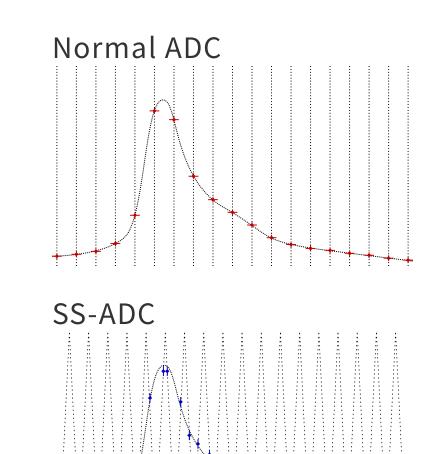

## SS-ADC : Principle (1) 1-bit A/D conversion with comparator

Measure the time of level-crossing points with HR-TDC

24th IEEE Real Time Conference, ICISE, Quy Nhon, Vietnam, 22-26, April, 2024

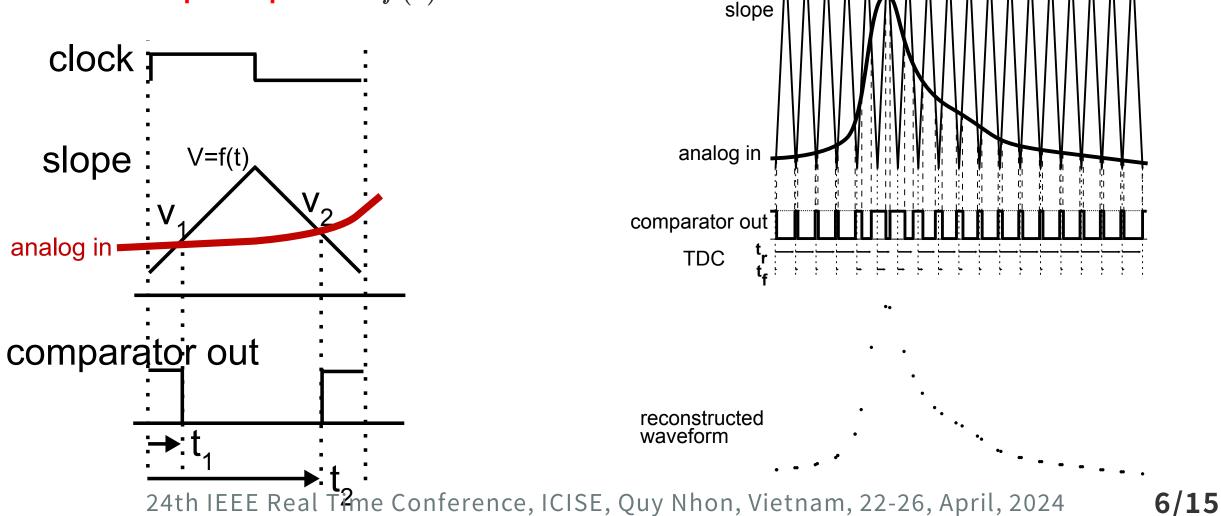

## SS-ADC : Principle (2) Waveform reconstruction

- Slope and HR-TDC clock  $\Rightarrow$  synchronized

- Known slope shape: V = f(t)

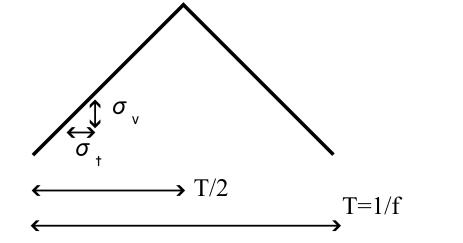

## SS-ADC: Rough estimation of performance

- $\sigma_t$  : TDC resolution

- f, T : slope repetition rate, period

- N bits : ADC resolution

$$egin{array}{ll} \circ \ rac{T}{2} = rac{1}{2f} = 2^N \cdot \sigma_t, & rac{\sigma_V}{\sigma_t} \sim rac{dV}{dt} \ \circ \ N = \log_2 rac{T}{2\sigma_t} \end{array}$$

Example :  $\sigma_t$  = 10 ps, f = 500 MHz (= 1 Gsps)  $\Rightarrow N = \log_2 100 = 6.6$

> ref. 600 Msps, 7-ENOB L. Leuenberger *et al*, <u>doi:10.1145/3431920.3439287</u>

In a real environment, SS-ADC performance would be affected by noise, jitter, slope shape, stability, ...

## **SS-ADC : Pros and Cons**

#### Pros

- Fast waveform sampling (100 MSps 1 Gsps)

- Fewer external components

- Compact, low-cost

- $\circ$  COTS

## Cons

- ADC resolution (single measurement): Low to moderate

- Trade-off: resolution ⇔ sampling rate

- Unevenly-sampled signal

## Purpose of this study

## **Performance evaluation of SS-ADC**

- ADC linearity, voltage range

- Time resolution, charge resolution, sampling rate

- Effect of noise, signal shape

- Effect of slope shape

- Triangle, sinusoidal, exponential decay

- How to extract time and charge information

- Averaging, interpolation, waveform fitting, AI, ...

- Scope of application, applicable detectors

Simulation study and FPGA firmware development 24th IEEE Real Time Conference, ICISE, Quy Nhon, Vietnam, 22-26, April, 2024

# **Ongoing studies**

24th IEEE Real Time Conference, ICISE, Quy Nhon, Vietnam, 22-26, April, 2024 **10/15**

## Studies with hardware

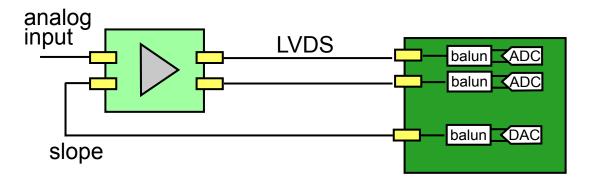

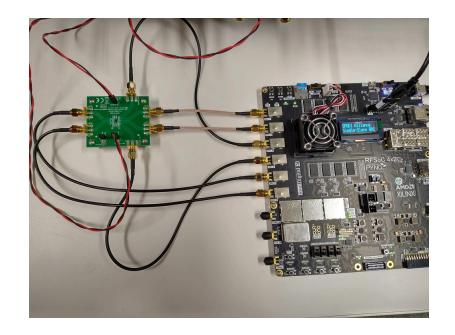

- Performance evaluation of SS-ADC independent of <a href="https://www.secarity.com">https://www.secarity.com</a> here

FPGA-TDC implementation

- Commercial comparator board + high-speed DAC and ADC

- Evaluation of SS-ADC with FPGA-TDC (a few channels)

- Evaluation of SS-ADC with FPGA-TDC (multi-channel board)

## SS-ADC performance evaluation without FPGA-TDC

comparator Evaluation Board

RFSoC 4x2

ADC, DAC:

- AC coupled

- balun : 10 MHz 10 GHz

RFSoC4x2 (Real Digital)

- DAC (14 bit, max. 9.85 Gsps)

Arbitrary slope shape

- Analog pulse emulation

- ADC (12 bit, max. 5 Gsps)

- Record LVDS waveform at comparator output

- Analyze LVDS waveform

HR-TDC emulation

## Test bed using RFSoC4x2 and comparator eval. board

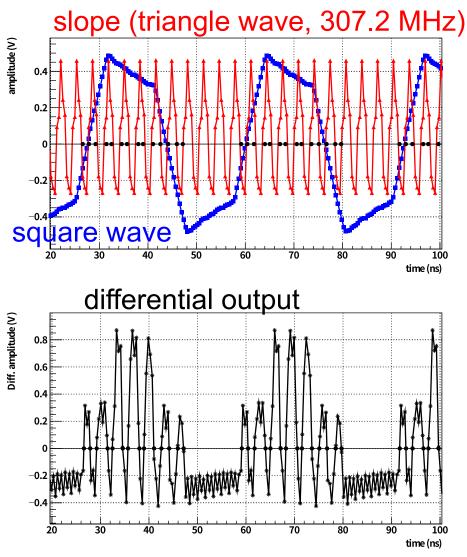

- Firmware : modified from RFSoC-PYNQ

- DAC: 4.9152 Gsps

- Triangle wave 307.2 MHz as a slope

- Square wave as a pulse to be measured

- ADC: 2.4576 Gsps

- Comparator input (+, -)

- LVDS out (+, -)

## Comparator : TLV3801 (TI)

- Max input 3 GHz

- low cost : a few \$/chip

24th IEEE Real Time Conference, ICISE, Quy Nhon, Vietnam, 22-26, April, 2024 **13/15**

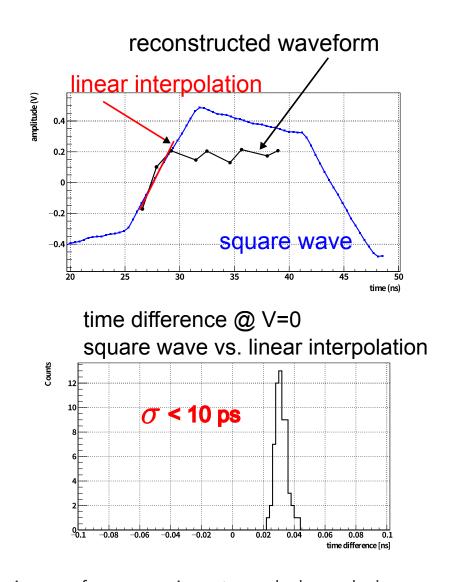

## Timing performance test

The timing performance is not much degraded. 24th IEEE Real Time Conference, ICISE, Quy Nhon, Vietnam, 22-26, April, 2024

## Summary

#### Single-slope ADC

- Periodic slope + comparator + HR-TDC

- Waveform digitizer with moderate performance

- Sampling rate : 100 Msps 1 Gsps, ADC resolution : 5 8 bit

- Need to process unevenly-sampled data points if we want to get the best performance

#### **Ongoing studies**

- Evaluation with comparator board and RFSoC

- Independent of HR-TDC implementation

- $\circ$  Input range depends on amplitude of the slope. (typ. V<sub>pp</sub> = 0.5-0.7 V in this study)

#### **Future work**

- PCB design, implementation of FPGA-TDC

- Data processing method

24th IEEE Real Time Conference, ICISE, Quy Nhon, Vietnam, 22-26, April, 2024 15/15