Michael Goodrich<sup>\*</sup>, Vardan Gyurjyan<sup>\*</sup>, Graham Heyes<sup>\*</sup>, Derek Howard<sup>+</sup>, Yatish Kumar<sup>+</sup>, David Lawrence<sup>\*</sup>, Brad Sawatzky<sup>\*</sup>, Stacey Sheldon<sup>+</sup>, Carl Timmer<sup>\*</sup>

# Where Are We Now?

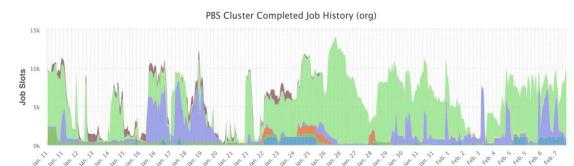

#### Online:

- Counting House: Custom Electronics, Multi-Level Triggers, Pipelined Readout Systems Build Events Online and Store for Offline Analysis

- Designed To Be Inherently "Stable"

- Stability Often Comes At An Efficiency Cost As The trade Off for Reliable/Acceptable Performance

#### Offline:

FPSC

- Events Processed In Steps: Monitoring, Calibration, Decoding, Reconstruction, Analysis.

- Data Passed Between Stages In Flat Files.

- Pauses Of Days/Weeks/Months Between Steps.

- Minimal Automation Between Steps.

- Analyze with Homogeneous Batch Farms.

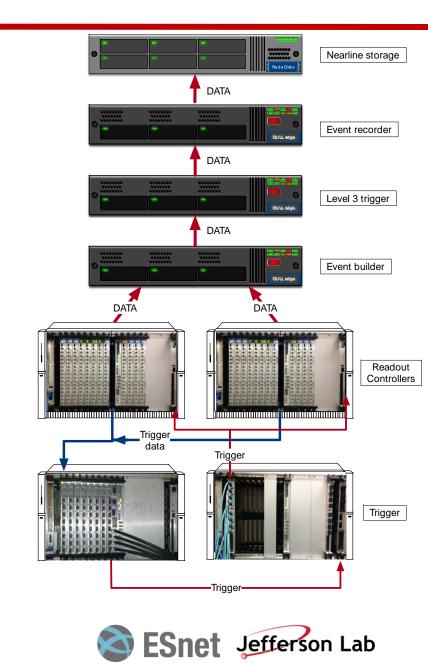

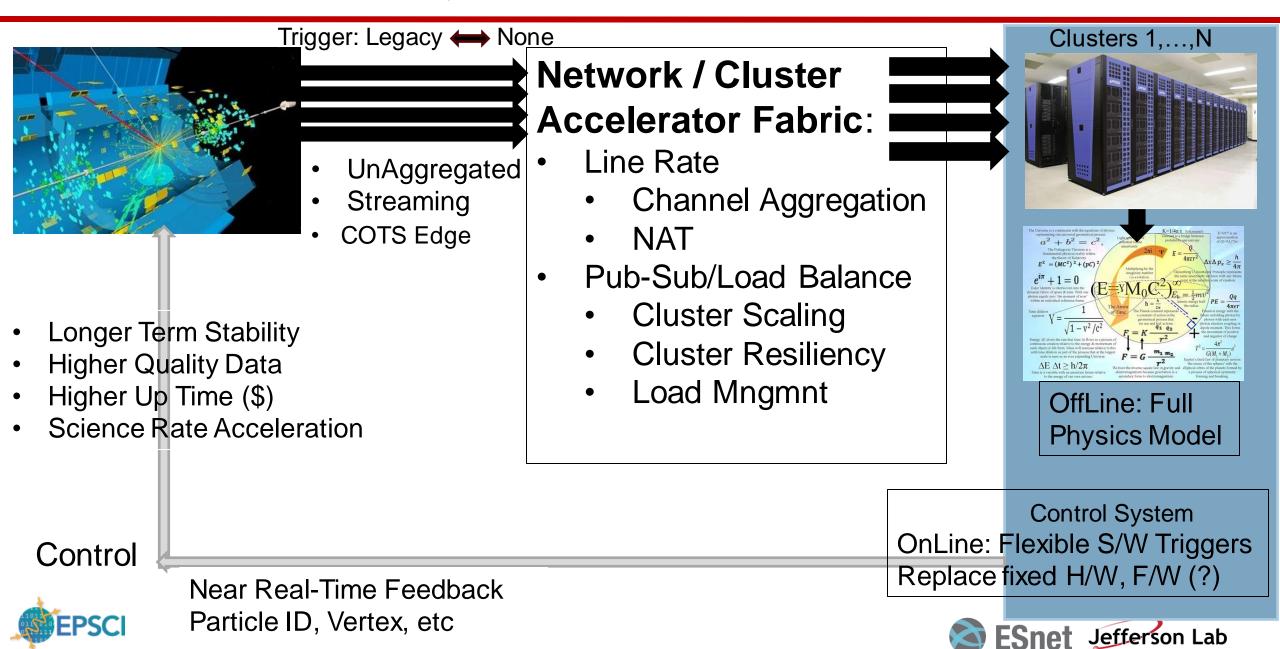

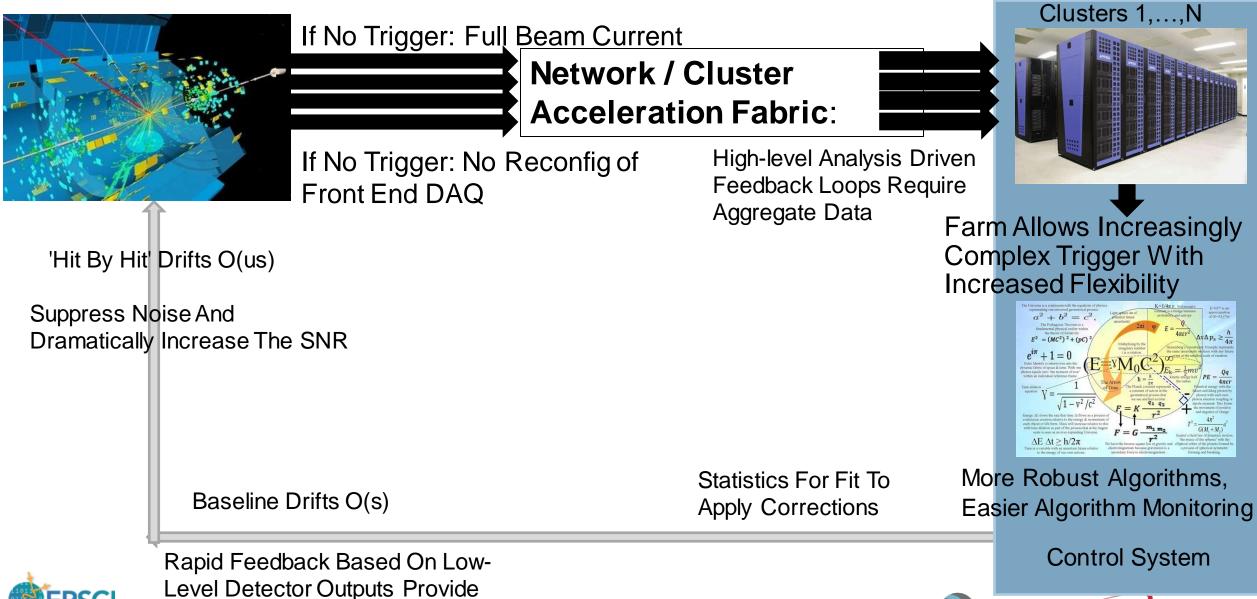

## EJFAT: Network-Cluster Acceleration Fabric

#### Full Streaming Readout Greater Stability, Cluster Resilience/Scaling

#### Better Detector Feedback Greater Stability, Better Data

ESnet Jefferson Lab

EPSC

Level Detector Outputs Provide Rapid Baseline Corrections O(ms)

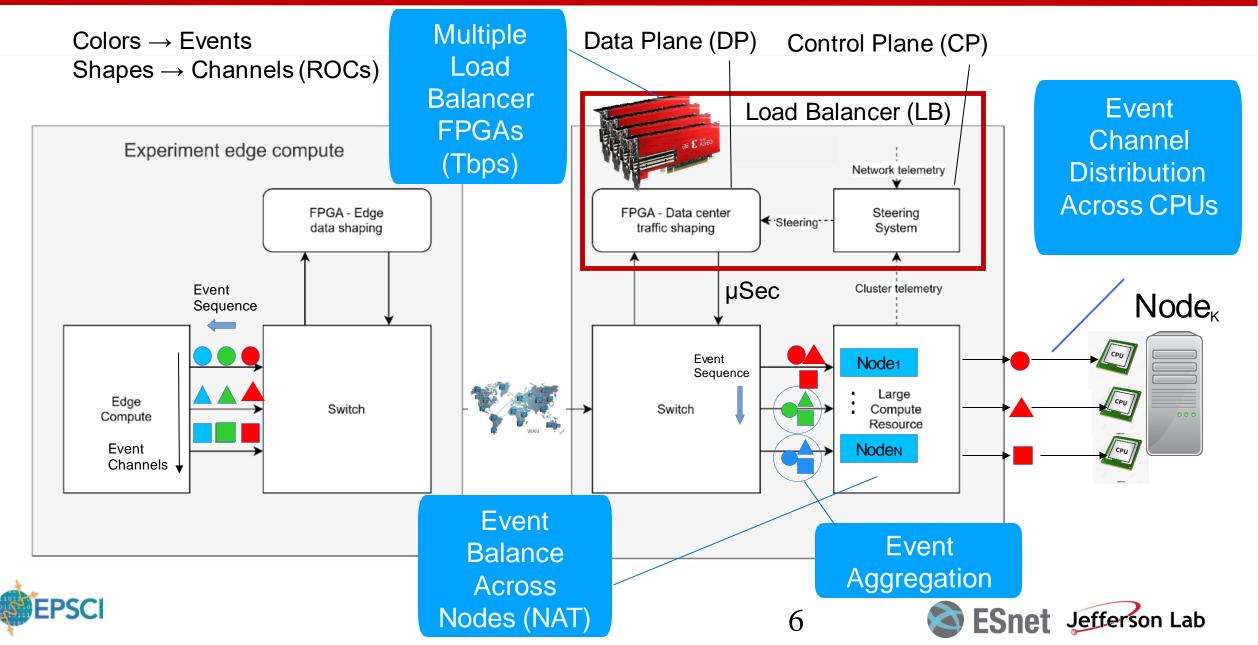

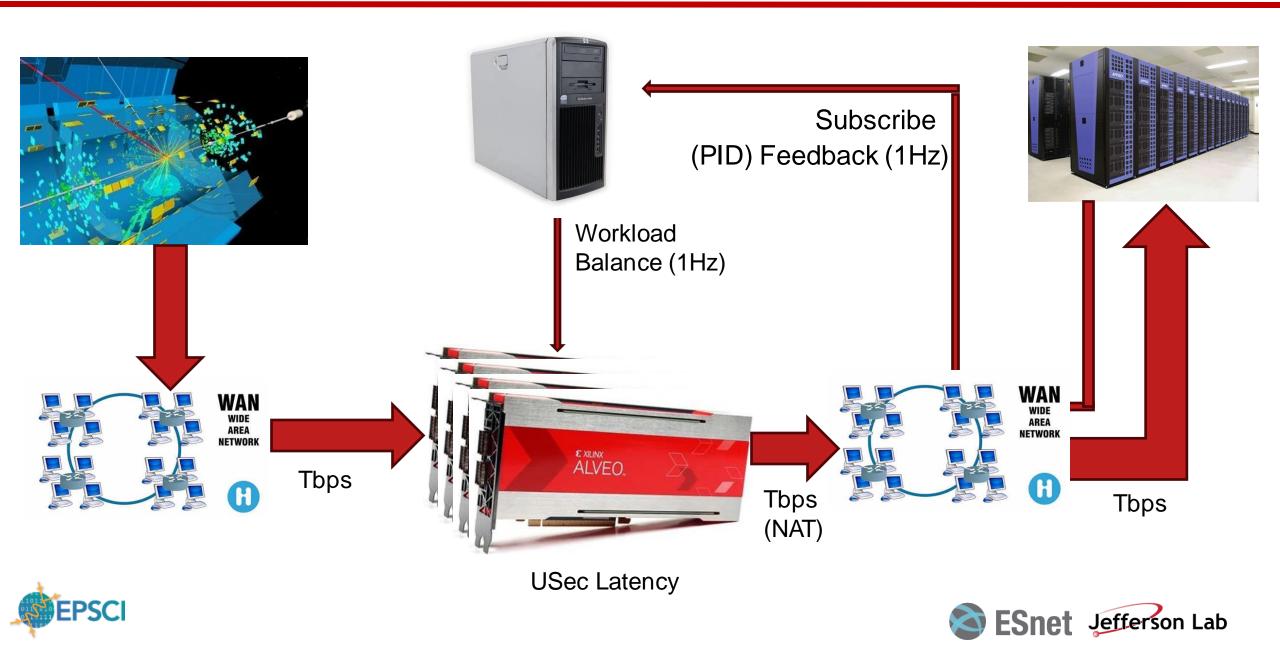

### **EJFAT LB: Horizontal Scaling**

# EJFAT LB FPGA Data Plane (DP)

Network Device:

- Ping

- ARP

- Line Rate NAT

- Some ICMP

- RTL/P4

- Supports Four Virtual DP Pipelines / Separate Experiments

- NAT Look Up Tables Configured by Control Plane

- Node Network Coordinates

- Event to Node Dynamic Balancing (1Hz)

- Destination Ports for Channels

# EJFAT LB Control Plane (CP)

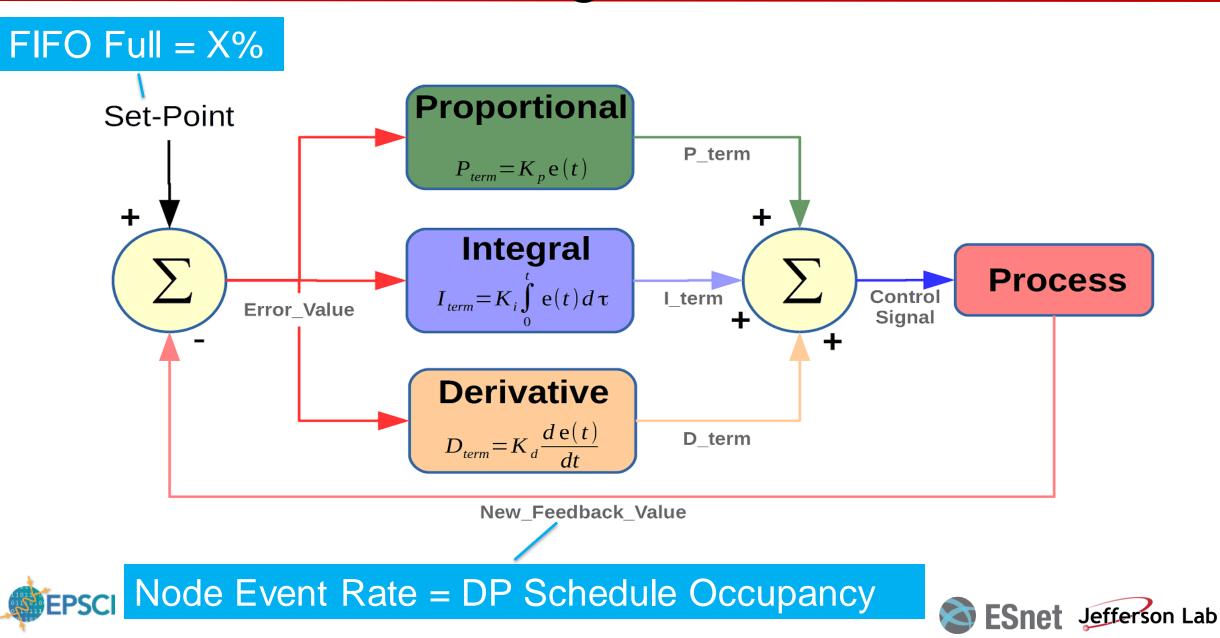

# CP Load Balancing: PID Control

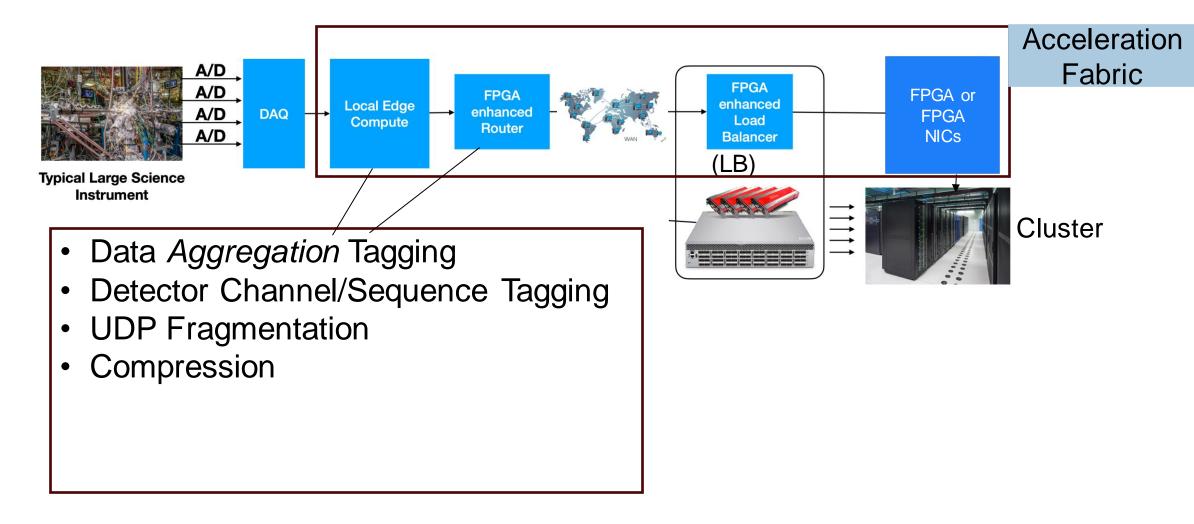

## EJFAT: Data Producer Acceleration

ESnet Jefferson Lab

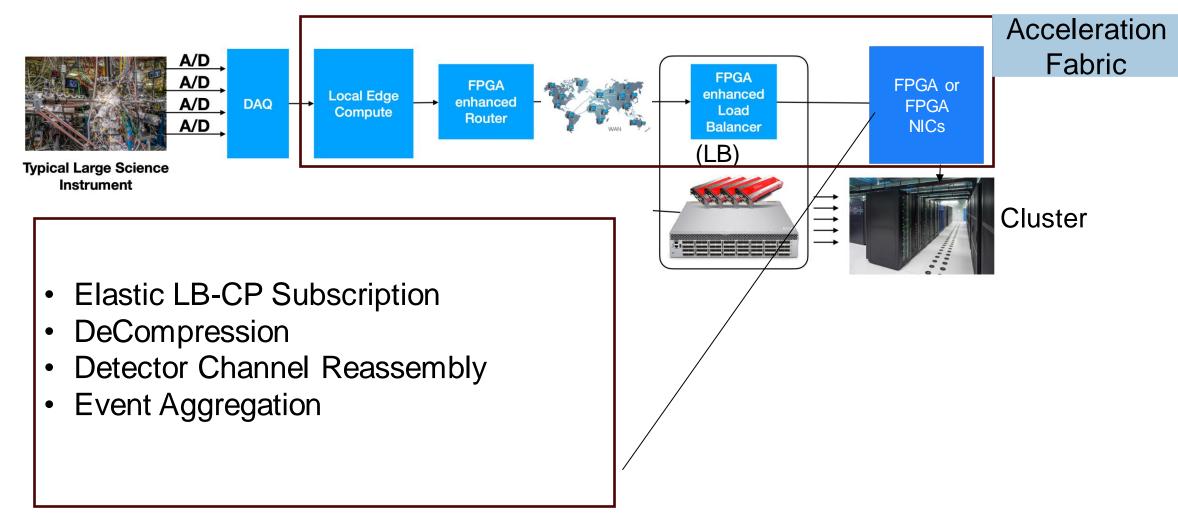

# **EJFAT: Data Consumer Acceleration**

11

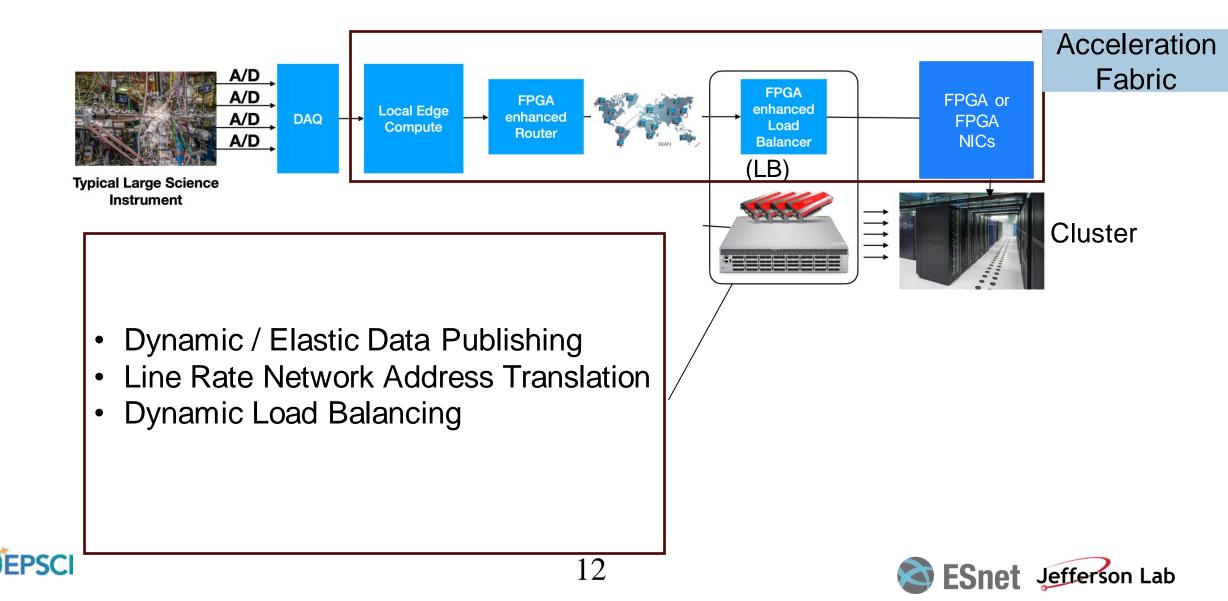

## **EJFAT: LB Acceleration**

## Status / Future

- EJFAT LB Data Plane, Control Plane Developed and Deployed

- Alpha Testing:

- Jlab Based Data Fabric Research Efforts, LDRDs

- Jlab Data Source, ESnet based EJFAT LB, LBNL based Cluster (Perlmutter)

- Jlab Data Source, ESnet based EJFAT LB, ORNL based Cluster (soon)

- Beta Testing:

- Advanced Light Source (ALS) / LBNL (summer 2024)

### ESnet-JLab FPGA Accelerated Transport (EJFAT)

# Questions?