24th IEEE Real Time Conference ICISE, Quy Nhon, Vietnam Apr 22 – 26, 2024

# Cross-Chip Partial Reconfiguration for the Initialisation of Heterogeneous Systems

Marvin Fuchs, Hendrik Krause, Timo Muscheid, Lukas Scheller, Luis E. Ardila-Perez, and Oliver Sander

#### **Definition for this talk:**

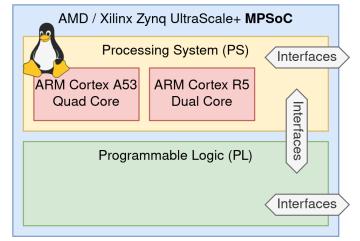

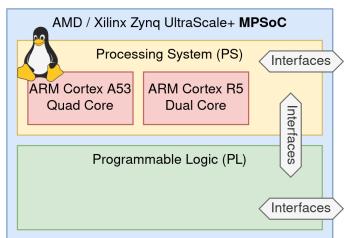

- System composed of various devices from AMD / Xilinx

- MPSoCs

- RFSoCs

- FPGAs

Multiple such heterogeneous systems developed at CERN:

Heterogeneous device

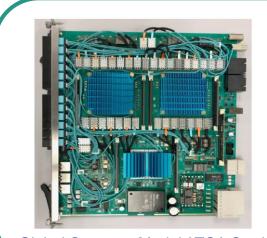

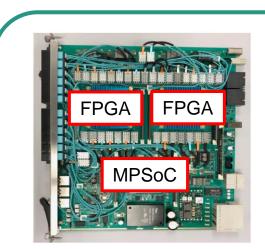

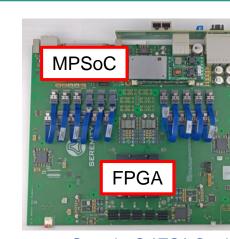

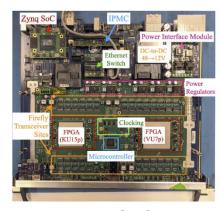

Serenity S ATCA Card

#### **Definition for this talk:**

- System composed of various devices from AMD / Xilinx

- MPSoCs

- RFSoCs

- FPGAs

Multiple such heterogeneous systems developed at CERN:

**MPSoC**

Heterogeneous device

Serenity S ATCA Card

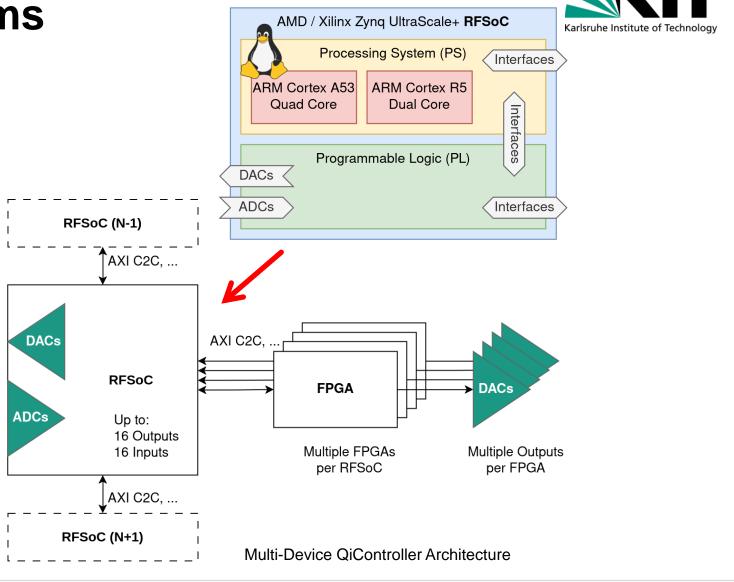

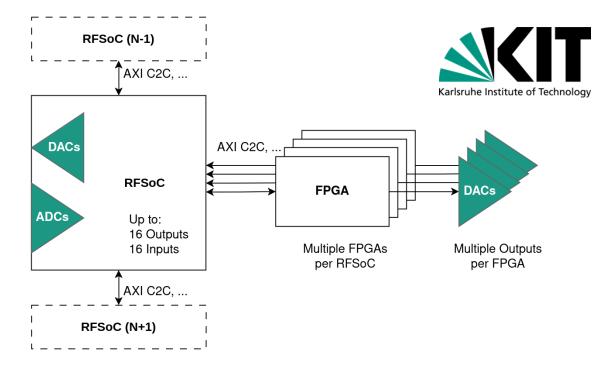

#### **QiController:**

- RFSoC based Qubit control system

- Modular PL firmware

#### Next step:

- Scaling to control more Qubits

- → Heterogeneous system

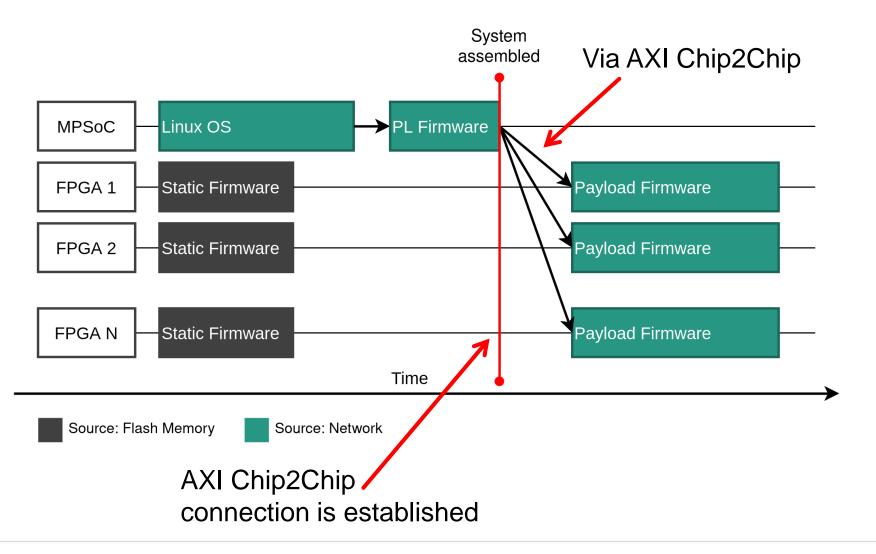

# Initialisation of Heterogeneous Systems

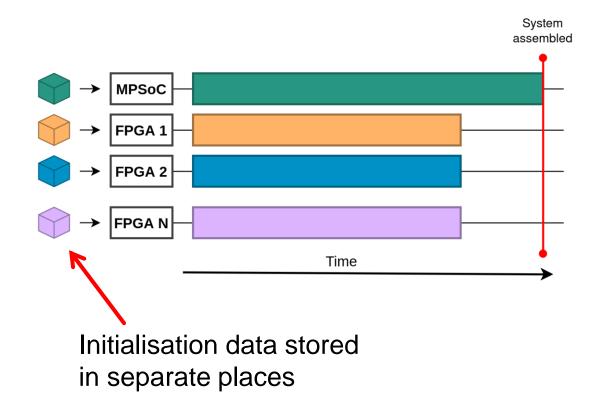

#### **Conventional Approach:**

- Independent initialisation of devices

- Assembly to overall system in late boot stage

#### **Drawbacks:**

- Hard to manage

- Hard to update

# **Initialisation of Heterogeneous Systems**

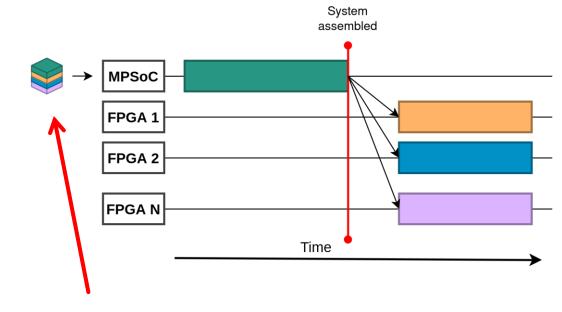

#### **Proposed Approach:**

- Early formation of overall system

- Boot as one system

#### Advantages:

- System manageable by MPSoC / RFSoC

- Centrally controlled updates

- Scalable approach

### **But how to implement?**

All initialisation data stored in the same place

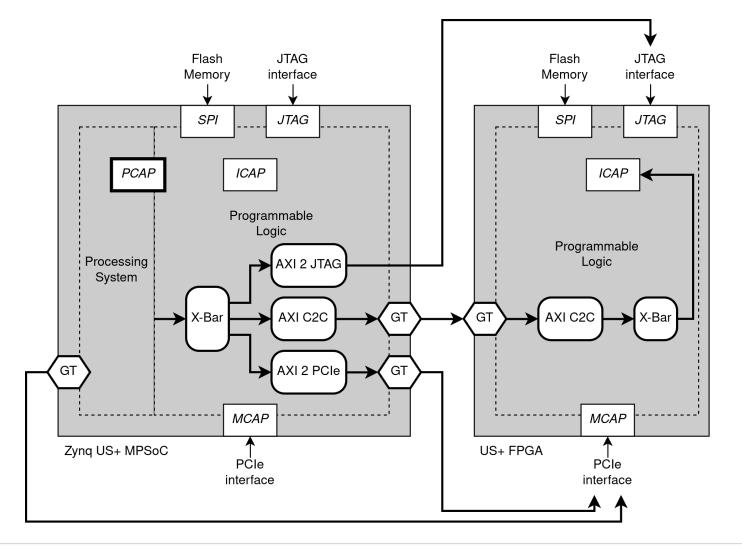

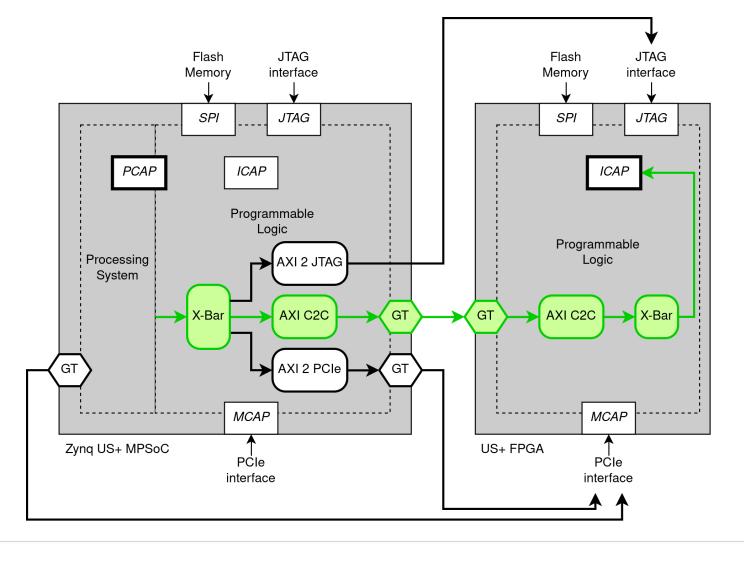

# Initialising an FPGA from an MPSoC

Marvin Fuchs - Cross-Chip Partial Reconfiguration

- Multiple approaches

- JTAG

- PCIe

- AXI Chip2Chip

# Initialising an FPGA from an MPSoC

- Multiple approaches

- JTAG

- PCIe

- AXI Chip2Chip

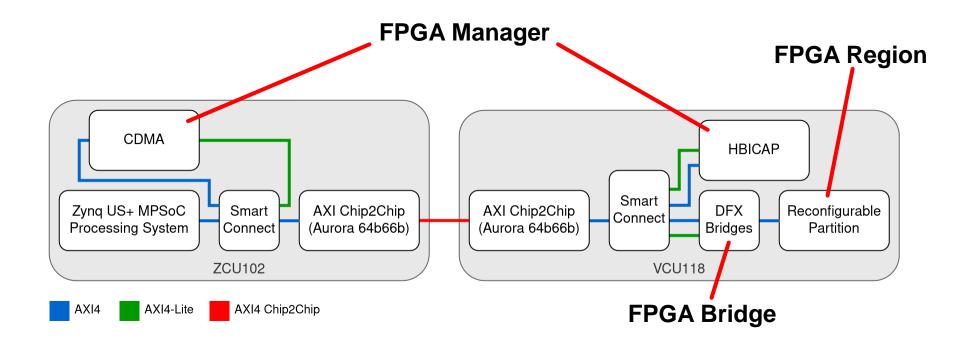

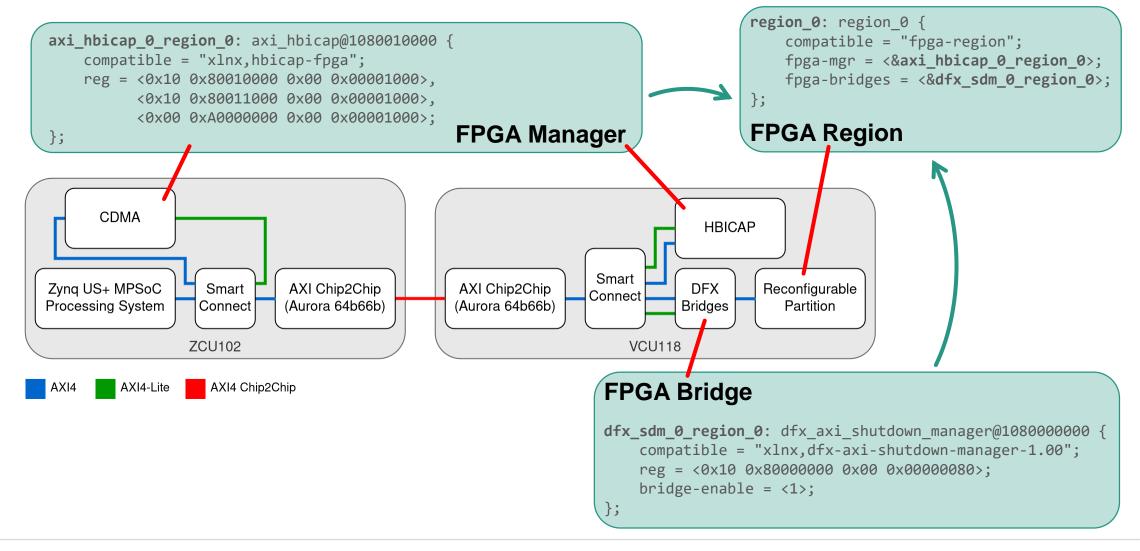

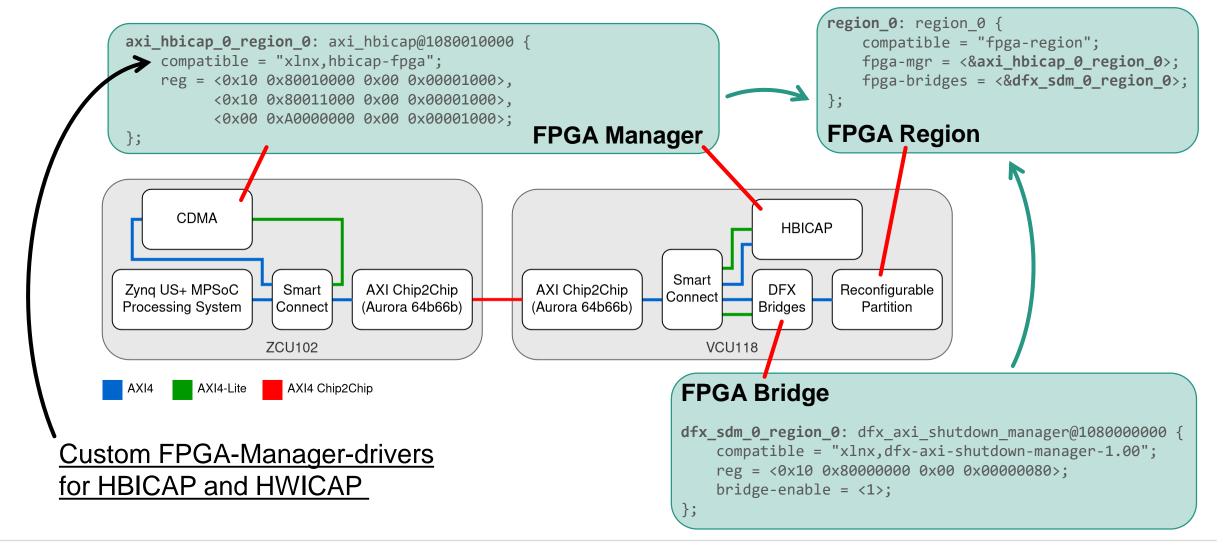

#### Our Choice: AXI Chip2Chip

- Reuse of existing connection

- ICAP is the fastest interface

- Requires generic preinitialisation from flash

# **System Start-Up**

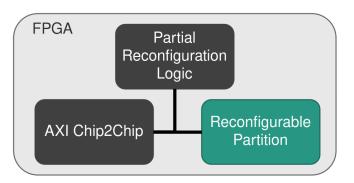

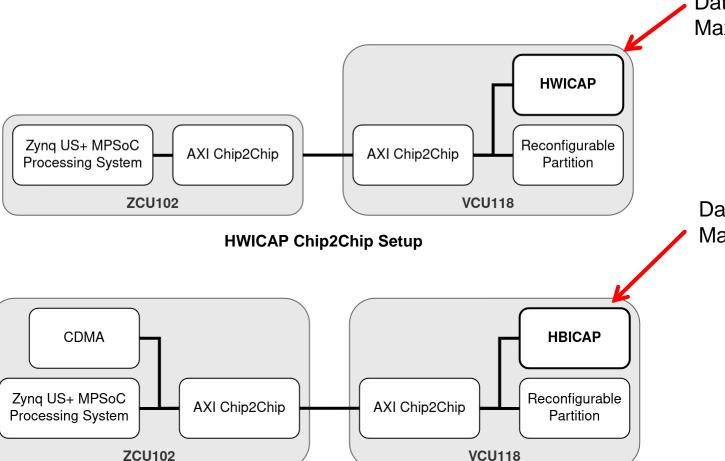

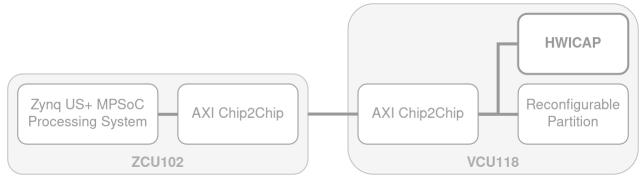

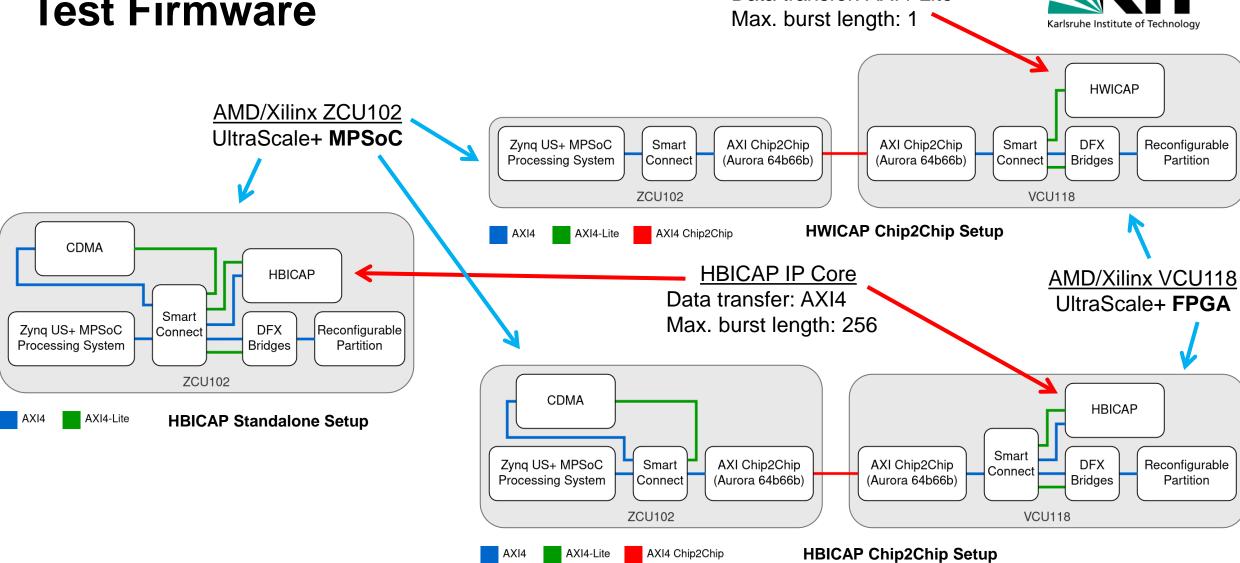

# **Three Test Setups**

HWICAP IP Core

Data transfer: **AXI4-Lite**

Max. burst length: 1

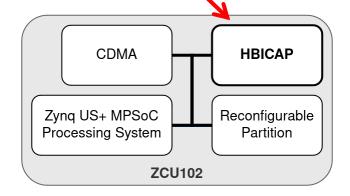

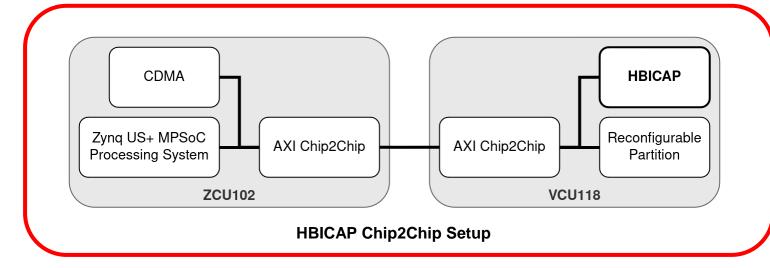

#### **HBICAP IP Core**

Data transfer: AXI4

Max. burst length: 256

**HBICAP Standalone Setup**

#### How can Linux control this?

**HWICAP Chip2Chip Setup**

Let's use this as an example

**HBICAP Standalone Setup**

# **FPGA Subsystem in Linux**

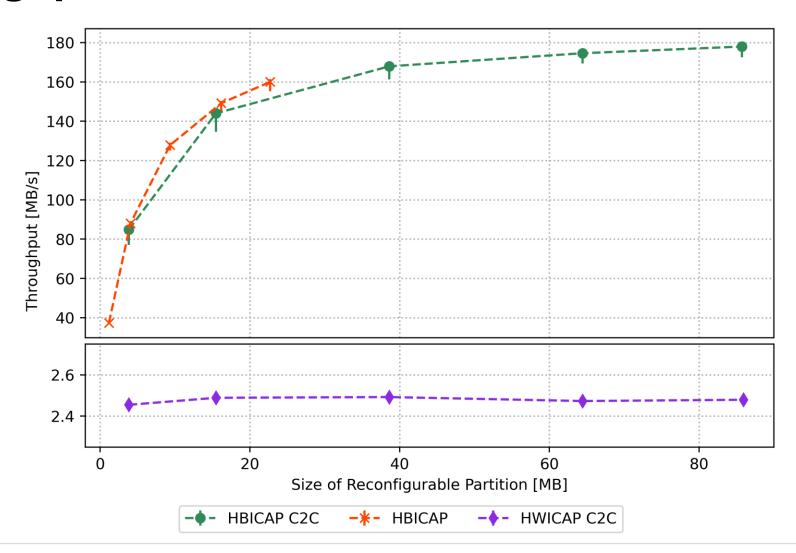

# Performance: Throughput vs. RP Size

#### **HBICAP**

- Throughput depends on reconfigurable partition (RP) size

- Max. ~180 MB/s

- Only minor fluctuations

- Impact of Chip2Chip neglectable

#### **HWICAP**

- Significantly slower

- Only minor fluctuations

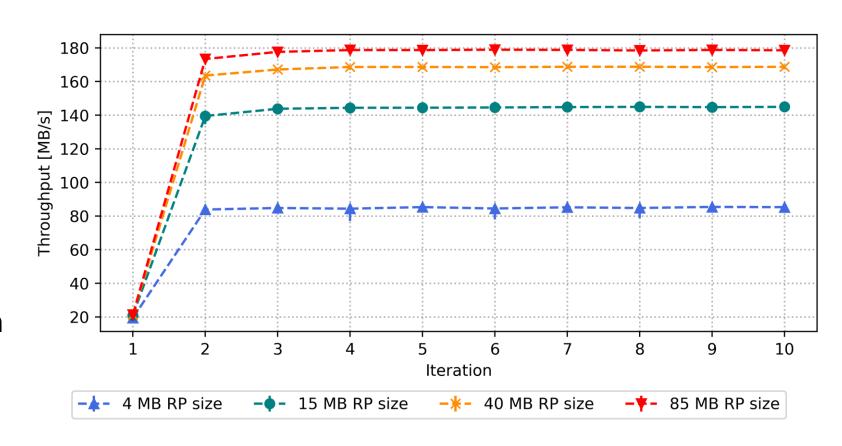

# Performance: Consecutive Reconfigurations

- Throughput almost constant from second reconfiguration on

- Only minor fluctuations

- First reconfiguration always slow

- Cause so far unknown

- Still under investigation

Marvin Fuchs - Cross-Chip Partial Reconfiguration

#### **Outlook**

- Further investigation of the slow first reconfiguration

- Focus on the Processing System of the MPSoC and especially on Linux

- Exploration and optimization in larger systems with more FPGAs connected

- So far only 2 FPGAs connected to 1 MPSoC

- The goal is 10 FPGAs and 1 RFSoC on custom HW

- Exploration of open source ICAP controllers

- Adaptations needed

#### Conclusion

- We have developed a method based on partial reconfiguration for initializing heterogeneous systems via AXI Chip2Chip.

- The proposal can reduce maintenance effort and facilitate the distribution of updates.

- In test setups, the concept has proven to be fast, reliable, and stable and will soon be scaled up to the full QiController system with up to 10 FPGAs per RFSoC.

- Many ATCA cards at CERN are also compatible with this method, and this field of application will also be explored.

# Backup

20

Marvin Fuchs - Cross-Chip Partial Reconfiguration

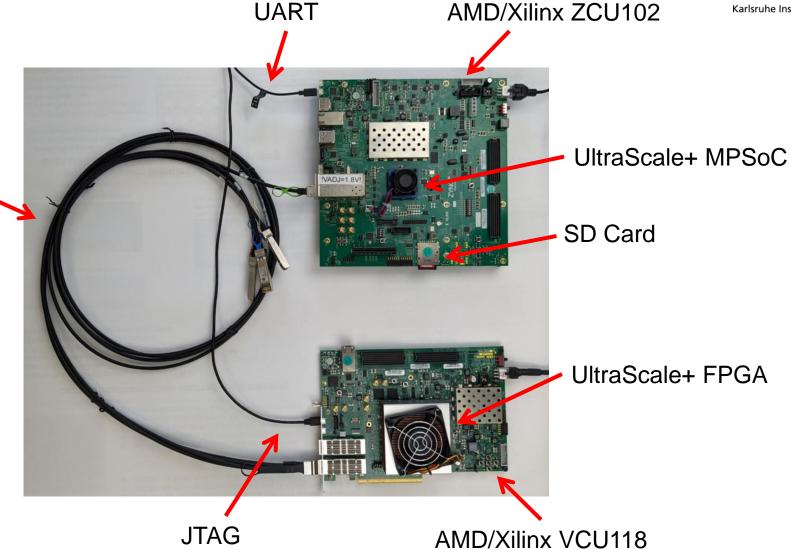

# **Test Setup**

QSFP to SFP+ Cable (AXI Chip2Chip)

# **Test Firmware**

**HWICAP IP Core** Data transfer: AXI4-Lite

- Composed of various devices from AMD / Xilinx

- MPSoCs

- RFSoCs

- FPGAs

- Architecture for Qbit control system

- Multiple systems developed at CERN

Multi-Device QiController Architecture

Global Common Modul ATCA Card

Apollo ATCA Card

Serenity S ATCA Card