An FPGA-Based High Precision Pulse Width Measurement Timeto-Digital Converter with Time Division Multiplexing Encoder

Wenhao Duan<sup>1,2</sup>, Changqing Feng<sup>1,2</sup>, Junchen Wang<sup>1,2</sup>, Yu Wang<sup>1,2</sup>, Zhongtao Shen<sup>1,2</sup>, Shubin Liu<sup>1,2</sup>

# Introduction

- FPGA-based TOT Measurement TDCs in High-Energy Physics: TDCs are vital for high-energy physics experiments. FPGA-based TDCs offer advantages like increased channel density and reduced power consumption.

- Challenges and Optimization: Conventional TDL TDCs face limitations in capturing rising edges only. Optimization strategies involve resource-intensive methods, but they compromise resource usage, channel density, and measurement throughput.

- Novel Architecture and Performance: The dual-TDL TDC, featuring a TDM encoder, achieves remarkable results, with a minimum measurable pulse width of 520 ps and an average rms precision below 5.3 ps. It sustains a high throughput of 250M samples for arrival time and TOT measurements.

- Superiority: Compared to other FPGA-based TOT TDCs, the dual-TDL TDC excels in timing precision and resource efficiency.

# TDC Architecture

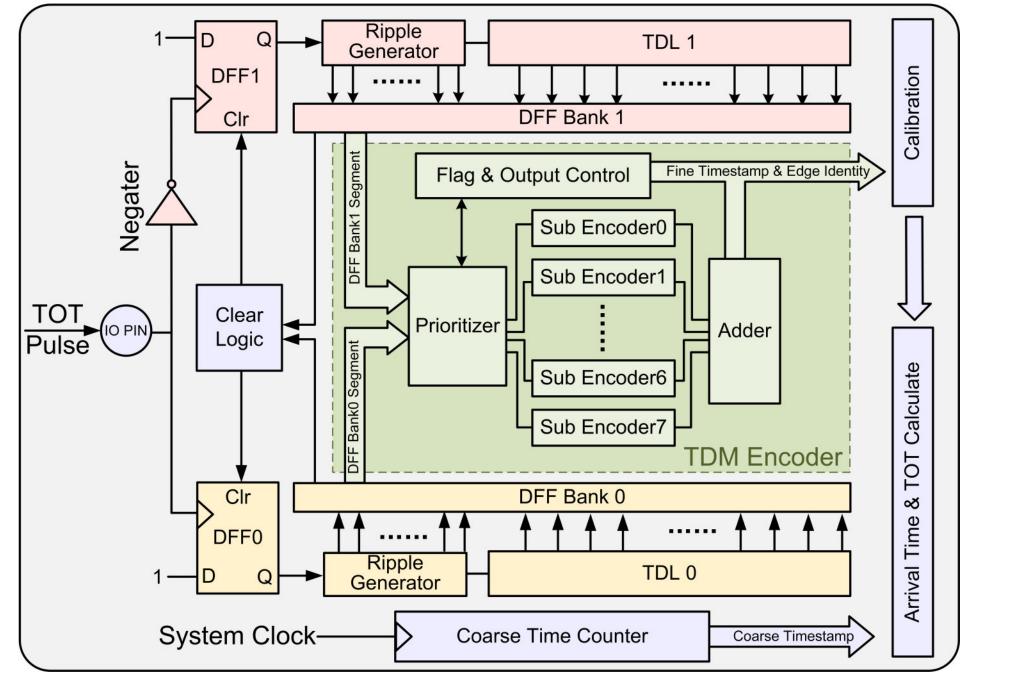

## Dual TDL TDC Stracture

• **Dual TDL Module:** Processes pulse edges separately in TDLs for fine timestamp generation. • Trigger and Ripple Generator: Initiates ripple signals in TDLs for multi-measurements.

### Dual TDL Module

Our design efficiently controls delay sensitivity in the ripple generator by managing the relative locations of DFF0 & TDL0 and DFF1 & TDL1 using Vivado's RLOC Constraints.

## **TDM Encode Scheme**

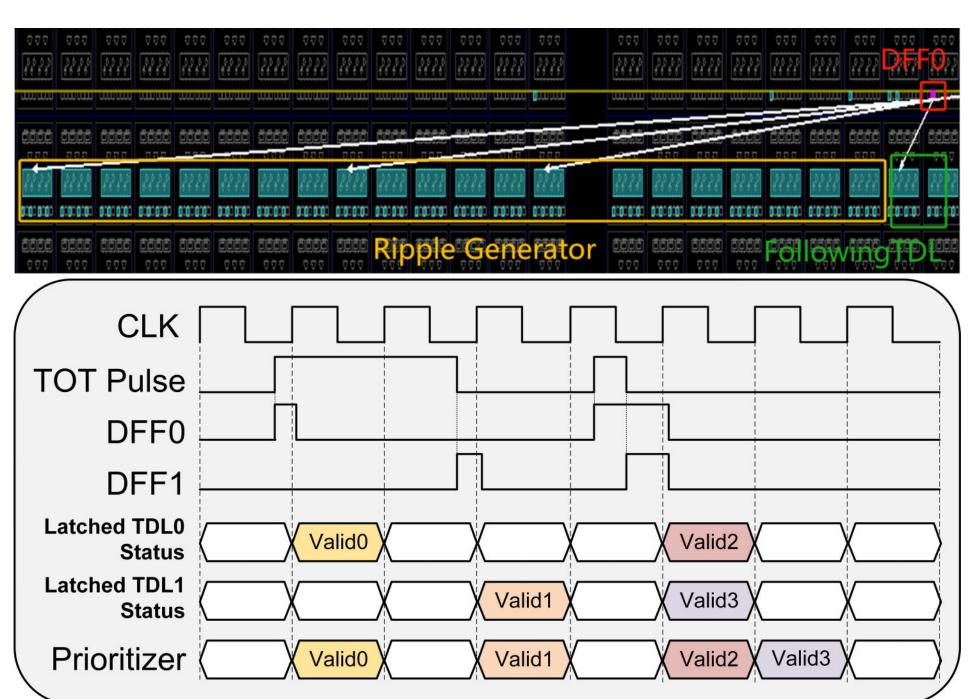

• **Prioritization:** Selects one valid status from TDL0 or TDL1 based on the clock cycle.

- Clear Logic: Ensures proper pulse generation and guards against invalid pulses during reset.

- **TDM Encoder:** Converts TDL statuses into fine timestamps, adeptly handling the latched status from dual TDLs.

The prioritizer selects between segments from DFF bank0 and DFF bank1 based on activity, ensuring smooth transmission even when both TDLs are active due to narrow pulse widths, preventing data congestion.

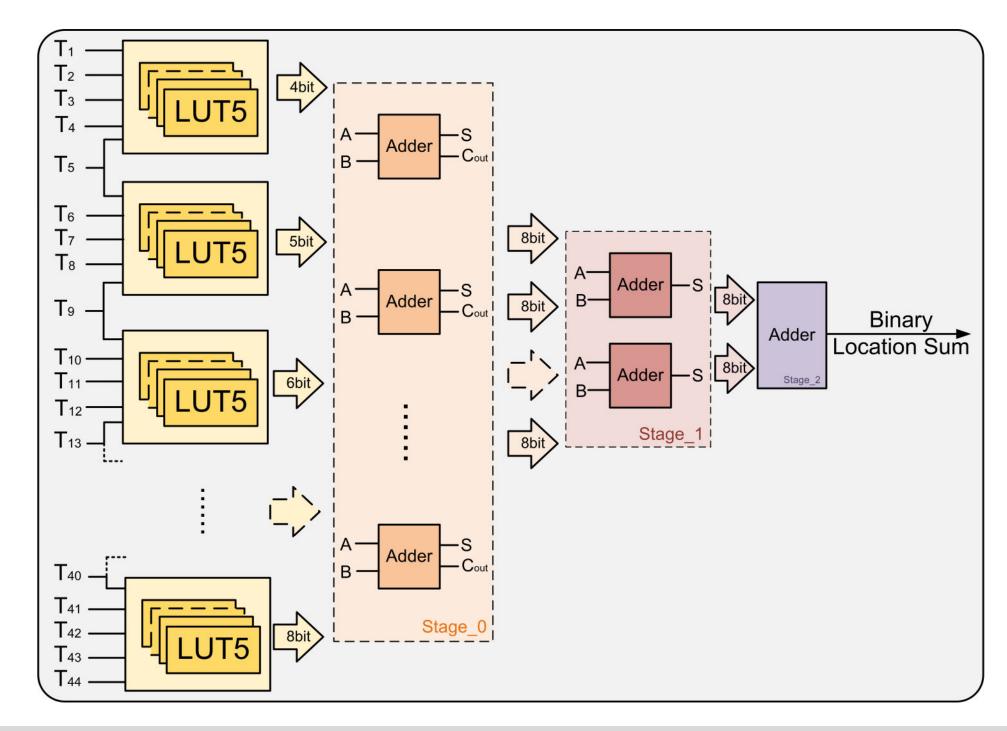

- Subsequence Decomposition: Breaks down TDL status into subsequences to identify transition edges.

- Sub-encoder Construction: Calculates transition edge positions in 5-bit fragments using LUT5 groups and adders.

- Aggregation: Sums binary encoded values from all sub-encoders to represent the TDL status.

## Performance Test

#### Test Environment

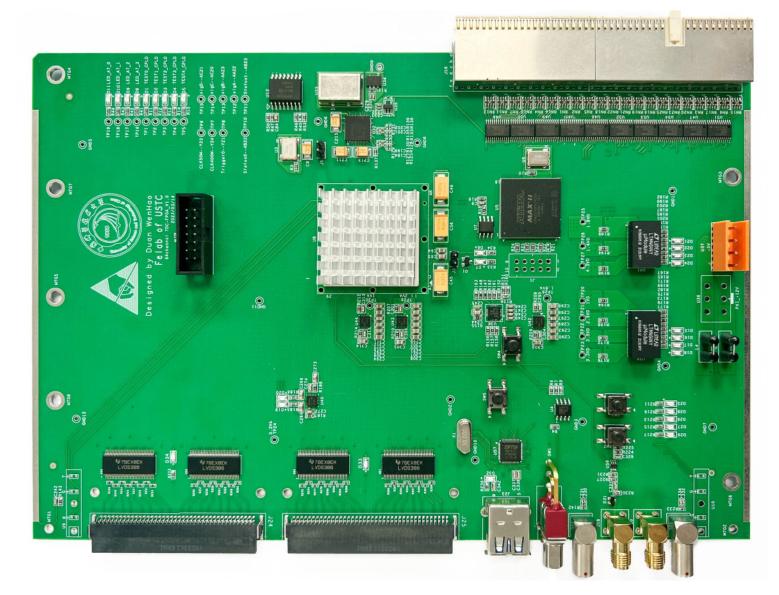

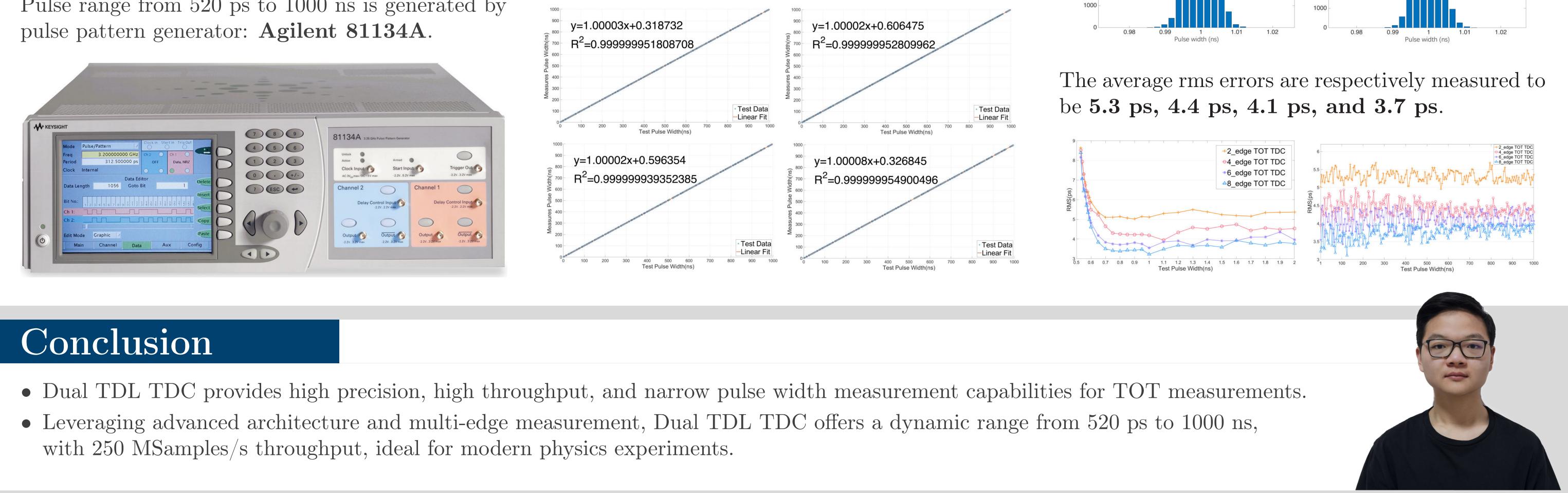

A series of 2, 4, 6, and 8-edge Dual TDL **TDCs** were implemented on a custom TDC evaluation board utilizing the Xilinx xc7k410t-2ffg900i FPGA.

Pulse range from 520 ps to 1000 ns is generated by pulse pattern generator: Agilent 81134A.

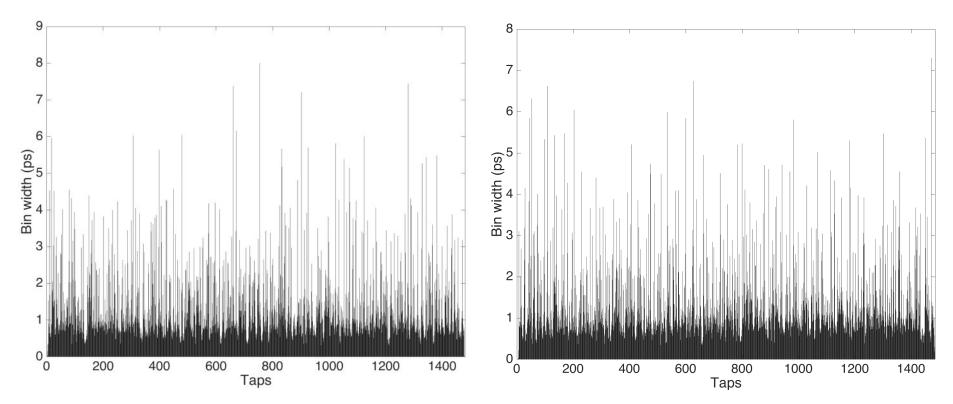

#### Calibration

The **code density test** evaluates a Time-to-Digital Converter's performance by analyzing the distribution of measured time intervals, providing crucial insights into resolution and linearity.

Offset calibration aligns measured pulse edges with actual pulse edges by determining the offset using a linear fit method, enhancing the accuracy of time measurements in TDCs.

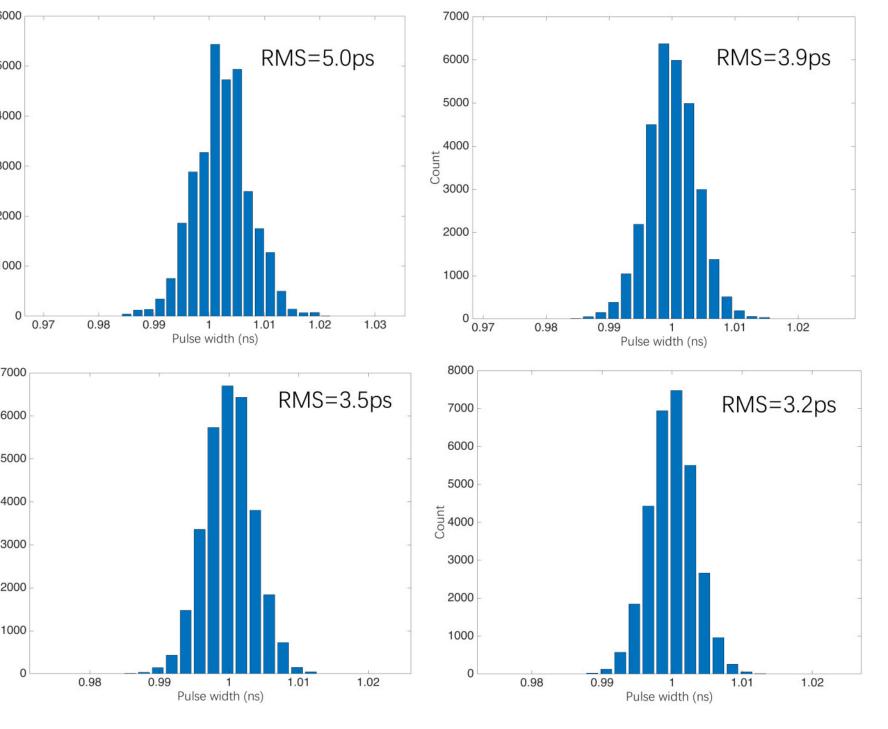

## **RMS** Precision

The precision and dynamic range of 2, 4, 6, and 8edge Dual TDL TDCs are assessed, revealing typical rms errors of 5 ps, 3.9 ps, 3.5 ps, and 3.2 ps respectively at 1 ns TOT time.

Wenhao Duan

caestecker@mail.ustc.edu.cn

<sup>1</sup>State Key Laboratory of Particle Detection and Electronics, USTC, Hefei 230026, China <sup>2</sup>Department of Modern Physics, USTC, Hefei 230026, China