# Hybrid Scrubber of SEM and Picoblaze for FPGA on COMET Read-out Electronics

### Eitaro Hamada<sup>1</sup>, Youichi Igarashi<sup>1</sup>, Kazuki Ueno<sup>2</sup>

<sup>1</sup>High Energy Accelerator Research Organization, <sup>2</sup>Osaka University

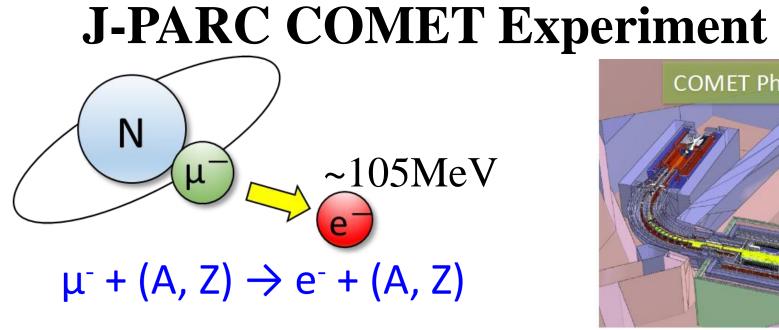

## Introduction

Purpose: Search for muon-to-electron conversion

- Undetectable physics process in the Standard Model [1]

- Single Event Sensitivity: O(10<sup>-15</sup>) (Phase-I)  $O(10^{-17})$  (Phase-II)

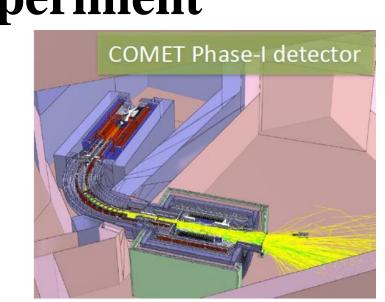

#### **Straw Tube Tracker**

To suppress the background and Vacuum to achieve the goal sensitivity, we adopt this detector.

- momentum resolution:

- better than 200 keV/c

- **ROESTI**(Read-Out Electronics for Straw Tube Instrument)

The ROESTI reads out the signal from the straw tube

tracker precisely [2].

- installation location:

- in the gas manifold

Straw Tube

(light materials)

Gas Manifold

#### **Neutron Effect**

- Neutron fluence (Phase-I):  $1.0 \ge 10^{12} [n/cm^2](1 \text{ MeVeq})$ (Measurement time: 150 days)

- SEU (Single Event Upsets): Bit upsets in the

- FPGA configuration particle 🔵 (neutron) memory occur due to Gate neutron irradiation.

Drain

## Motivation

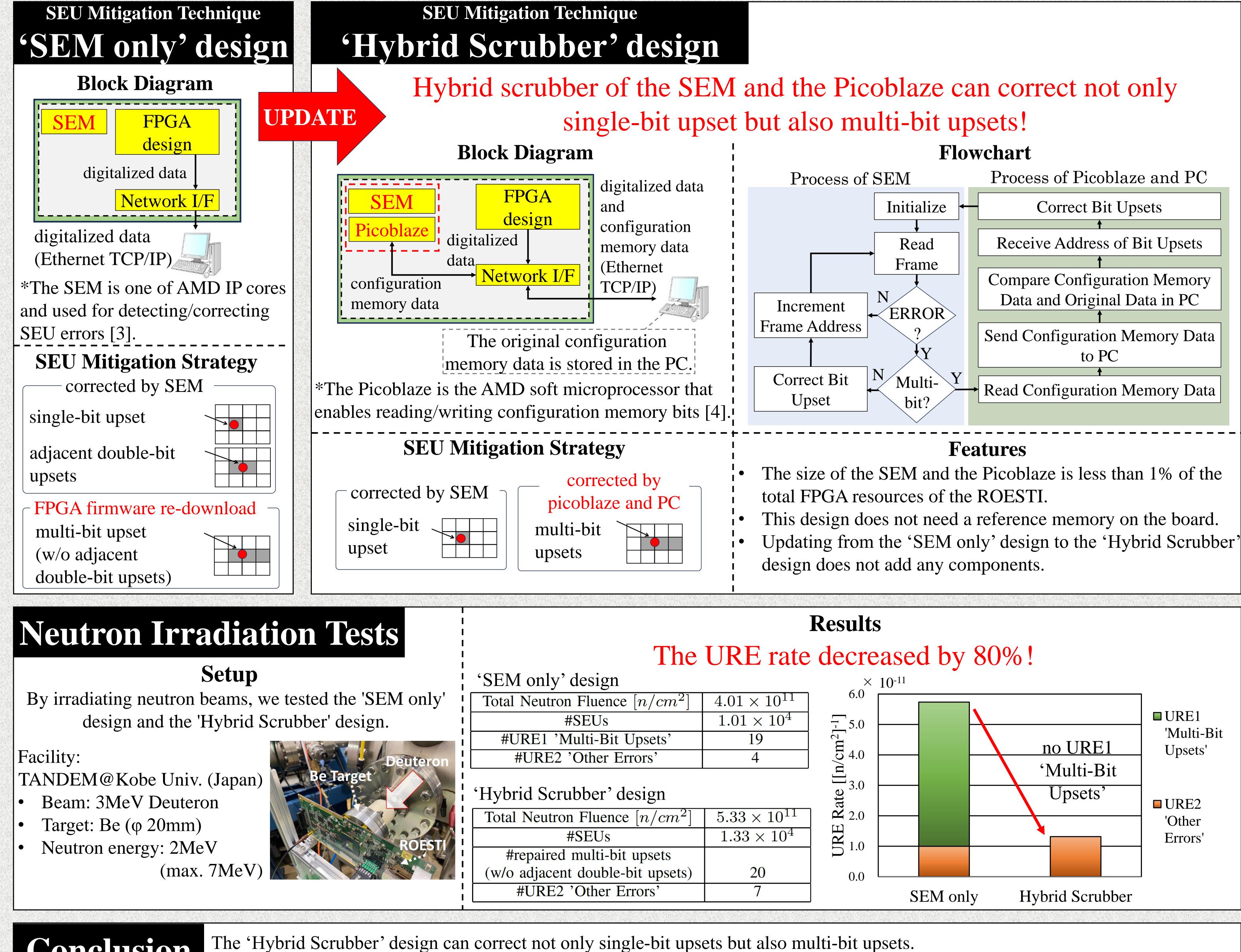

Our conventional FPGA has adopted the 'SEM only' design for SEU mitigation.

- However, even with this design implemented, two types of UnRecoverable Errors (URE) occur as shown in the right.

- The purpose of this study is to develop a new SEU mitigation technique that resolves URE1 'Multi-Bit Upsets' and decreases the dead time.

URE

SEUs have a potential to cause UnRecoverable Error (URE). URE cannot be repaired without re-downloading the FPGA (UnRecoverable Error) firmware, which takes 37 seconds of dead time.

**URE1. 'Multi-Bit Upsets'**

The 'SEM only' design cannot correct multi-bit upsets (w/o adjacent double-bit upsets) in a configuration frame.

**URE2. 'Other Errors'**

Source

Charged particle

An upset of a critical register can cause URE. e.g. 1. registers in a clock generation module 2. registers in the SEM

Conclusion The 'Hybrid Scrubber' design can decrease the URE rate by 80% compared to the 'SEM only' design. Because the frequency of FPGA firmware re-downloads can be reduced, the dead time decreases by 80%, and the Mean Time Before Failure (MTBF) is five times longer.

References: [1] Y. Kuno and Y. Okada, Rev. Mod. Phys. 73, 151-202, Jan.(2001) [3] AMD Inc., "Soft Error Mitigation Controller" (PG036) [2] K.Ueno, et al., Nucl. Instrum. Meth. A, 936, 298-299, (2019) [4] AMD Inc., "PicoBlaze 8-bit Embedded Microcontroller User Guide" (UG129) Acknowledgement: This work was supported by World Premier International Research Center Initiative (WPI), MEXT, Japan. The authors would like to express their sincere thanks to the staffs of The Tandem Accelerator Laboratory of Kobe University.