# New developments for the Trigger-Time-Event system for the W7-X experiment

J. Schacht<sup>1</sup>, T. Brockmann<sup>2</sup>, M. Marquardt<sup>1</sup>, J. Recknagel<sup>1</sup>, and T. Schröder<sup>1</sup>

*Abstract*—Since the first plasma operation in 2015, the superconducting fusion experiment Wendelstein 7-X has successfully completed 4 experiment campaigns (OP1.1, OP1.2a, OP1.2b, and OP2.1). The machine maintenance phase was completed at the end of January 2024, followed by the commissioning of W7-X. The scientific plasma operation phase OP2.2 is planned from September 2024.

The Trigger Time Event System is used by the control and data acquisition systems of the central control systems, the technical components and the diagnostics of W7-X for their time synchronization, for processing events and for generating and receiving trigger signals. This use cases makes it necessary to adapt the TTE system to the changing requirements of users.

After an introduction to the functions and structure of the TTE system, this contribution describes the current expansion status of the TTE system and the planned modifications and expansion of the hardware and software of the TTE system. Finally, the current status of the planned work on the TTE system for the upcoming W7-X operational phase Op2.2 is presented. The contribution ends with a summary.

*Index Terms*—Timing system, synchronization, event distribution, trigger generation,

#### I. INTRODUCTION

**T**HE Wendelstein 7-X fusion experiment is based on the stellarator principle and has a magnet system with 50 non-

planar and 20 planar superconducting coils. Stationary plasma operation with full heating power is possible up to a maximum discharge duration of 30 minutes [1] [2] [3] [4].

The first scientific plasma operation took place in December 2015. So far, 4 operational phases have been successfully completed, in which a total of 6,559 plasma discharges with a total plasma time of 473 min have been generated [5] [6] [7] [8].

The next operational phase (OP2.2) will begin with scientific plasma operation in September 2024. Commissioning of the Wendelstein 7-X facility has been underway since the beginning of 2024 and the first plasma discharges will be carried out in June 2024 as part of the commissioning process.

The Wendelstein 7-X is a very complex technical system consisting of many technical installations (e.g. vacuum systems, cooling systems, magnetic field systems, plasma heaters [9] [10] [11] [12]), fueling systems [13], as well as operational and scientific diagnostics [14] [15] [16] [17] (diagnostics for measuring plasma energy, plasma density, turbulence measurements, i.a.).

During the preparation and execution of the plasma experiments, processes for control and data acquisition must be synchronized in the control and data acquisition systems themselves as well as between the systems. It should be possible to start certain control actions at predefined times. With multichannel data acquisition, synchronous clock signals are often required for the A/D converters. Recorded events and measured values should be provided with a time stamp in order to evaluate event chains and measured values across systems.

Many fusion experiments and particle accelerators have developed their own trigger and timing systems (e.g. [18], [19], [20], [21], [22]) to meet their specific requirements in terms of synchronization, time accuracy and the generation and processing of triggers.

The trigger time event system (TTE system) developed specifically for the requirements of W7-X was put into operation before the start of the first W7-X operating phase Op1.1 in December 2015 [23]. Since then, the TTE system has been continuously expanded and technically enhanced.

This article introduces the key requirements and architecture of the TTE system. Important innovations for TTE system components are then described. This is followed by a project status of the TTE system. The article ends with a short summary and an outlook.

#### II. REQUIREMENTS FOR THE TTE SYSTEM

The main requirement for time-related functions is the provision of a synchronized clock signal, which is derived from a central clock generator. The local time counters should be synchronized system-wide to a central clock. The requirements for the accuracy of the synchronization depend on the specific application. For example, a clock synchronization in the range of 10 ms - 50 ms is sufficient for a PLC application. For fast control tasks, this should be better than 1 ms. For data acquisition of high-frequency signals, a time resolution in the range of 100 ns - 1  $\mu$ s is often required. Alarm functions with absolute and relative alarm times and time capture functions are also required.

The analysis of the control and data acquisition requirements for W7-X for a timing system revealed that the system should also be able to process trigger signals and event messages. For the trigger functions, it should be possible to read in and output trigger signals via a signal interface. It should also be possible to generate periodic pulses and user-defined pulse sequences.

The TTE system should be expandable without limitation to enable the integration of new control and data acquisition systems into the TTE system.

The third category of requirements describes the ability to send and process special event messages within a system and between systems.

## III. TTE SYSTEM OVERVIEW

The TTE system has a hierarchical structure, as shown in Fig. 1. The central TTE system is at the top of this structure and is assigned to the central control system of W7-X.

Fig. 1. Structure of W7-X TTE system.

The main functions of the cTTE system are provided in the cTTE device. An oven-stabilized clock generator generates the master clock with a frequency of f = 50 MHz for the central and local clocks. This clock generator can be controlled by the clock of the LAN Time Server via a control loop.

The clock is doubled to 100 MHz in the cTTE device and drives bit 1 of a 64-bit time counter, whereby the time counter counts in 10 ns increments. The 64-bit register value of the cTTE time counter corresponds to UTC (Universal Time Coordinated).

The time counters of the PLCs and computers with low time resolution requirements are synchronized by a connection to the LAN time server using the NTP protocol.

The cTTE device has an optical transceiver module that communicates with the local TTE systems via an optical unidirectional network (use of the device version cTTE V1) bidirectional network (use of the device version cTTE V2). Clock and time information as well as event messages are transmitted to the local TTE systems. Once the new expansion stage of the TTE system has been commissioned, the ITTE devices can transmit event messages to the central TTE system.

The TTE switch devices in the TTE network are responsible for dividing the TTE network into the required number of subnets and ultimately for providing the ports required for connecting the local TTE devices.

To ensure high availability, the central TTE system components – specifically, the cTTE device, the cTTE control

computer and the Lan Time Server are designed redundantly. This redundancy enhances system reliability by providing backup options in case of component failure.

The cTTE source switch device connects the transmission signal of the active cTTE\_V2 device to the downlink of the TTE network. The cTTE\_V2 master and slave device receive all messages from the local TTE devices via the uplink of the TTE network.

The TTE network and the local TTE systems are designed without redundancy.

The ITTE\_V2, cTTE\_V2 and TTE Network Switch\_V2 devices are connected to their assigned Control Station via a 1 GBit/s Ethernet interface in order to exchange configuration data, control commands, and status and timing data. The cTTE / ITTE devices of the previous version V1 were computer cards with a PCI bus interface.

For clock synchronization, the cTTEV2 device is connected to the 1pps signal of the LAN Time Server.

The cTTE V2 and ITTE V2 devices have a number of I/O ports with special functions (such as pulse generator outputs, triggering of the time capture function, triggering of predefined event messages) and I/O ports for user-defined functions.

## IV. NEW DEVELOPMENTS

The existing TTE devices were further developed on the basis of operating experience with the TTE system and the wishes of the users. Table 1 shows on overview of changes of TTE devices.

| TABLE 1                        |                  |                 |

|--------------------------------|------------------|-----------------|

| OVERVIEW OF TTE DEVICE CHANGES |                  |                 |

| Development                    | Replacement for  | Available since |

| ITTE_V2 device                 | ITTE_V1 PCI card | 2022            |

| cTTE_V2 device                 | ITTE_V1 PCI card | 2023            |

| cTTE source switch             | -                | 2024            |

| TTE switch_V2                  | TTE switch V1    | 2024            |

The most important changes to the TTE devices are presented below.

## A. Changes of *lTTE\_V2* device

The ITTE PCI card was the first TTE device to be converted to a 19" / 1 high unit device with a 1 GBit/s Ethernet interface. A comprehensive description of the structure and features of the ITTEV2 device is given in [24]. After completion of the operating phase OP2.1 in May 2023, identified deficiencies in the FPGA program were corrected and new features were implemented for the transmit data module and for the pulse sequence generator module.

In the FPGA program, the Pulse Sequence Generator (PSG) module has been fundamentally revised in order to simplify the application for the user.

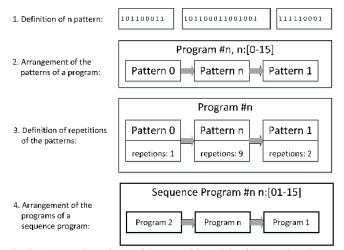

The PSG module uses so-called patterns, programs and sequences to generate pulse sequences.

Patterns are based on predefined bit sequences. For each pattern, the time length of a bit is defined with the value "high" and a bit with the value "low". The bit times of a logical 1 and a logical 0 are configured as multiples of the system clock TCLK.

A pattern has a maximum length of 32 bits. The number of bits/pattern used (pattern length) is defined for each pattern. A maximum of 16 different patterns can be defined.

A program consists of a sequence of max. 16 different patterns. For each pattern in a program, you can specify whether it is to be executed once or several times before the next program step is processed.

When a sequence program is started, programs are processed in a defined order. Each sequence program has a maximum of 16 steps. The program to be executed is defined for each step.

A maximum of 16 different sequence programs can be defined. It must be specified whether a sequence is to be processed once or several times. It is possible to define an endless loop for the continuous repetition of the sequence. First, patterns are defined from bit sequences (patterns), which can contain a maximum of 128 bits. The time for a bit =1 and for a bit =0 can be configured. Fig. 2 shows the configuration process for a pulse sequence.

Fig. 2. Programming scheme of the new PSG module of ITTE\_V2 device.

## B. ITTE\_V2 device for standard trigger application

An ITTE\_V2 device with a special FPGA configuration was programmed for easy integration of data acquisition into the W7-X experiment sequence.

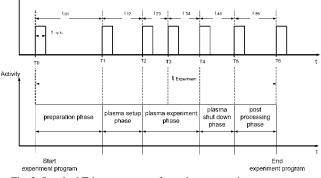

In this FPGA configuration, the event message module and 7 I/O trigger modules were statically configured so that an assigned trigger generates an output signal when a specific event message is received. The individual triggers are linked to the start time of different experiment phases (see Fig. 3). The event messages are sent by the cTTE\_V2 device at the instigation of the central experiment sequence controller.

By using the standard trigger, the diagnostic system can decide which activities it wants to start or end for which trigger. Trager

Fig. 3. Standard Trigger sequence for a plasma experiment program.

# C. The cTTE-V2 device

The functions of the previous cTTE\_V1 PCI card have been implemented in a 19" / 1 High Unit built-in device with a 1 GBit Ethernet interface to its control PC.

Fig. 4 shows a front view of the cTTE\_V2 device.

Fig. 4. Front view of cTTE\_V2 device.

The internal structure of the cTTE\_V2 device is shown in Fig. 5. This device uses the same FPGA board (4) as the ITTE\_V2 device, which has significantly reduced the development effort. This FPGA card is equipped with a Virtex 6-130t FPGA and a DDR3 RAM module. The motherboard (3) with the power supply unit (1), signal driver, and the oven stabilized oscillator board (2) are new developments.

Fig. 5. cTTE\_V2 device with open housing.

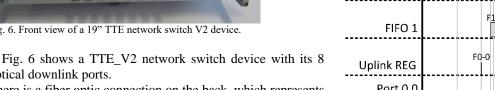

#### D. The network switch device

TTE network switches have the task of connecting the central TTE device with any number of local TTE devices via an optical network. Synchronization information, time data packets and event messages are exchanged via this network. The TTE network switches have one uplink port and 8 downlink ports.

Version V1 of the TTE network switch was based on electronics without an FPGA and was designed only for a unidirectional optical connection from the central TTE (cTTE) to the local TTE devices (ITTE).

For the operating phase OP2.1, version V2 of the TTE switch was developed in order to meet the requirements of new ITTE\_V2 and cTTE\_V2 devices.

The FPGA card of the TTE network switch is identical in hardware design to the ITTE\_v2 card, supplements the basic functions of the TTE network switch version V1 by adding the reverse transmission direction and its transmission prioritization.

Fig. 6. Front view of a 19" TTE network switch V2 device.

optical downlink ports.

There is a fiber optic connection on the back, which represents the uplink (UL). The UL is used to connect the switch to the next higher hierarchy level, which can be either another TTE network switch or a cTTE card.

Inside the switch is a FPGA that takes over the control tasks. Incoming messages at the UL are forwarded without delay to all outgoing DL ports. The core function is the intermediate storage of incoming time and event messages from the fiber optic network in FIFO structures and their sequential forwarding to the outgoing UL port.

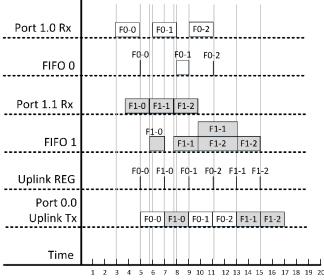

The TTE network switch has two basic operating modes for messages transmission: standard mode and priority mode.

The standard mode is the default mode, which is used directly after the switch is started and without any configuration.

In standard mode, the incoming data from the receivers of the DL ports is temporarily stored in FIFO structures before this data are sent to the next higher level of the fiber optic network via the transmitter of the UL port. By using a round-robin scheduling method, the FIFOs are read in ascending order. If there is a message in the respective FIFO, it is sent and the logic moves on to the FIFO with the next higher number. After FIFO 7, the logic starts again at FIFO 0.

In the priority mode, each FIFO is assigned a priority by the user. The control register responsible for this is written via Ethernet using a configuration message. The FIFO with the highest priority is read out completely first before switching to the FIFO with the next priority. If data is received on ports with a higher priority while a FIFO with a lower priority is being read and the entry is currently sending out, all existing, higher priority FIFO entries are processed according to their configured priority once the current transmission process has been completed. The standard prioritization is according to the port numbers from 0 (highest priority) to 7 (lowest priority) which can be changed in the configuration registers.

Fig. 7 shows an example procedure with only two occupied ports. Event message data from Port 1.0 have a higher send priority than data from Port 1.1. The messages displayed at receivers (RX) and transmitters (TX) are the sequential incoming and outgoing serial data of the respective optical ports. Once a message has been received in full, its content is temporarily stored in a FIFO. The Uplink REG represents the register for the currently to be sent message. This register is written to by the priority control with the event message data from the FIFO of a corresponding port. The respective event message is then output bit by bit to the FBO uplink transmitter.

Fig. 7. Message processing in a TTE\_V2 Network Switch.

As there are no further messages in the port 1 FIFO 1 at time 7, the content of the port 1.1 FIFO 2 is output first. In the meantime, port 1.0 receives further messages, which are now preferentially output. Only then are the remaining event messages from port 1.1 sent out.

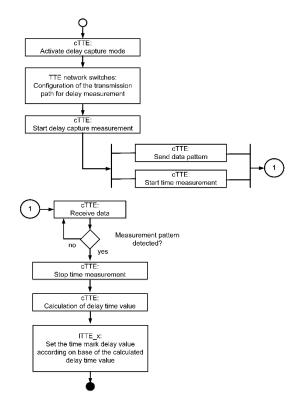

To determine the delay of a TTE network path in the TTE system, the switch can be set to delay measurement mode. This does not change anything on the downlink, as all data will be already forwarded directly and in parallel to all T1.x port transmitters.

The uplink port P1.x to be activated for the delay measurement is configured via Ethernet. The receiver R1.x of this configured port P1.x direct forwarding of its received data to the uplink transmitter T0.0.

The last TTE network switch in the TTE network hierarchy, which connects the lowest level ITTE devices, is a special case. To measure the transmission delay in a TTE network section, the data to be sent via the T1.x transmitter of port 1.x of a TTE network switch is mirrored directly to the Tx0.0 data transmitter of the uplink port by means of a configured short circuit. This means that the received data packet can be sent directly back to the cTTE receiver. The transmission time of the measurement data for the selected network route can then be determined in the cTTE device and the delay calculated from this.

A activity diagram for the delay measurement processing in TTE network is shown in Fig. 8.

Fig. 8. Activity diagram for the delay measurement of a TTE network path.

Fig. 9. IRIG-B converter device.

## E. The TTE Source switch device

The TTE Source switch is a new development. When operating the two cTTE\_V2 devices in redundant mode, the transmission signal of the active cTTE\_V2 device must be transmitted to the local TTE system via the TTE network. The TTE signal source switch device is responsible for switching the transmit signal. It is equipped with a  $\mu$ C board with an Ethernet interface. The signal source can either be switched manually or remotely.

## F. The IRIG-B converter device

Products from Gantner Instruments [11] are often used at W7-X to measure mechanical and thermal variables. These measurement modules can be synchronized via the IRIG-B protocol. A converter module has been developed so that these Gantner measuring systems can be synchronized to the W7-X time of the cTTE system. It has a connection to the TTE network and receives the periodically time information from cTTE system. The IRIG-B coded time signal is then output to the measuring modules.

The converter module is based on an FPGA module (AMD Spartan 6) and an electronic board for the optical receiver of the TTE signal and output of the electrical IRIG-B signal.

The IRIG-B converter has a top-hat rail housing, as shown in Fig. 9.

## V. STATUS AND OUTLOOK

New versions of the ITTE device and the cTTE device have been developed for the future-proof operation of the TTE system. The ITTE\_V2 devices have been in use since the OP1.2b operating phase. However, the FPGA configuration of these devices has been partially revised. The new devices for the central TTE system (cTTE\_V2 devices, TTE network switch, TTE signal switch) are not yet being used for the upcoming OP2.2 phase, as they still need to be extensively tested together with the new application software. A comprehensive test system is currently being set up for this purpose, which contains all the necessary central and local components of the TTE system.

The number of ITTE\_V2 devices still available is limited. It must therefore be decided soon whether a new FPGA card with a new FPGA type must be developed to meet the future demand for ITTE\_V2 devices.

Another ongoing working package is to develop a common FPGA software for both the ITTE\_V2 und cTTE\_V2 devices.

Furthermore, the previous static determination of transmission delays in the TTE network is to be replaced by dynamic measurement of the delays.

### SUMMARY

In summary, this article has outlined the recent developments and ongoing initiatives within the TTE system for the W7-X fusion experiment. Key advancements include the introduction of new TTE device versions, the potential development of a new FPGA card to address device availability concerns, and the ongoing effort to unify FPGA software for improved efficiency.

Additionally, plans are underway to transition from static to dynamic measurement of transmission delays in the TTE network. These efforts collectively aim to ensure the continued effectiveness and future-proofing of the TTE system to meet the evolving needs of the W7-X experiment.

## ACKNOWLEDGEMENT

This work has been carried out within the framework of the EUROfusion Consortium, funded by the European Union via the Euratom Research and Training Programme (Grant Agreement No 101052200 — EUROfusion). Views and opinions expressed are however those of the author(s) only and do not necessarily reflect those of the European Union or the European Commission. Neither the European Union nor the European Commission can be held responsible for them.

#### REFERENCES

H.-S. Bosch et al., "Transition from Construction to Operation Phase of the Wendelstein 7-X Stellarator", IEEE Trans. on Plasma Science, 42 (3), 432-438, 2014.

- [2] H.-S. Bosch et al. "Engineering Challenges in W7-X: Lessons Learned and Status for the Second Operation Phase", IEEE Transactions on Plasma Science 46 (5), 1131 – 1140, 2018.

- [3] K. Risse et al., "First operational phase of the superconducting magnet system of Wendelstein 7-X", Fusion Engineering and Design, 124, 10-13, 2017.

- [4] A. Winter et al., "Preparation of W7-X CoDaC for OP2", IEEE Transaction on Plasma Science, 48 (6), 1779-1782, 2020.

- [5] Wendelstein 7-X project documentation, "Ringbuch: Operational Phases", document UID: 29F99C, 2023.

- [6] T. Klinger et al., "Performance and properties of the first plasmas of Wendelstein 7-X. Plasma Physics and Controlled", Fusion, 59, 112004, 2017.

- [7] T. Klinger et al.,"Overview of first Wendelstein 7-X high-performance operation", Nuclear Fusion 59, 112004 (2019).

- [8] R. Wolf et al., "Performance of Wendelstein 7-X stellarator plasmas during the first divertor operation phase", Physics of Plasmas 26, 082504 (2019).

- [9] H. P. Laqua, et al., "The ECRH-Power Upgrade at the Wendelstein 7-X Stellarator". EPJ Web of Conferences 277, 04003 (2023).

- [10] H. P. Laqua, W7-X Team, "The ECRH System at W7-X: Status, Results and Perspectives", 46th International Conference on Infrared, Millimeter, and Terahertz Waves (IRMMW-THz). New York, NY: IEEE, October 2021.

- [11] J. Ongena et al., "The ICRH system for the stellarator Wendelstein 7-X", AIP Conference Proceedings 2254, published online AIP Conference Proceedings 2254 (https://doi.org/10.1063/5.0014264), Sept. 2020.

- [12] S. Lazerzon et al., "First neutral beam experiments on Wendelstein 7- X", Nucl. Fusion, 61, 096008, 2021.

- [13] S. Meitner et al., "Design of a continuous pellet fueling system for Wendelstein 7-X", IEE Transaction on plasma science, 48, 1585-1590, 2020.

- [14] M. Endler et al., "Wendelstein 7-X on the path to long-pulse highperformance operation", Fusion Engineering and Design 167, 112381 (2021).

- [15] K. Rahbarnia et al, "Diamagnetic energy measurement during the first operational phase at the Wendelstein 7-X stellarator", Nucl. Fusion, 58, 096010, 2018.

- [16] K.-J. Brunner et al., "Real-time dispersion interferometry for density feedback in fusion devices", Journal of Instrumentation, 13, P09002, 2018.

- [17] A. Puig Sitjes et al., "Real-Time Detection of Overloads on the Plasma-Facing Components of Wendelstein 7-X", Appl. Sci., 11, 11969, 2021.

- [18] G. Maduchi et al., "The timing system of the ITER full size neutral beam injection prototype", Fusion engineering and design, 146, 281-284, 2019.

- [19] C. Megias at al., "Ethernet-based timing system for accelerator facilities: The IFMIF-DONES case", Computer networks, 233, 2023.

- [20] V. Schmidt et al., "The Timing System of the RFX Nuclear Fusion Experiment", Proceedings of international conference on accelerators and large experimental physics control systems, 1992.

- [21] A. Aloisio et al., "Design, implementation and test of the timing trigger and control receiver for the LHC", Journal of Instrumentation, JIST 8 T02003, 2013.

- [22] R. Raupp et al., "The Timing System for the ASDEX Upgrade Experiment Control", *IEEE Transactions on Nuclear Science*, vol. 39, no. 2, pp. 198-204, April 1992.

- [23] J. Schacht et al., "The Trigger-Time-Event-System for Wendelstein 7-X: Overview and First Operational Experiences", IEEE Transactions on Nuclear Science, 66(6), 969-973, 2019,

- [24] J. Schacht et al., "Multifunction-Timing Card ITTEV2 for CoDaC Systems of Wendelstein 7-X. IEEE Transactions on Nuclear Science, 62(3), 1187-1194. doi:10.1109/TNS.2015.2425895, 2015.