Forward Calorimetry

(EM and Hadronic)

# A Proposal for the Clock and Control Distribution for EIC Experiment (ePIC)

J. W. GU (for ePIC collaboration)

|                                                                                                                                           | ESR       | HSR           |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------|

| RMS bunch length $\sigma_{z} \text{[mm/ps]}$                                                                                              | 7-9/23-30 | 75-60/250-200 |

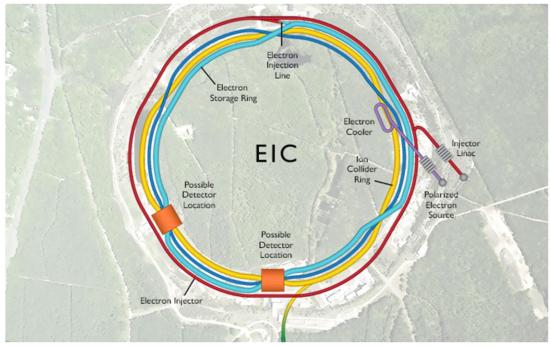

| Electron Beam Energy: 5 – 18 GeV<br>Proton Beam Energy: 41, 100, 275 GeV<br>Luminosity: 10 <sup>34</sup> cm <sup>-2</sup> s <sup>-1</sup> |           |               |

Electron Direction

Tracking

**Imaging Barrel**

**EM Calorimeter**

Backward

Calorimetry

1.7T Superconducting Solenoid

AC-LGAD TOF

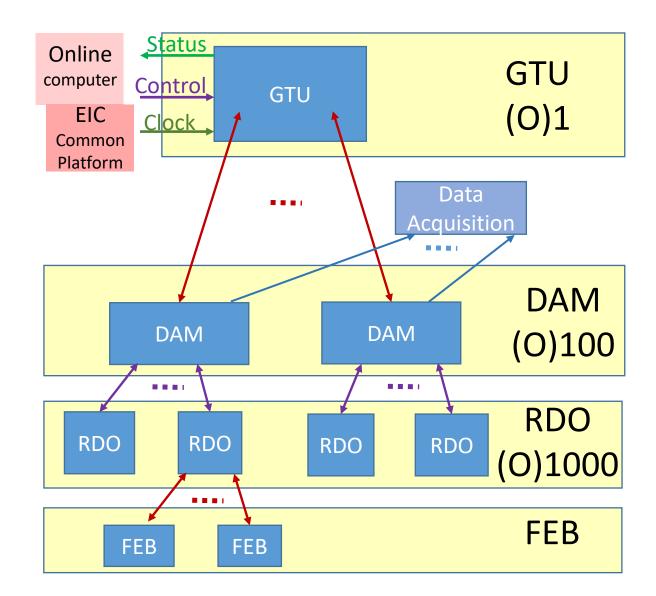

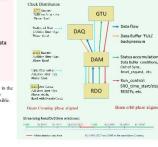

# ePIC DAQ /Clock Control distribution electronics

# GTU: Global Timing Unit

control encoding, status decoding. The interface for machine clock source, Data acquisition control and monitor etc.

## **DAM:** Data Aggregation Module:

The clock/control fanout, and status/busy accumulation.

local control over the RDO boards connected, though the main function of the DAM is for Data Acquisition.

## **RDO:** optical interface of detector ReaDOut

control decoding, status encoding.

The clock/control interface to the front end electronics.

Data collection from Frontend boards, and data transmission to the DAM

## FEB:

Detector dependent Front End / ASIC carrier boards.

# System Clock: 98.5 MHz (100MHz nominal) **ePIC**

## **Clock Distribution**

### **Control Distribution**

A Proposal for the Clock and Control Distribution for EIC Experiment (ePIC)

J. W. Gu\* (for ePIC collaboration) \* Thomas Jefferson National Accelerator Facility (TJNAF), Newport News, VA 23606, USA

#### 5. Some Test results

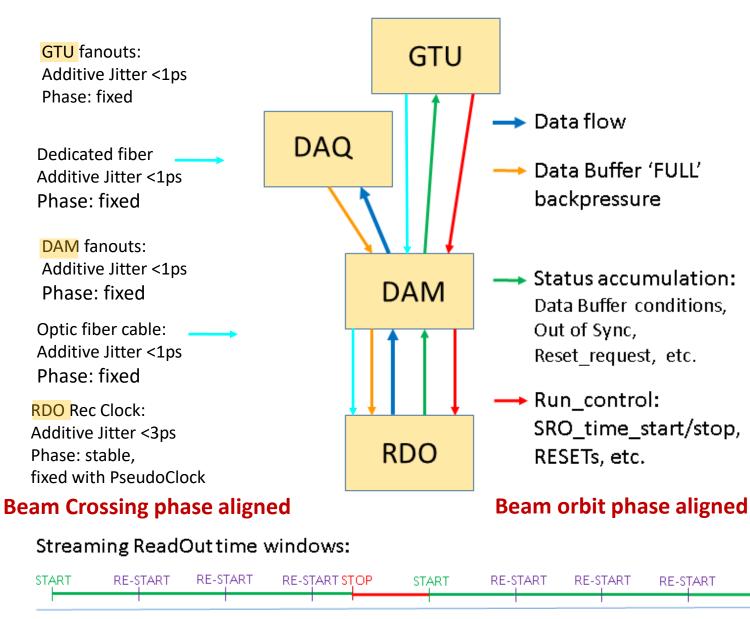

### 3.1 Dedicated fibers between GTU and DAM (and

3. Clock Distribution

5.1 Test setup: Skyworks' Si5344H → System Clock, Reference BNL's FLX182 as DAM: OpalKelly's XEM8320, Xilinx KCU105/Skyworks Si5394A as RDO

transceivers on the GTU. The clock is received by the optic transceivers, and jitter cleaned and fanned out to the MGTs (Multi Gigabit Transceivers) on the DAM.

GTU to monitor the feedback clock phase 3.2 MGT serialized data between DAM and RDOs The GTU CONTROL (8-bit) and DAM CONTROL (32-bit) are serialized and phase aligned with the System clock (98 4

The RDO reconstructs the system clock, and sends front-end electronics data and status back to the DAM (fiber UPLINK).

### 4. Synced CONTROL Distribution

4.1 Fixed latency from GTU to DAM, and RDO The fibers from GTU to DAM will be the same length/delay routed in the DAO computer racks. The fiber delays from DAM to RDO will be measured individually, and saved on the RDO. The RDO will delay the received GTU control commands (compensating for the fiber latency), so that all the RDOs will send the GTU commands at the SAME time (synchronous with the 98.5 MHz system clock

### 4.2 Beam orbit information is embedded in GTU

The GTU, DAM and RDO will all keep (at least) two counters, Beam Crossing counter (11-bit from 1 to 1260), and Beam Orbit counter (at least 5-bit, for a The GTU will send SRO (Streaming ReadOut) time window start command and some other SYNC commands on the first beam crossing of the orbit. The

size of RDO time window can be set on the GTU. 4.3 DAQ data flow control There are data buffers on DAMs and RDOs. The

buffer status is monitored by GTU, DAM and RDO.

# 5.2 (RDO's) RxRECclock Test setup The clock jitter is measured by the positive width and the

negative width of the difference between the RxRFCclock and the reference clock using the Tektronix's MSO64 oscilloscope

RxRECclk jitter < 3 ps RxRECclk phase can be fixed at ~(0)ps precision (by measuring the phase difference between the RxRECclk and the pseudoClock, and resetting the RxRECelk CDR.)

### 6. Status and Future plans

6.1 Proved designs by others TJNAF's 12 GeV upgrade program proved that the dedicated clock distribution and the DAQ (BUSY) feedback are viable 6.2 Pre-prototype RDO is being manufactured

6.3 Prototyne FLX155 (cPIC DAM) is expected this year

6.4 To setup a sub-system DAQ (DAM + RDOs) to fine tune the protocols, to think about GTU prototyping

Authorsel her Jefferson Spinner An-Gotte: Autoreen by Terrerson Science Associates, LLC under U.S. IOE Contract No. DE-AC05-06OR23177. The U.S. Government statistic sequencelusive, paid-tap, irrevocable, world-wide license to ublish or percoduce this manuscript for U.S. Government purposes.

Jetterson Lab mas Jefferson National Accelerator Facility EEE Real Time 2024, Ouv Nhon, Vietnam

💳 Whole detector dead time

RE-START: STOP and START at the same Beam Crossing

MHz) on the DAM (fiber DOWNLINK).

2. Hardware description 2.1 The diagram of ePIC DAQ, Clock /Control

1. Introduction

### 2.2 Hardware description