# **Development of the Low Noise Front-end Electronics for Pulse Voltage Stability Measurement**

#161, 24th IEEE Real Time Conference, Apr. 22 – Apr. 26, 2024. Quy Nhon, Vietnam

Author: Lin Jiang, Haoyan Yang, Tao Xue, Liangjun Wei, Qiutong Pan, Jianmin Li, Yinong Liu

#### Motivation

In order to achieve the stability measurement of 10V high-voltage pulses on an oscilloscope, this paper designs a low-noise front-end electronics to adjust the high-voltage pulse bias to near 0 V, and then uses the oscilloscope to perform measurements at a resolution of 1 mV/div.

## Design of Low Noise Front-end Electronics

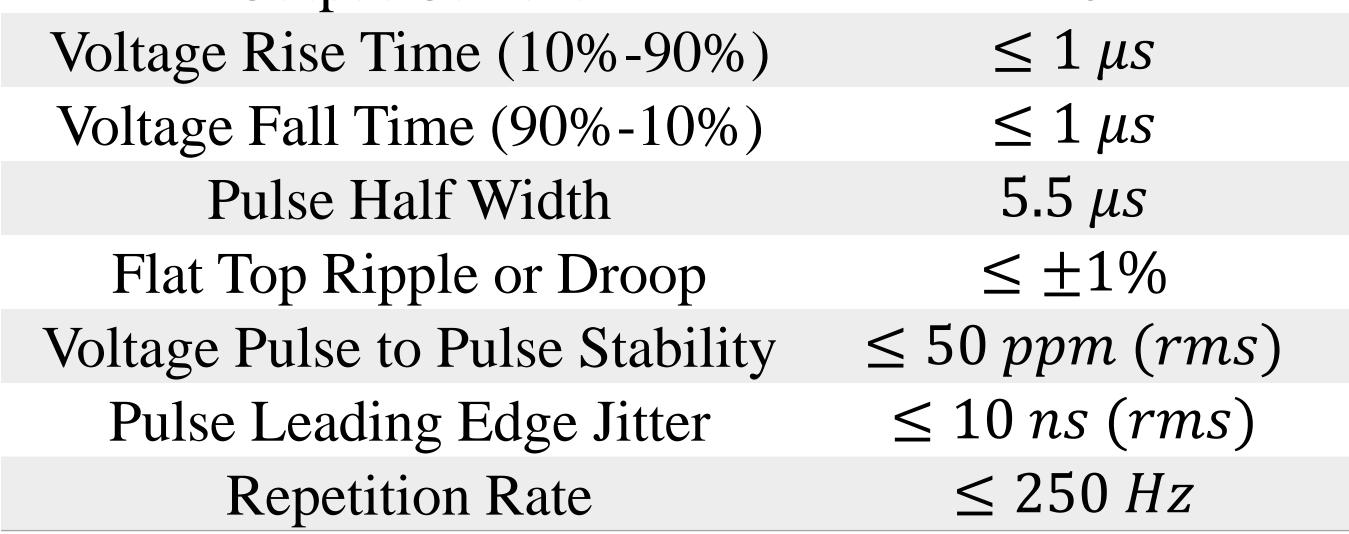

Modulator Specification

| Description    | Result  |

|----------------|---------|

| Output Voltage | -160 kV |

| Output Current | 116 A   |

### Low Noise Front-end Electronics

- > provide a clean 10 V DC voltage

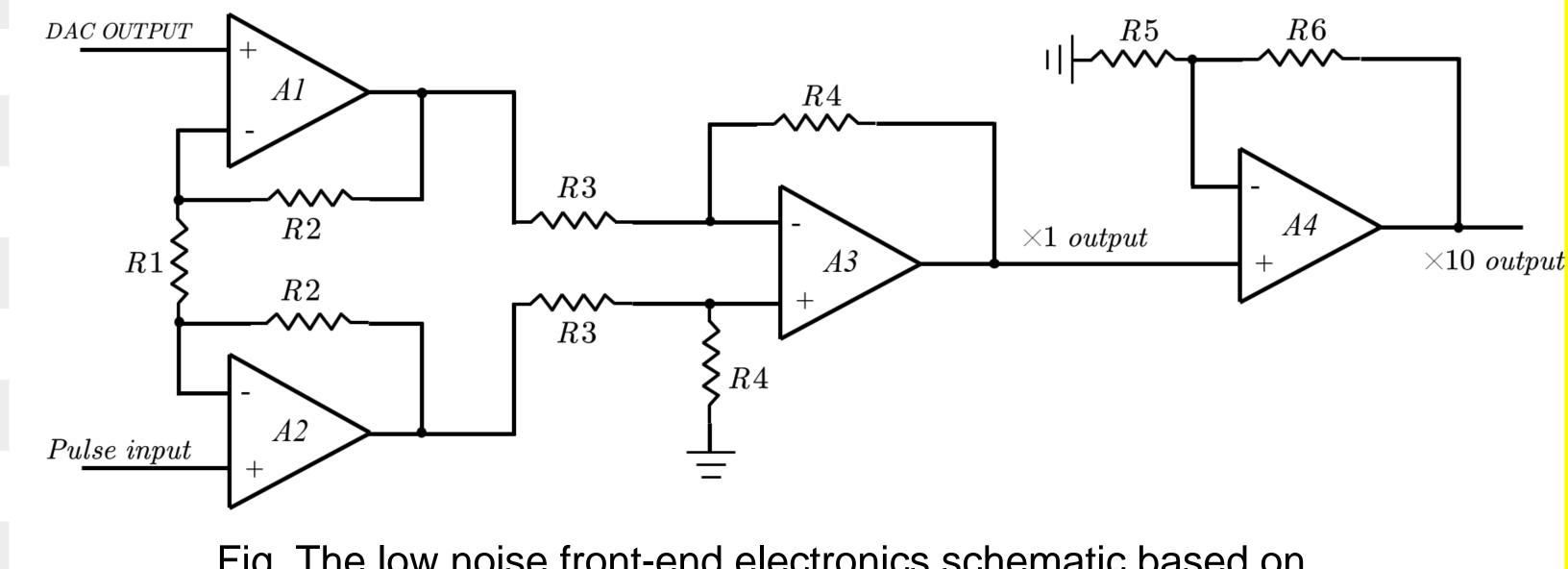

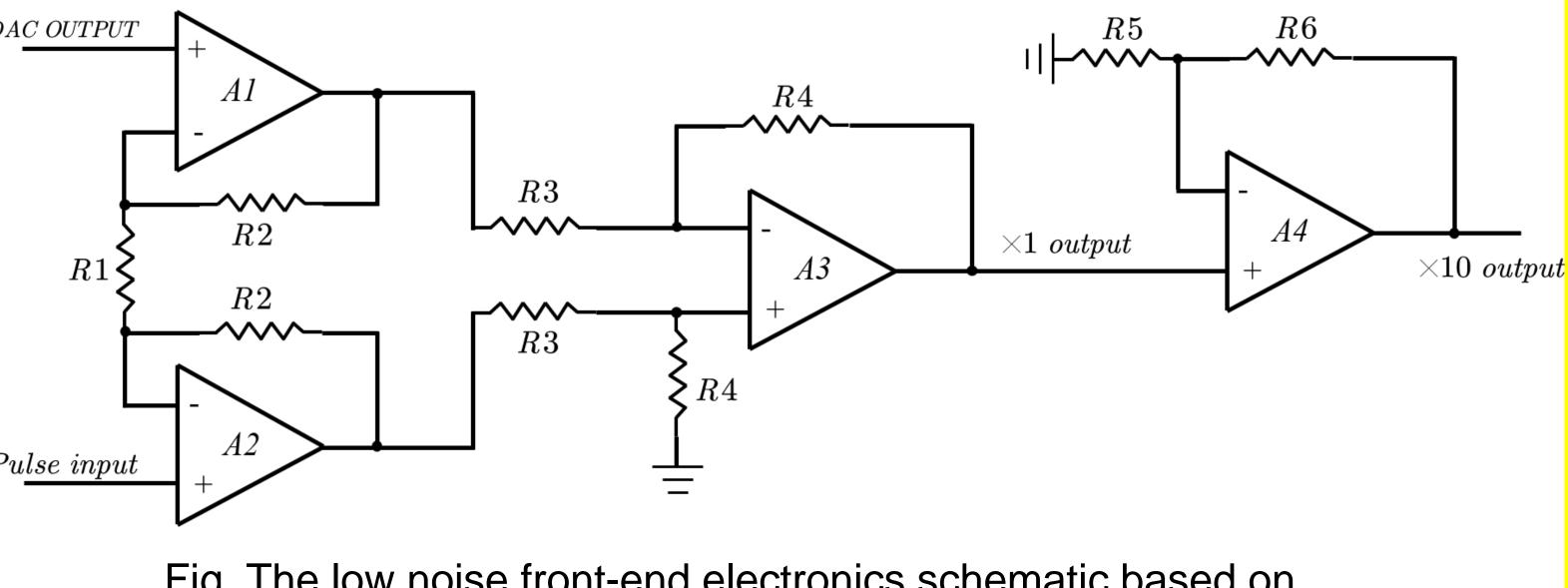

- $\succ$  make a difference with the input 10 V voltage pulse > shift the flat top of the pulse of interest to near 0 V  $\geq$  a discrete three-op-amp instrumentation amplifier

Fig. The low noise front-end electronics schematic based on discrete three op-amp instrumentation amplifier.

### **Circuit Analysis**

The common mode rejection ratio (CMRR) of the discrete instrumentation amplifier

$CMRR = \frac{G \times CMRR_3 \times CMRR_{12}}{G \times CMRR_3 + CMRR_{12}}$

The CMRR of the first stage, where the

### > Improve CMRR

- $\succ$  the parametric matching of the first-stage op amp

- higher first-stage gain

- higher second-stage op amp CMRR

- > second-stage precision matching resistor network

### Noise Reduction

- $\succ$  the output noise spectral density of A1 and A2

- $\succ$  the output noise spectral density of A3

CMRR1 and CMRR2 is the CMRR of amplifier A

$$\begin{array}{l} \text{amplifier A1 and A2, respectively.} \\ CMRR_{12} = \frac{CMRR_1 \times CMRR_2}{CMRR_1 - CMRR_2} \\ \end{array} \quad V_{n1}(rms)^2 = e_{n1}^2 \cdot \left(1 + \frac{2 \cdot R_2}{R_1}\right)^2 + (i_{n1} \cdot R_2)^2 + e_{nR2}^2 + \left(\frac{e_{nR1}}{\sqrt{2}} \cdot \frac{R_2}{R_1}\right)^2 \\ V_{n3}(rms)^2 = \left[e_{n3} \cdot \left(1 + \frac{R_4}{R_3}\right)\right]^2 + 2 \cdot (i_{n3} \cdot R_4)^2 + e_{nR4}^2 + \left(e_{nR3} \cdot \frac{R_4}{R_3}\right)^2 + \left[e_{nR34} \cdot \left(1 + \frac{R_4}{R_3}\right)\right]^2 \\ \end{array}$$

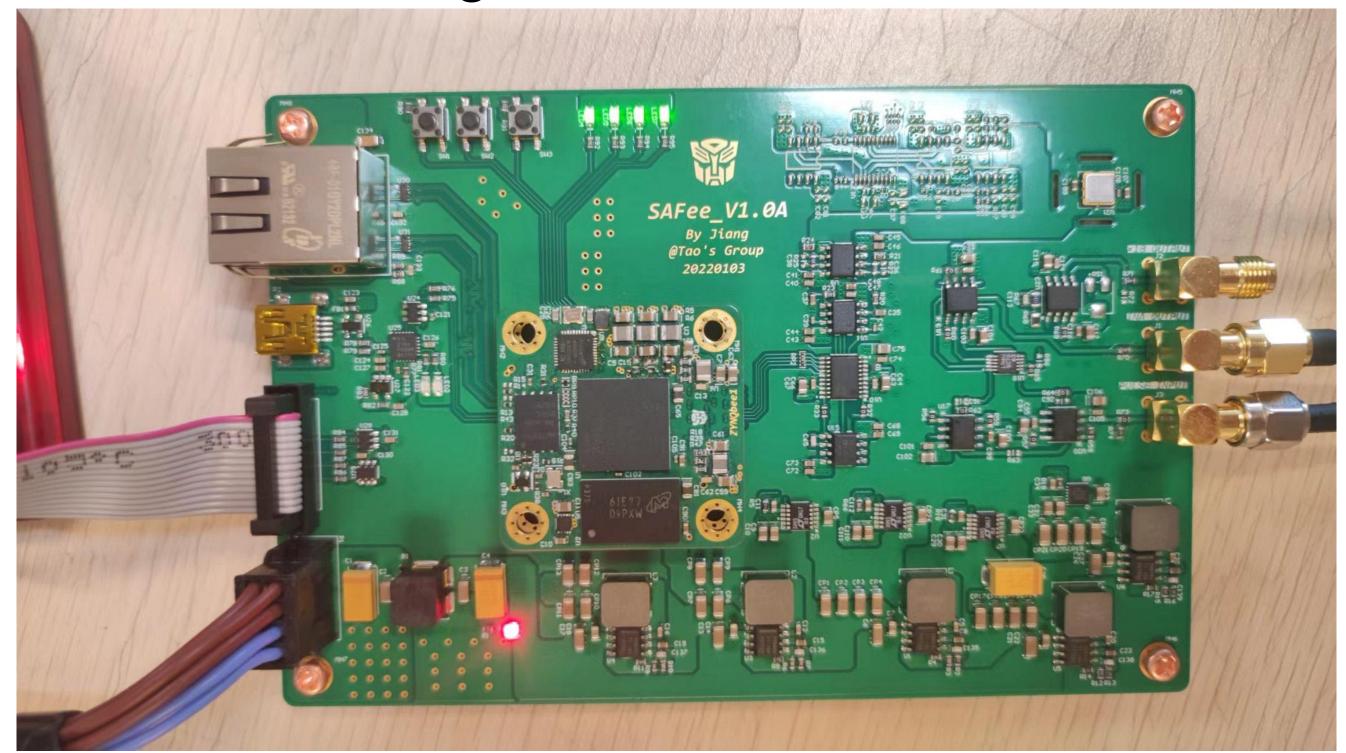

### Hardware Design and Test of SAFee

### Key Component Selection

- > A1, A2and A3: LT6018 from ADI

- Precision matched resistor network: LT5401

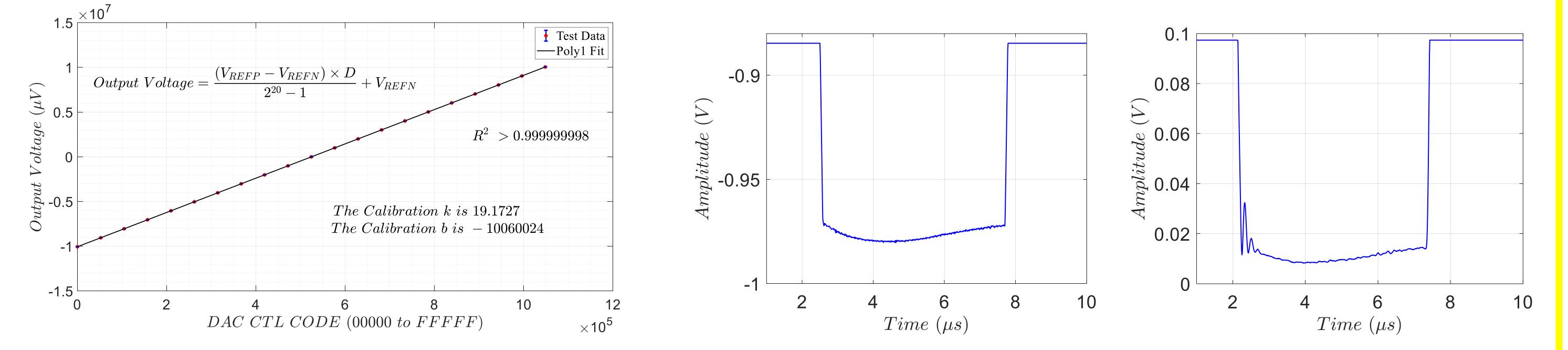

- > DAC: 20-bit AD5791

- ► Reference voltage: LTC6655

- > Buffer Amplifier: AD8676

- Test Result

- $\succ$  Output noise: 150.34  $\pm$  1.13  $\mu V$  RMS

- Supported measurement accuracy: 50 ppm

- ➢ Goodness of linear fit between DAC code and

Lin Jiang, Department of Engineering Physics, Tsinghua University. Email: I-jiang18@mails.tsinghua.edu.cn