# A fast front-end readout design for NICA-MPD shashlik electromagnetic calorimeter Xinchi Ran<sup>1</sup>, Zhi Deng<sup>1,\*</sup>, Fule Li<sup>2</sup>, Tao Xue<sup>1</sup>, Yi Wang<sup>1</sup>, Yi Wang<sup>2</sup>, Qiutong Pan<sup>1</sup>, Lin Jiang<sup>1</sup>, and Haoyan Yang<sup>1</sup>

The 24th IEEE Real Time Conference

<sup>1</sup> Key Laboratory of Particle and Radiation Imaging, Department of Engineering Physics, Tsinghua University, Beijing 100084, China <sup>2</sup> Institute of Integrated Circuit Design and Electronic Design Automation, School of Integrated Circuits, Tsinghua University, Beijing 100084, China \*Correspondence: dengz@mail.tsinghua.edu.cn

### **INTRODUCTION**

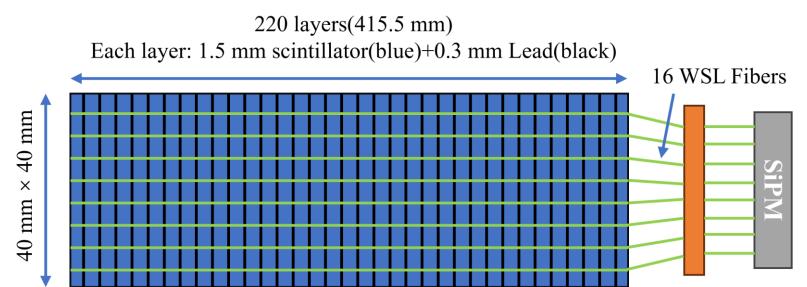

### **□** Electromagnetic Calorimeter (ECal)

- Shashlik sampling structure

- Bremsstrahlung photons collected through optical wavelength shifter (WLS) fibers

- Coupled with Silicon photomultipliers (SiPMs) readout

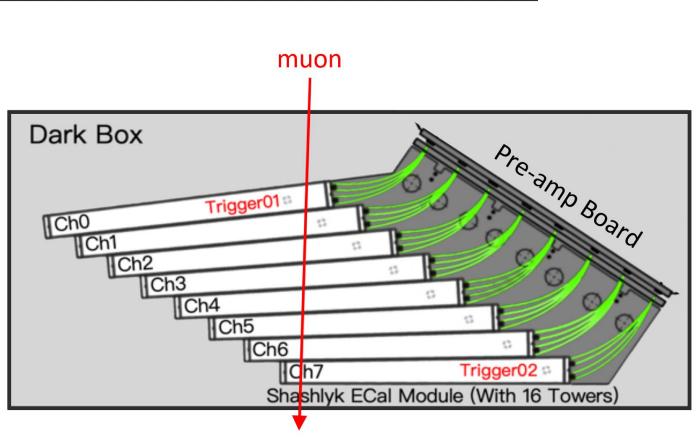

#### **PRELIMINARY TEST**

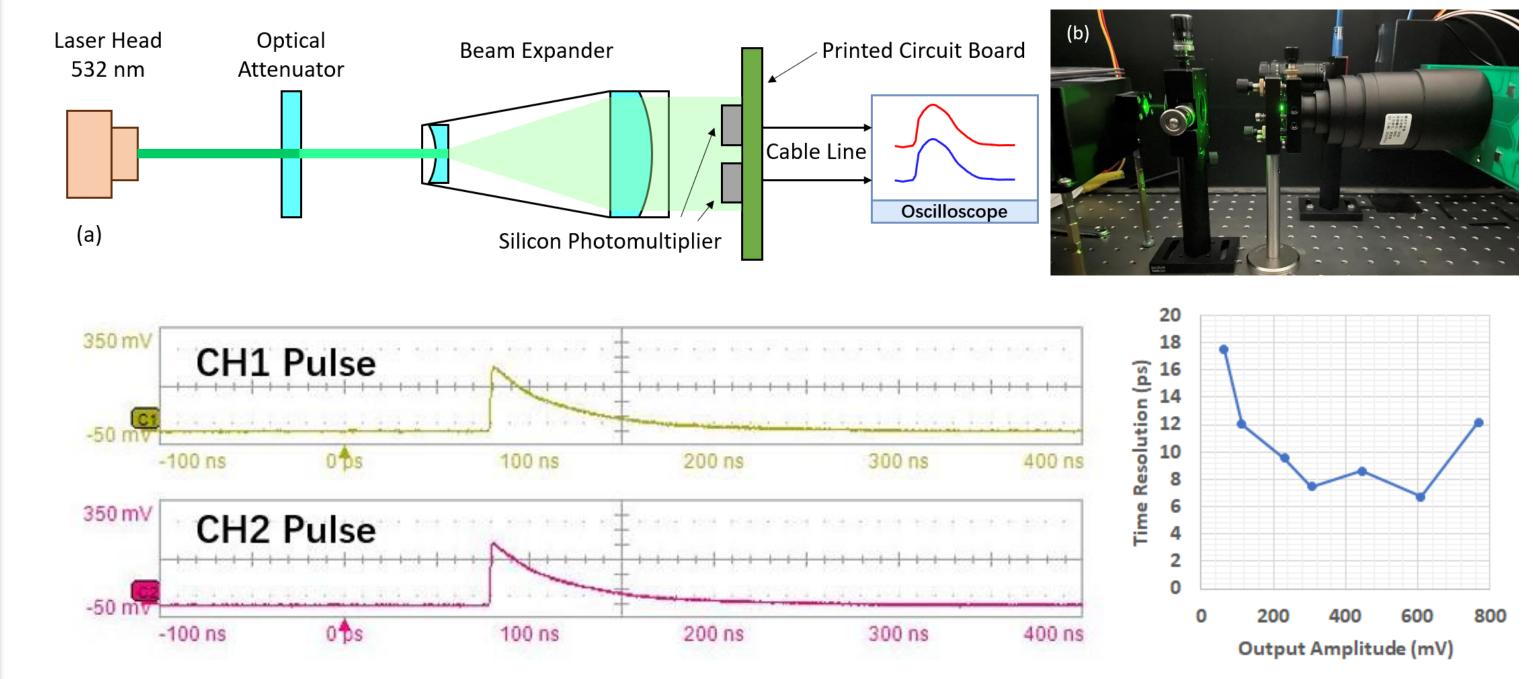

### **□** Laser test for preamplifier

- Signal rise time ~1.4 ns, giving the estimation of an expected bandwidth of roughly 250 MHz

- Single-channel time resolution performance better than 20 ps (samping rate @10GS/s)

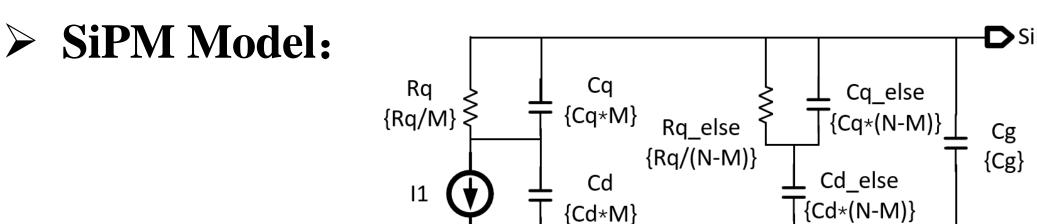

### □ SiPM Readout

- Large terminal capacitance detector (> 100 pF)

- Nonlinear behavior arises with a finite input impedance amplifier

- Readout structure: trans-impedance (TIA) or common-base amplifier

- Unfavored effects: gain peaking and ringing of the output

**READOUT DESIGN**

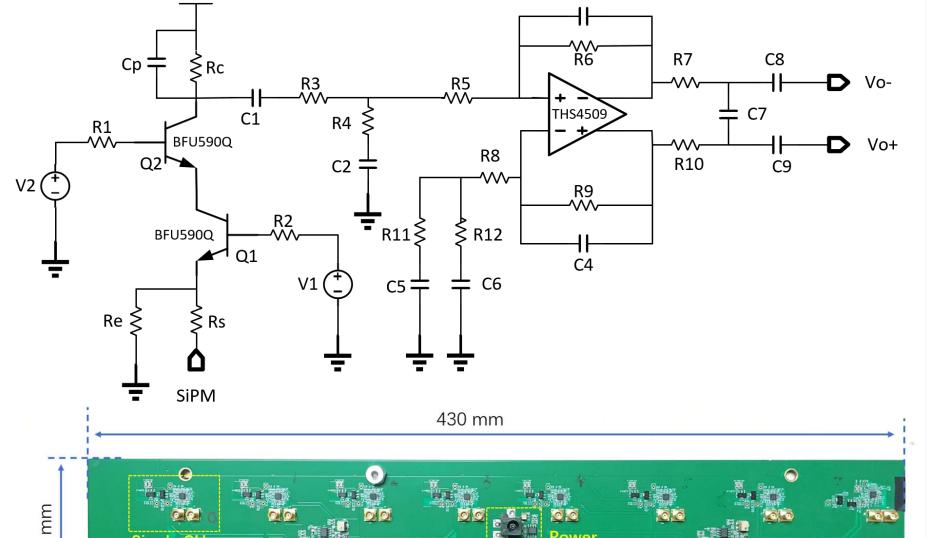

### **D** Preamplifier

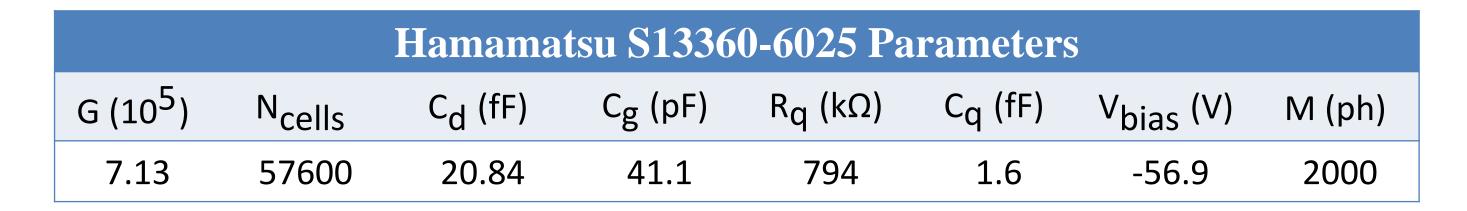

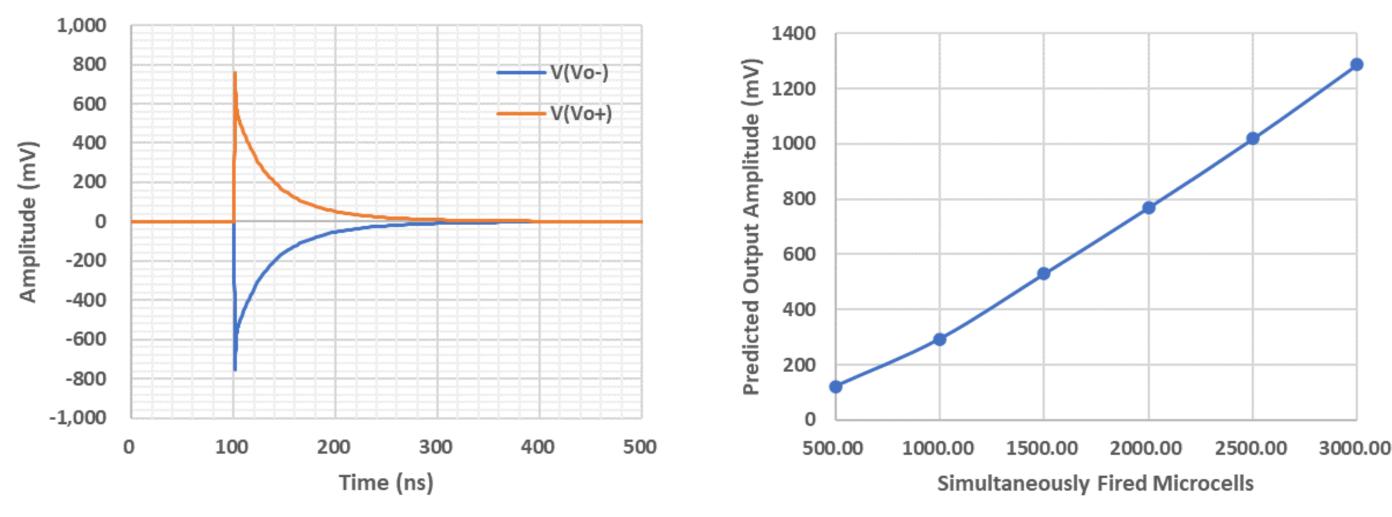

- Detector: Hamamatsu multi-pixel photon counter (MPPC) S13360-6025 (typ. 1280 pF/ch)

- Circuit: a RF transistor current follower with a differential op-amp

- Working scenario: with an incident of 2000 photons, the output is ~750 mV (Vcom), ~1.5 V (Vdiff)

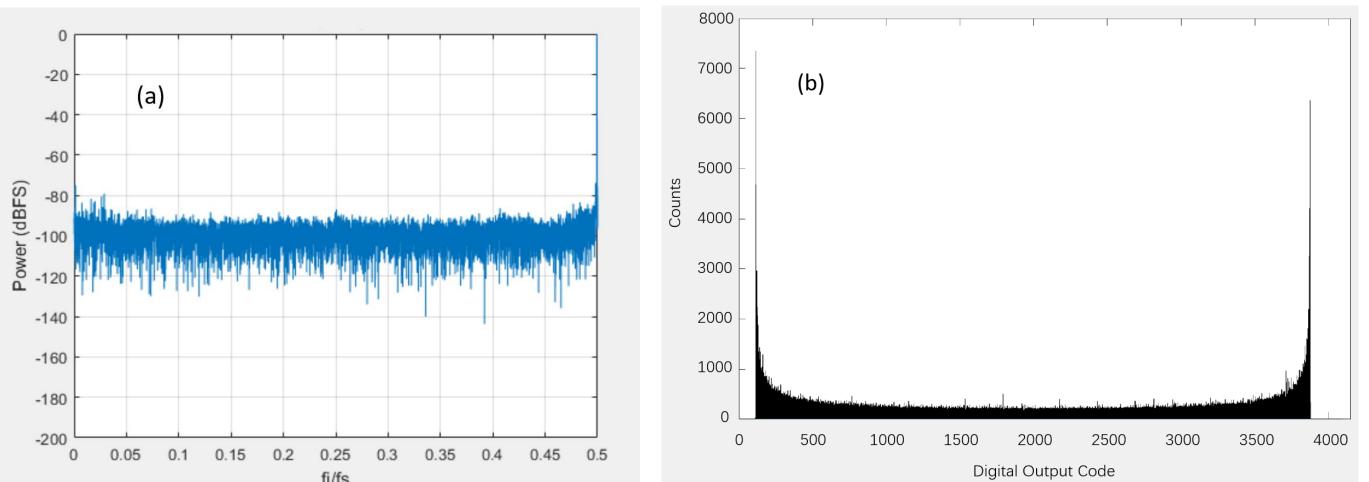

## **Chip test for ADC**

- Maximum sampling rate ~160MHz

- Input a sine wave with a frequency of 80 MHz and an amplitude of -1dBFS, the effective number of bits (ENOB) is 9.34, the spurious-free dynamic range (SFDR) is 73.8 dBc

PCB: 16 channels offers dual outputs  $\mathbb{B}$

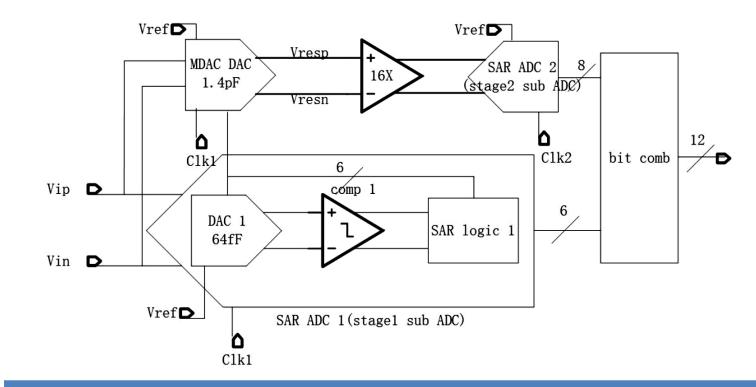

### $\square$ ADC

- 12bit 200MS/s pipeline SAR ADC architecture

- Two-step conversion process (6+7 bits), DAC1 with a smaller capacitance (64fF) while the MDAC DAC (1.4pF)

- A redundancy design is employed to effectively mitigate the Vref buffer requirements

| Main Design Specifications |                |         |                      |                      |

|----------------------------|----------------|---------|----------------------|----------------------|

| Process<br>Technology      | Input<br>Range | Power   | ENOB<br>@fin=100 MHz | SFDR<br>@fin=100 MHz |

| TSMC65nmLP                 | $\pm$ 600 mV   | ≤ 17 mW | ≥ 10 bit             | ≥ 75 dBC             |

-**D**SiPM

{Cg}

1k

0.1 µ 茾

HV (+

### **SPICE SIMULATION**

### **D** Preamplifier SPICE results

Software: LTspice XVII

## **SYSTEM PERFORMANCE TESTING** (PROOF OF CONCEPT)

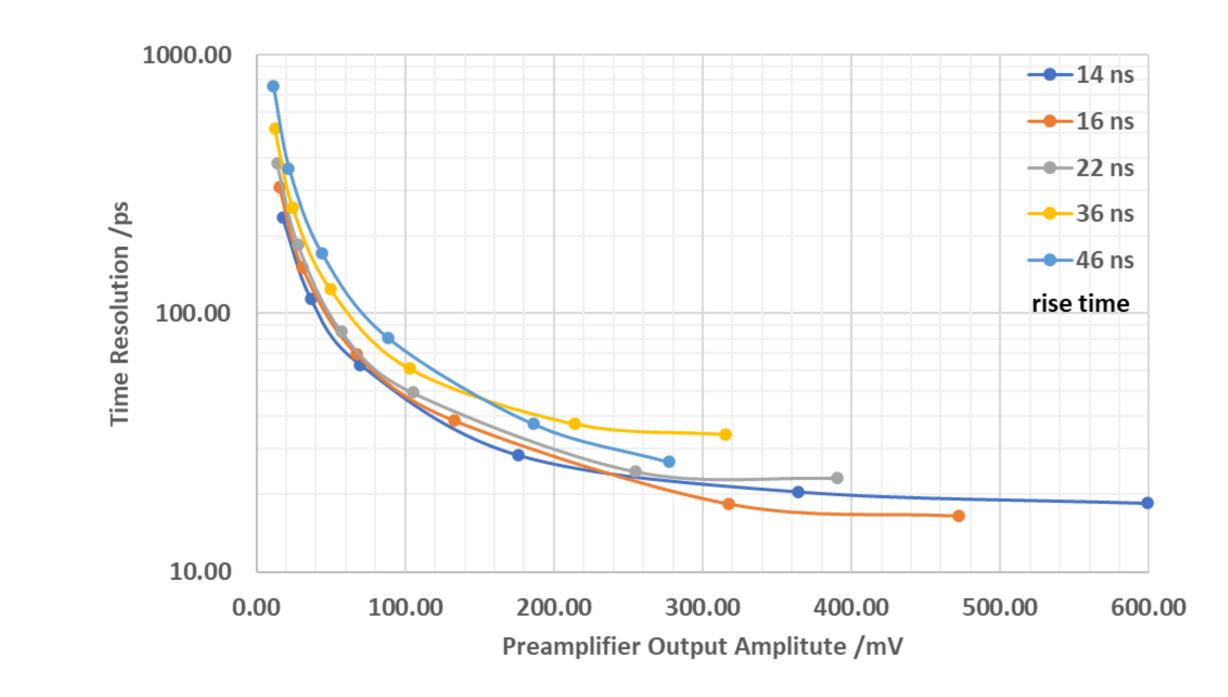

### **□** Electrical test

- > Preliminary system-level time response assessments were performed using an established 14-bit 1 GHz acquisition card (called WRX0608A1, Vpp=1.6 V)

- > Preamplifier configuration was changed for different output rise time test

- > A square wave signal was generated by an arbitrary function generator (Tektronix AFG3102C)

- Data processing includes sparse sampling, with an equivalent sampling rate of 200 MHz

- ➤ Waveforms with 3~4 sampling points (rise time at 15~20 ns for 200 MHz sampling rate) on the rising edge has better time resolution ~20 ps (@output  $\geq$ 250mV)

#### > Preamplifier SPICE results:

SUMMARY

- > A fast front-end readout design was designed and developed. The prototype preamplifier and ADC chip performance were evaluated.

- > Preliminary system time response assessments were performed. Verification had shown that good time resolution performance can still be achieved at low sampling rates (200MHz).