Stefan Ritt :: Head of Muon Physics Group :: Paul Scherrer Institute

Mastering Picosecond Precision: Lessons learned from Large-Scale Timing Systems

IEEE NPSS Real Time Conference, Qui Nhon, Vietnam, April 26, 2024

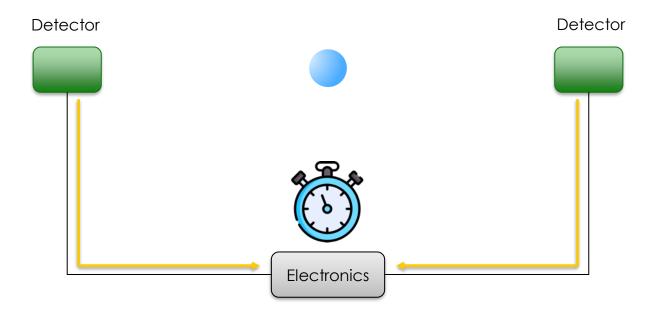

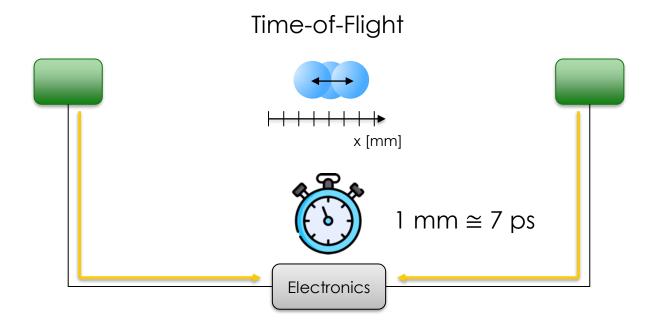

### Measuring precision timing

### Measuring precision timing

# Two particle decay Different Time

### Measuring precision timing

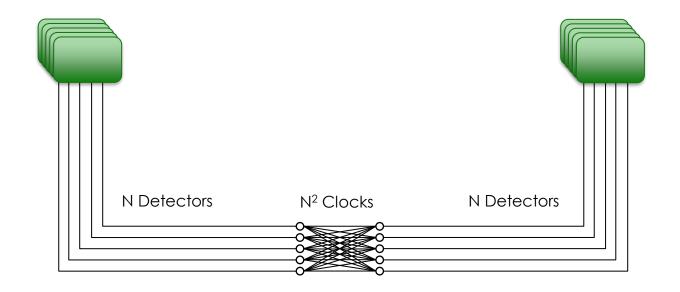

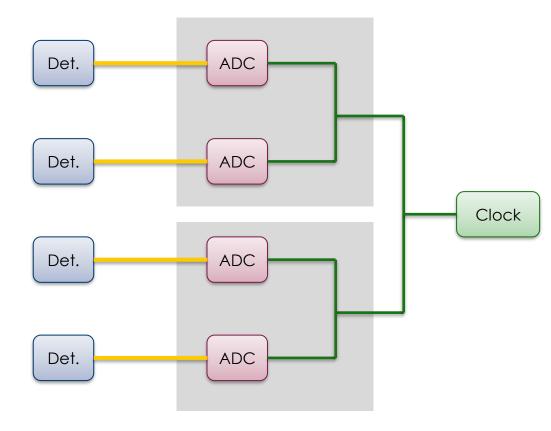

### Large systems

N=1000 → 1,000,000 Clocks

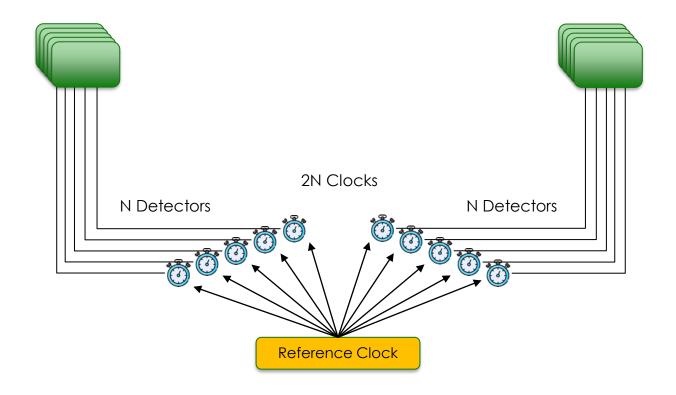

### Large systems with reference clock

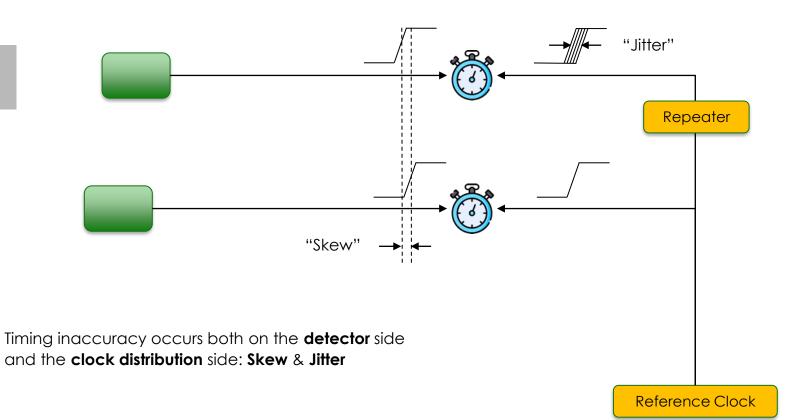

### Time inaccuracy

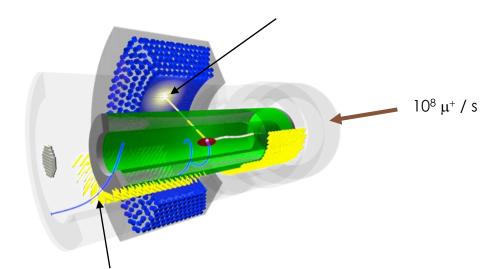

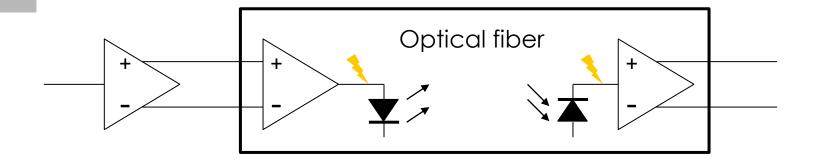

### MEG II Experiment at PSI

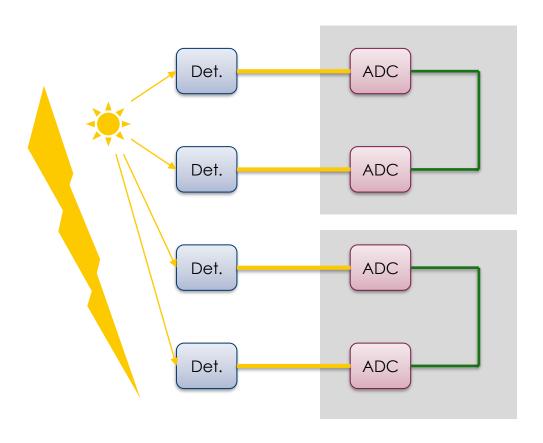

$\gamma$  detection in liquid Xenon Calorimeter: 4760 channels

Normal  $\mu$  decay (Standard Model):

$$\mu^+ \rightarrow e^+ \nu_e \nu_\mu$$

Lepton-Flavor Violating Decay (New Physics):

$$\mu^+ \rightarrow e^+ \gamma$$

e<sup>+</sup> detection in Timing Counter: 1024 channels

MEG II Experiment requires

~10 ps at electronics level

### How to achieve timing at the Pico second level?

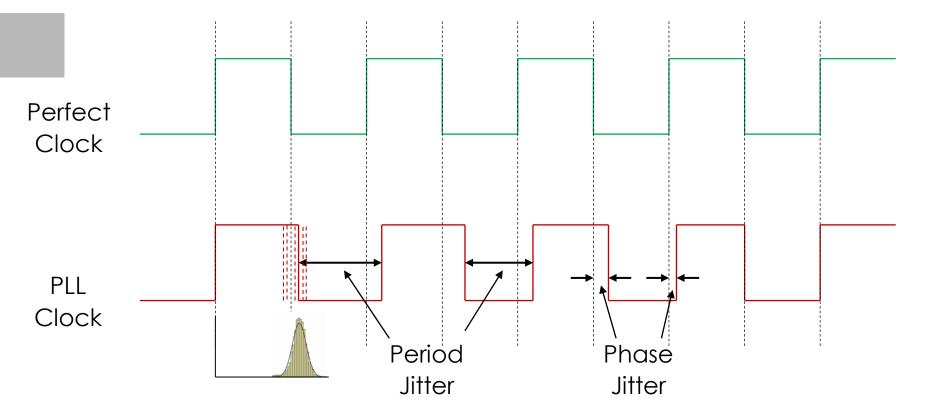

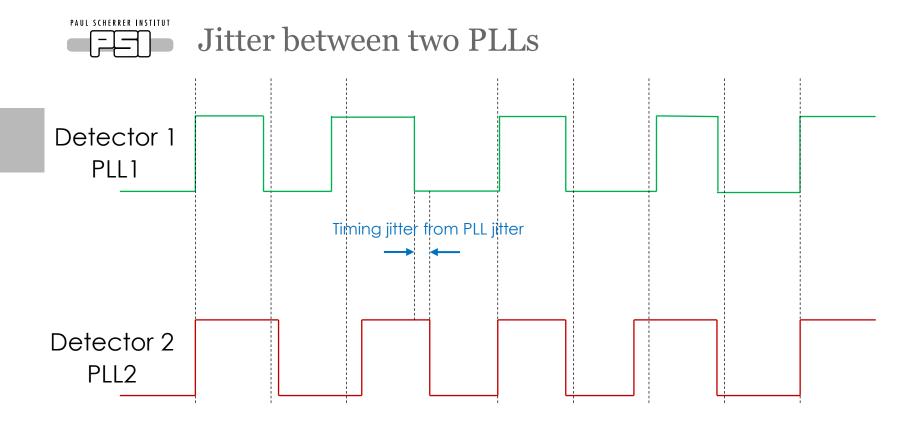

- Sources of timing jitter: Single ended lines, PLL jitter

- Clock stability

- Noise reduction strategies

- Timing calibration

- Lessons learned from the MEG II system

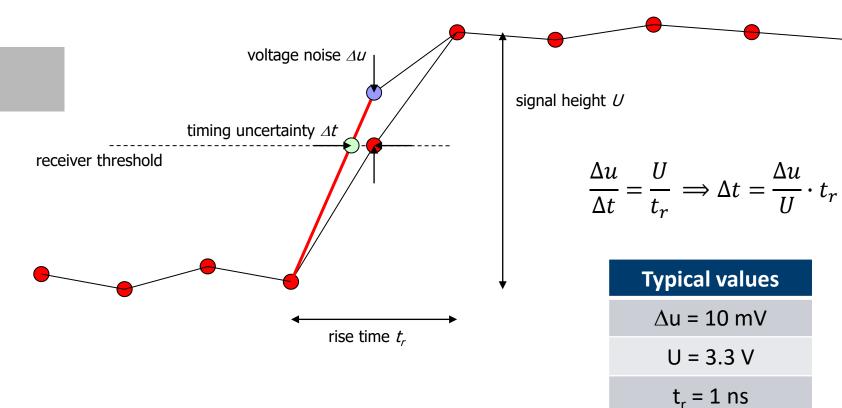

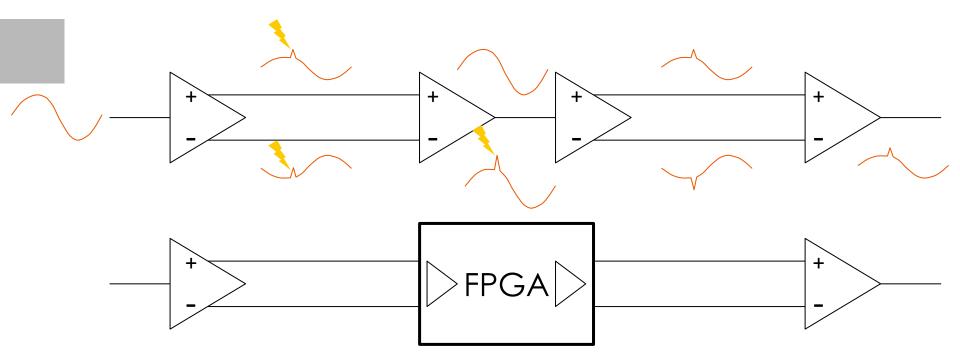

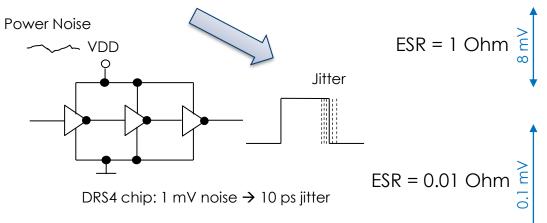

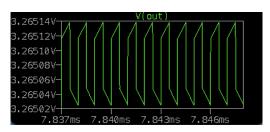

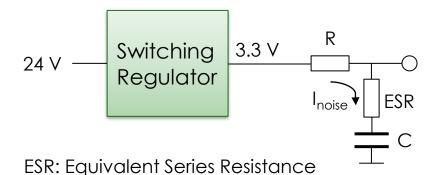

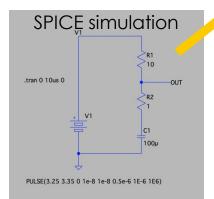

### Jitter caused by voltage noise

5 Jan 2024 Page 10

$\Delta t = 3 ps$

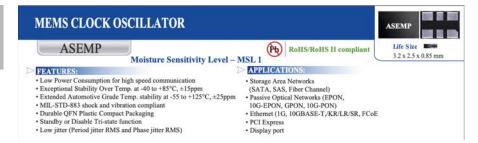

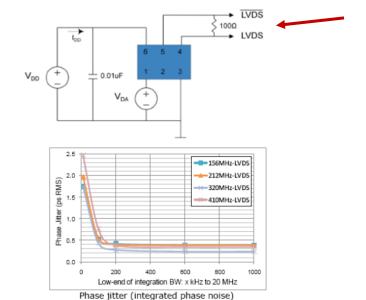

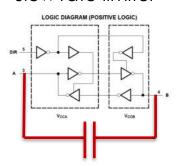

### Differential Signals e.g. LVDS

Do not send low-jitter clocks through FPGAs!

Careful with optical clock distribution!

### Clock stability

- GPS clock for measurements far apart

- Atomic clock for long term measurements

- Particle physics:

Measurement periods O(10 ns)

- $\rightarrow$  Frequency stability of **10-4** is enough 10 ns \* 10-4 = 1 ps

- → Excellent **low-jitter** clock distribution to all detector channels needed

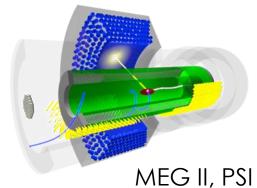

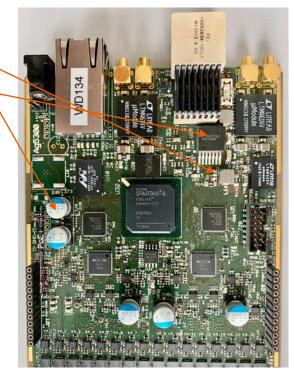

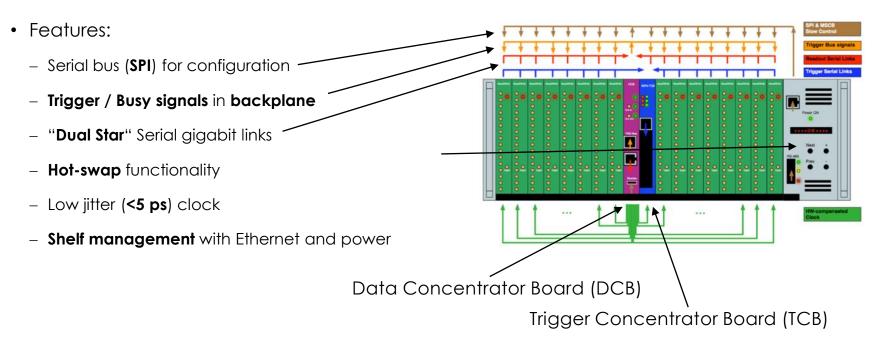

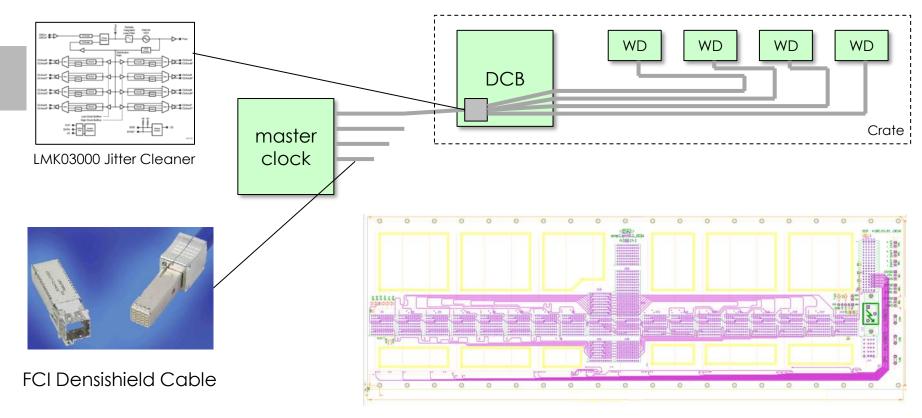

### WaveDAQ system for MEG II @ PSI

WaveDAQ Crate

9000+ channels 5 GSPS / 12 bit

2 May 2023 Page 14

### Low-jitter quartz

Common Key Electrical Specifications – CMOS, LVPECL, LVDS, and HCSL

Parameters Minimum Typical Maximum

| Parameters                           |        | Minimum Typical                |                                | Maximum       | Units      | Notes                                                                          |  |  |

|--------------------------------------|--------|--------------------------------|--------------------------------|---------------|------------|--------------------------------------------------------------------------------|--|--|

|                                      | CMOS   | 2.3000* 170.000                |                                | 170.0000      |            | -20 ~ +70°C<br>-40 ~ +85°C                                                     |  |  |

|                                      | CMOS   | 3.3000*                        |                                | 170.0000      |            | -40 ~ +105 °C<br>-55 ~ +125 °C                                                 |  |  |

| Frequency Range                      | LVPECL | 2.3000*                        |                                | 460.0000      | MHz        | Commercial, Industrial<br>temp. range<br>Commercial, Industrial<br>temp. range |  |  |

|                                      | LVDS   | 2.3000*                        |                                | 460.0000      |            |                                                                                |  |  |

|                                      | HCSL   | 2.3000*                        |                                | 460.0000      |            | Commercial, Industrial temp. range                                             |  |  |

| Operating Temperature                |        | -20                            |                                | +70           | °C         | See options                                                                    |  |  |

| Storage Temperature                  |        | -55                            |                                | +150          | °C         |                                                                                |  |  |

| Overall Frequency Stability          |        | -50                            |                                | +50           | ppm        | See options                                                                    |  |  |

| Supply Voltage (Vdd)                 |        | +2.25                          |                                | +3.6          | V          |                                                                                |  |  |

| Startup Time                         |        |                                |                                | 5             | ms         |                                                                                |  |  |

| Enable Time                          |        |                                |                                | 20            | ns         | STD (Tri-state)                                                                |  |  |

|                                      |        |                                |                                | 5             | ms         | PD option (Power Down)                                                         |  |  |

| Disable Time                         |        |                                |                                | 5             | ns         |                                                                                |  |  |

| Disable Current                      |        |                                | 20                             | 22            | mA         | STD (Tri-state)                                                                |  |  |

|                                      |        |                                |                                | 0.095         | IIIA       | PD option (Power Down)                                                         |  |  |

| Tri-state Function (Standby/Disable) |        | "1" (VIH≥0.75<br>"0" (VIL<0.25 | *Vdd) or Open:<br>*Vdd) : Hi Z | Oscillation V |            | 40kΩ pull-up resister embedded                                                 |  |  |

| Aging                                | -5.0   |                                | +5.0                           | ppm           | First year |                                                                                |  |  |

#### Key Electrical Specifications - LVDS

| Parameters                        |     | Minimum | Typical | Maximum | Units                       | Notes                        |

|-----------------------------------|-----|---------|---------|---------|-----------------------------|------------------------------|

| Supply Current (I <sub>dd</sub> ) |     |         | 29      | 32      | mA                          | RL=100Ω                      |

| Output Offset Voltage (Vos)       |     | 1.125   |         | 1.4     | V                           | RL=100Ω differential         |

| Delta Offset Voltage (ΔVos)       |     |         |         | 50      | mV                          |                              |

| Peak to Peak Output Swing (V      | po) |         | 350     |         | mV                          | Single ended                 |

| Rise Time                         | Tr  |         | 200     |         |                             | RL=50Ω, CL=2pF               |

| Fall Time                         | Tf  |         | 200     |         | ps                          | 20% to 80%                   |

| Duty Cycle                        |     | 48      |         | 52      | %                           | Differential                 |

|                                   |     |         | 0.28    | 2       |                             | 200kHz ~ 20MHz<br>@156.25MHz |

| Integrated Phase Jitter (JPH)     |     |         | 0.40    | 2       | ps                          | 100kHz ~ 20MHz<br>@156.25MHz |

|                                   |     | 1.70    | 2       |         | 12kHz ~ 20MHz<br>@156.25MHz |                              |

| Period Jitter RMS (JPER)          |     |         | 2.5     |         | ps                          |                              |

### LVDS clock distribution

CDCLVD110A

SCAS841D - FEBRUARY 2007-REVISED DECEMBER 2016

#### CDCLVD110A Programmable Low-Voltage 1:10 LVDS Clock Driver

#### 1 Features

- Low-Output Skew <30 ps (Typical) for Clock-Distribution Applications

- Distributes One Differential Clock Input to 10 LVDS Differential Clock Outputs

- V<sub>CC</sub> Range: 2.5 V ±5%

- Typical Signaling Rate Capability of Up to 1.1 GHz

- Configurable Register (SI/CK) Individually Enables Disables Outputs, Selectable CLK0, CLK0 or CLK1, CLK1 Inputs

- · Full Rail-to-Rail Common-Mode Input Range

- · Receiver Input Threshold: ±100 mV

- · Available in 32-Pin LQFP and VQFN Package

- Fail-Safe I/O-Pins for V<sub>DD</sub> = 0 V (Power Down)

#### 3 Description

The CDCLVD110A clock driver distributes one pair of differential LVDS clock inputs (either CLK0 or CLK1) to 10 pairs of differential clock outputs (Q0 to Q9) with minimum skew for clock distribution. The CDCLVD110A is specifically designed to drive  $50\text{-}\Omega$  transmission lines.

When the control enable is high (EN = 1), the 10 differential outputs are programmable in that each output can be individually enabled or disabled (3-stated) according to the first 10 bits loaded into the shift register. Once the shift register is loaded, the last bit selects either CLK0 or CLK1 as the clock input. However, when EN = 0, the outputs are not programmable and all outputs are enabled.

The CDCLVD110A has an improved start-up circuit that minimizes enabling time in AC- and DC-coupled systems

### fully CLK\_SEL differential CLK<sub>0</sub> CLK<sub>0</sub> Mux CLK1 CLK1

#### 6.7 Jitter Characteristics

characterized with CDCLVD110 performance EVM,  $V_{DD}$  = 3.3 V, outputs not under test are tell otherwise noted)

| PARAMETER                                                                                                                    |                                               | TEST CONDITIONS                              | MIN | TYP | MAX   | UNIT   |

|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------|-----|-----|-------|--------|

| $t_{\text{jitterLVDS}} \  \   \text{Additive phase jitter from input to} \\ \text{LVDS output Q3 and } \overline{\text{Q3}}$ | 12 kHz to 5 MHz, f <sub>out</sub> = 30.72 MHz |                                              | 281 |     | fo ma |        |

|                                                                                                                              | LVDS output Q3 and $\overline{\text{Q3}}$     | 12 kHz to 20 MHz, f <sub>out</sub> = 125 MHz |     | 111 |       | fs rms |

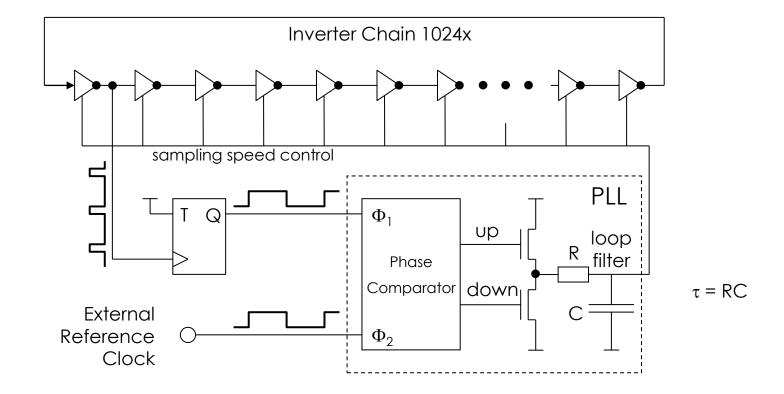

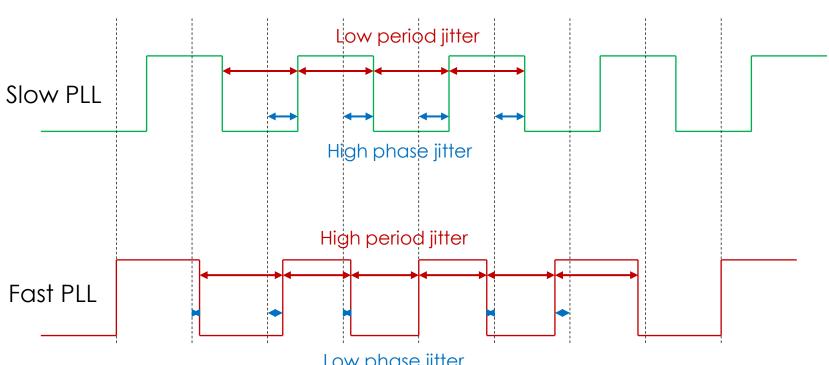

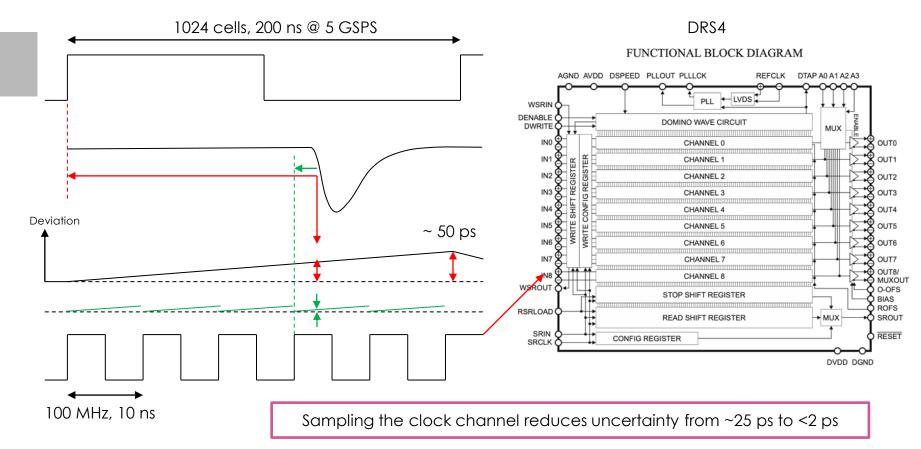

### DRS4 Phase Locked Loop

Low phase jitter

To achieve minimal timing jitter, PLL phase jitter must be minimized

### PLL jitter from power supply noise

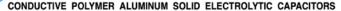

Use **low-ESR** capacitors for power supply filtering

### Used filter components

nichicon

- Ultra-low ESR, Higher Capacitance, High ripple current. . Load life of 2000 hours at 105°C.

- SMD type : Lead free reflow soldering condition at 260°C peak

- Compliant to the RoHS directive (2002/95/EC).

#### ■Standard Ratings

| Rated Voltage<br>(V)(code) | Surge Voltage<br>(V) | Rated Capacitance<br>(μF) | Case Size | tan 8 | Leakage Current<br>(μA) | ESR (mΩ)<br>(at 100kHz 20°C) | Rated Ripple<br>(mArms) | Part Number    |

|----------------------------|----------------------|---------------------------|-----------|-------|-------------------------|------------------------------|-------------------------|----------------|

|                            |                      | 390                       | 6.3 × 6   | 0.12  | 293                     | 10                           | 3900                    | PCK0E391MCO1GS |

| 2.5<br>(0E) 2.8            | 560                  | 8 × 7                     | 0.12      | 420   | 9                       | 4500                         | PCK0E561MCO1GS          |                |

|                            | 680                  | 8 × 7                     | 0.12      | 510   | 9                       | 4500                         | PCK0E681MCO1GS          |                |

|                            | 1200                 | 10 × 8                    | 0.12      | 900   | 9                       | 5000                         | PCK0E122MCO1GS          |                |

|                            |                      | 2200                      | 10 × 10   | 0.12  | 1650                    | 8                            | 6000                    | PCK0E222MCO1GS |

$560 \, \mu F / 9 \, m\Omega$

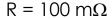

#### LC combines EMI Suppressor Filter NFE31PT222Z1E9

Insertion Loss Characteristics

Equivalent Circuit

5 Jan 2024

Page 22

#### PAUL SCHERRER INSTITUT

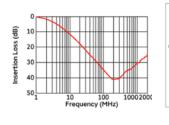

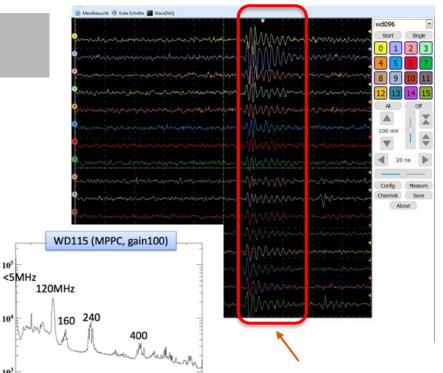

### Power section WaveDREAM board

### Electromagnetic Interference (EMI)

Frequency [MHz]

#### Shielding

#### Slew rate limiter

EMI pulse from switching converter

### Use of DRS4 clock channel

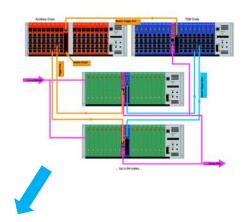

## The WaveDAQ system

### Custom Design "WaveDAQ"

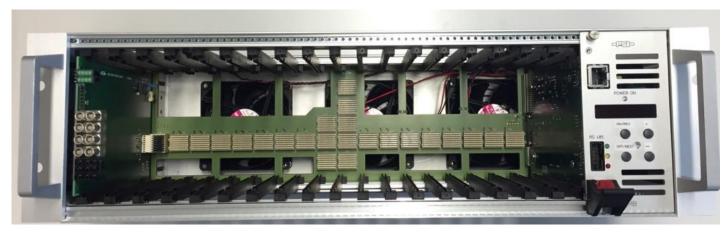

- Standard 19" crate + custom backplane (no VME, no xTCA)

- Idea: Not only a solution for MEG II, but more general "crate standard"

### WaveDAQ Backplane

### Half Height Backplane

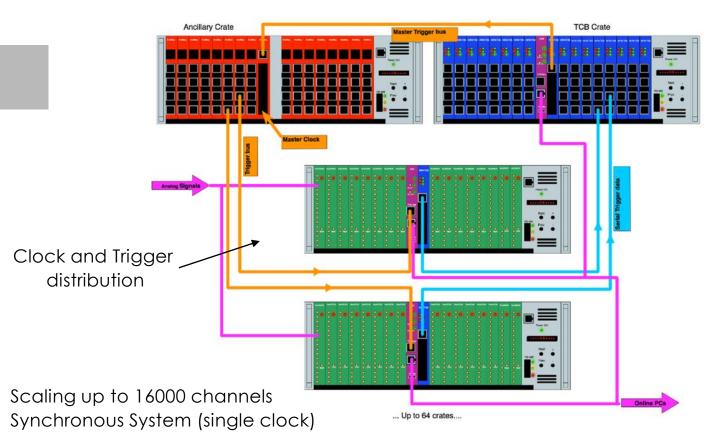

### MEG II System

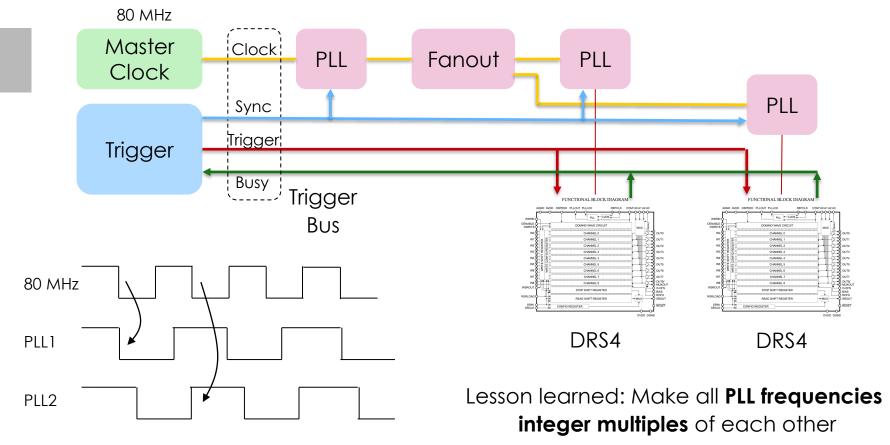

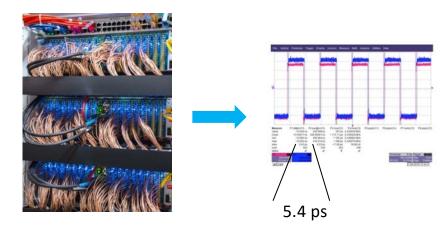

### Synchronization

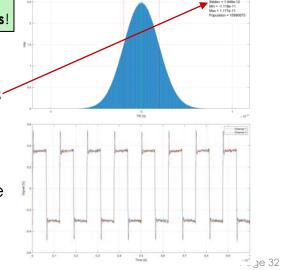

### Jitter measurements

courtesy E. Schmidt, PSI

| Filename<br>+ ToDo                                                                                          | Signal Probe<br>Location | Signal                                    | Ref Probe<br>Location | Ref Signal                                | Jitter<br>Std Dev | Jitter<br>Min | Jitter<br>Max | Tektronix MSO64B                          |

|-------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------|-----------------------|-------------------------------------------|-------------------|---------------|---------------|-------------------------------------------|

| 27_4_Crate190_AnbDistIn_vs_3_DcbDistIn Switch scope to refcik setup.                                        | 4                        | ANB<br>Distributor<br>Input<br>(Soldered) | 3                     | DCB<br>Distributor<br>Input<br>(Soldered) | 10.8 ps           | -63.7 ps      | 53.2 ps       | 8 GHz, 50 GSPS soldered diff. probe       |

| 28_7_Crate196_DcbDistln_vs_Crate192_DcbDistln  Solder 2 Probes to DCB02/DCB07 distributor input from Cable. | 7<br>Crate196            | DCB<br>Distributor<br>Input<br>(Soldered) | 7<br>Crate192         | DCB<br>Distributor<br>Input<br>(Soldered) | 7.3 ps            | -39.7 ps      | 45.5 ps       | soldered dill. probe                      |

| 29_7_Crate196_DcbDistIn_vs_ScopeRef  Switch to scope reference setup.                                       | 7                        | DCB<br>Distributor<br>Input<br>(Soldered) | None                  | Scope<br>Constant<br>Clock                | 3.9 ps            | -23.4 ps      | 31.0 ps       | a - 1 9 ps                                |

| 30_9_Crate196_Slot15WdbLmkin_vs_ScopeRef Solder 2 Probes to 2 WDB280/WDB317 LMK inputs.                     | 9                        | WDB<br>LMK<br>Input<br>(Soldered)         | None                  | Scope<br>Constant<br>Clock                | 2.0 ps            | -10.9 ps      | 12.3 ps       | $\sigma_{\text{jitter}} = 1.9 \text{ ps}$ |

| 31_9_Crate196_Slot15WdbLmkin_vs_Slot1WdbLmkin Switch scope to refcik setup.                                 | 9<br>Slot15              | WDB<br>LMK<br>Input<br>(Soldered)         | 9<br>Slot1            | WDB<br>LMK<br>Input<br>(Soldered)         | 1.9 ps            | -11.1 ps      | 11.8 ps       | Slot - Slot                               |

| 32_9_Crate196_Slot15WdbLmkin_vs_Crate192_Slot15WdbLmkin                                                     | 9<br>Crate196            | WDB<br>LMK<br>Input<br>(Soldered)         | 9<br>Crate192         | WDB<br>LMK<br>Input<br>(Soldered)         | 3.0 ps            | -16.4 ps      | 16.8 ps       | Crate - Crate                             |

### Global calibration

- Clock distribution is never perfect to the ps level

- Global sync injection at ADC does not calibrate different cable lengths

- Signal injection at detector can be difficult

### Global calibration

**Solution**: Use a **physics event** which is seen by all detectors:

- LED flash in calorimeter

- Cosmic traversing many channels

- Correct for different light path

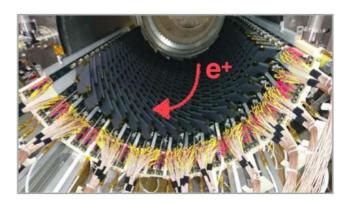

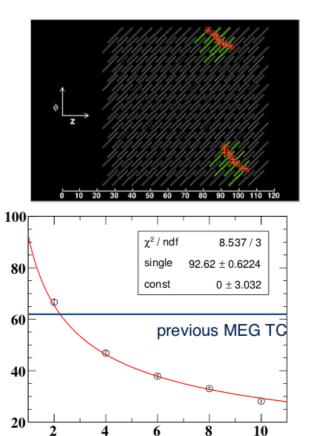

### MEG II Timing Counter

- $8 \times 10^8 \,\mu/s$

- 256 scintillating tiles 4x6 cm,

512 WDB channels (2 crates)

- Resolution scales with sqrt(N)

- 35 ps reached with 8 hits

5 Jan 2024 Page 35

Resolution (ps)

### Lessons learned (so far...)

- Designing a **crate standard** is **easier** than anticipated (if no committee is involved (a))

- Distributing a 5 ps jitter clock is not so hard

- Doing everything from scratch can simplify things

- shelf manager with 8-bit uC with few 100 lines of code

- crate costs ~ 2k\$ including power supply

- Mixed signal board with 40 μV of noise (gain=100!) is tough

- whole project took 6 years from first idea with ~2 FTE

- analog front-end took 1.5 years, FW ~2 years

- careful selecting and shielding

DC-DC converter, needed 4 revisions

- the more noise you fix, the more new sources you find

- Lots of experience obtained often missing in textbooks

### Conclusions for precision timing in large systems

- Use end-to-end differential clock distribution

- Careful filter power for all PLLs with low-ESR capacitors

- Identify and remove EMI sources

- Large systems with<5 ps timing can be built</li>

- This talk:

IEEE NPSS Educational Video at https://ieee-npss.org/videos/

5 Jan 2024