#### 1<sup>st</sup> CERN Baltic Conference (CBC 2021) June 28, 2021

#### **Test System HW/SW for LHC Data Links** and Other Projects Done for CERN and ESS Artur Jutman

#### **Inventor of Embedded Virtual Instruments**

# Solutions in 20+ countries

(🔅

Patented in 2013

# Testonica

### **Testing Right From the Inside**

nstruments

At Speed. Always.

Tester

on Chip

<u>+</u> + |+ ||

$\bigcirc$

Testonica

#### We Invest In R&D and Support The Community

Academic **Collaboration**

.....

Testonica

**Coordinating EU R&D** projects

**Jobs for PhD Students**

• Publishing

.....

()

Conference **Sponsorship**

#### **Presentation Outline**

#### Custom BERT Equipment – 2011

• Tau lepton decay triggering algorithm – 2020

Control System

Testonica

In collaboration with **TECH**

$\langle \diamondsuit$

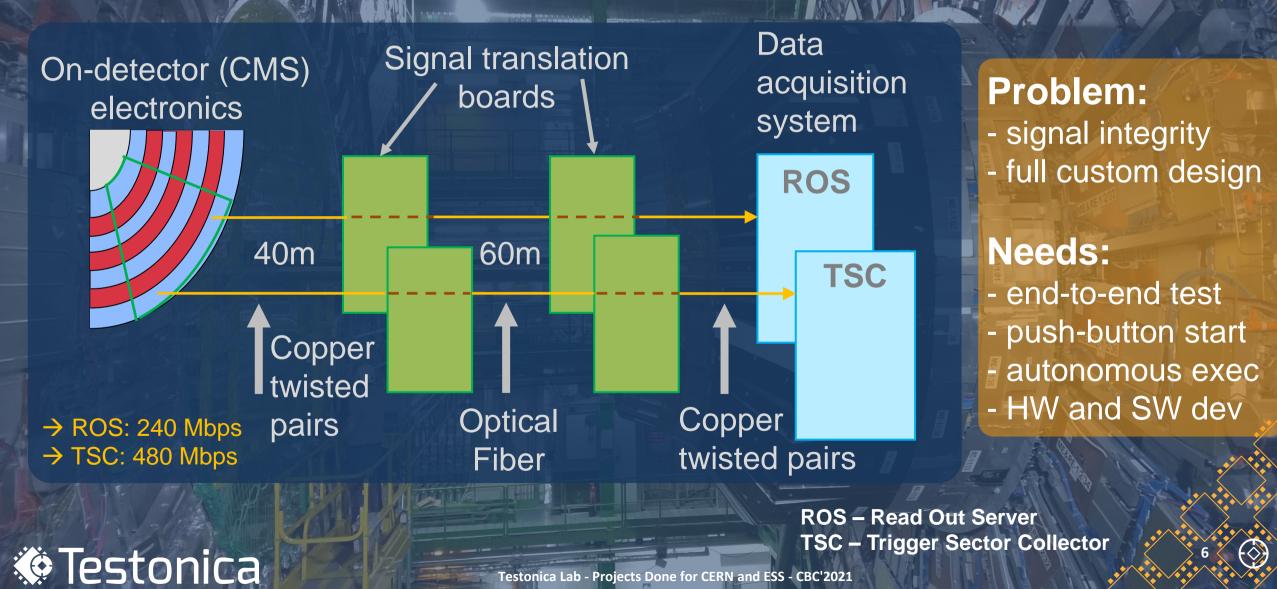

### **CMS Data Links**

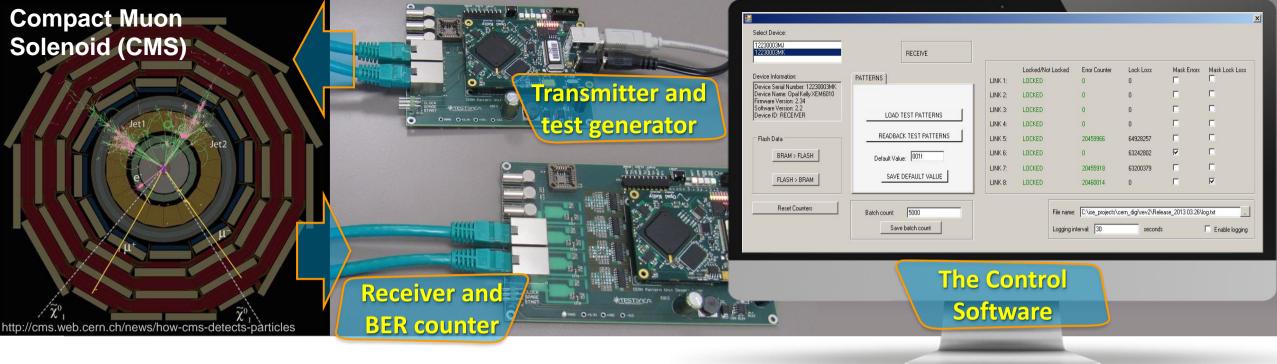

#### **Delivered: Custom BERT Equipment**

- System Under Test: communication channels of LHC/CMS

- Delivered: custom Bit Error Rate (BER) Test Equipment on FPGA

- Usage: test and certification of communication channels of LHC/CMS

- Hardware and FPGA design, software, final integration, and test by Testonica and TalTech (subcontractor)

- Successfully delivered in 2013 with positive feedback from CERN

#### Testonica

(⇔<del>)</del>

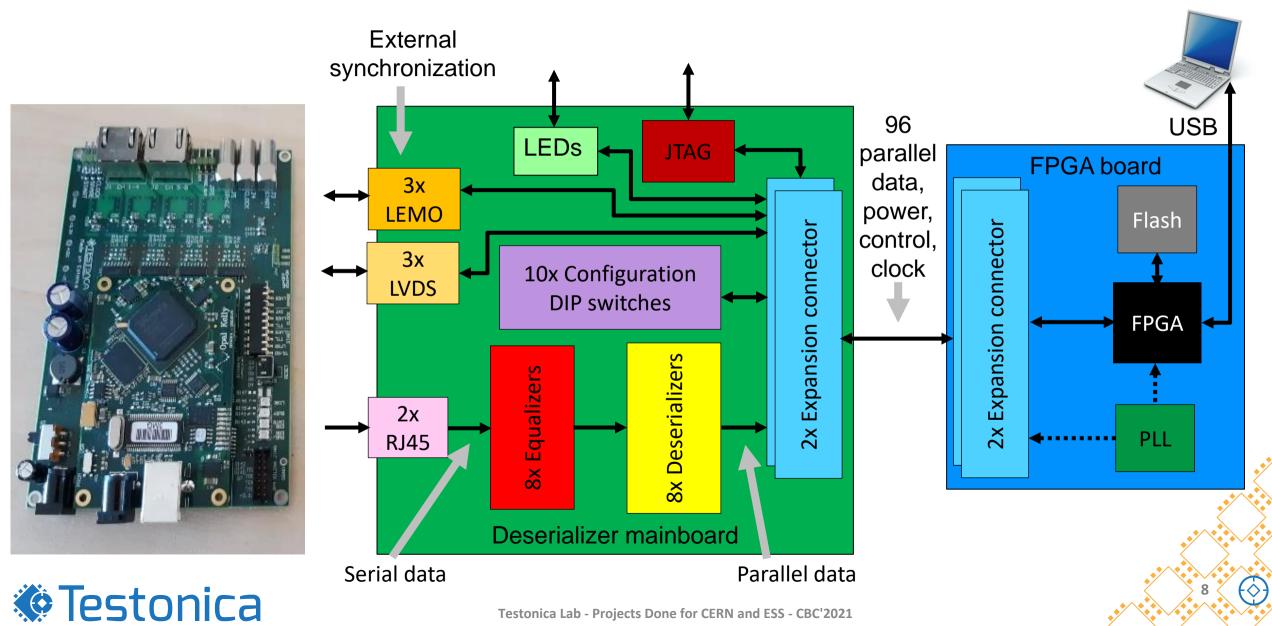

### **The Receiver Module HW**

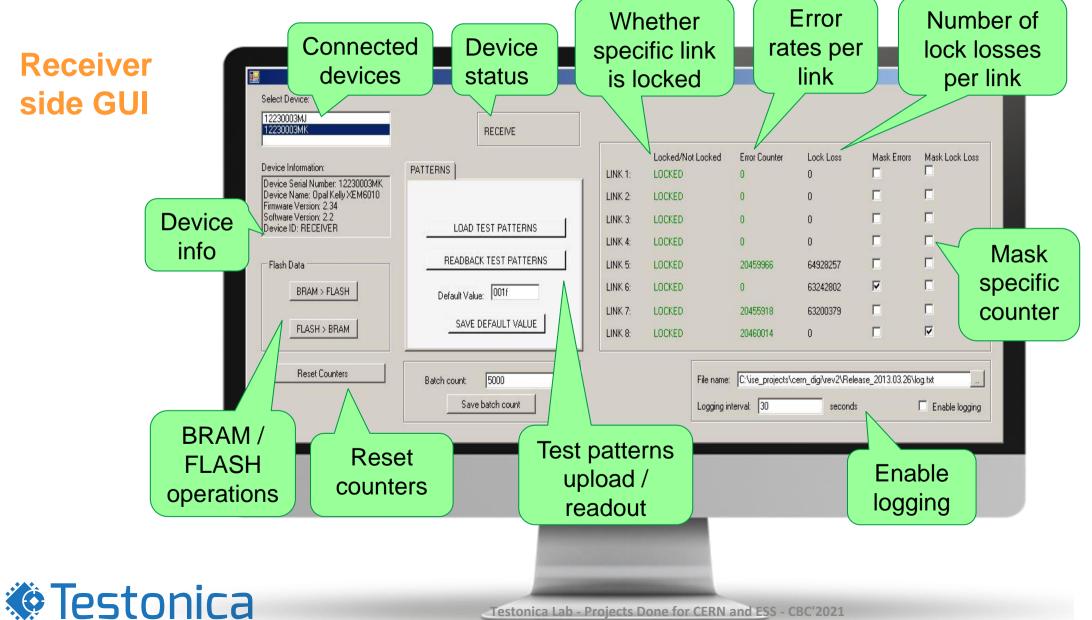

### The Control Software Application

$(\diamond)$

### DEVELOPMENT OF THE TAU LEPTON DECAY TRIGGERING ALGORITHM

# **Project Facts**

- Development of the tau lepton decay triggering algorithm

- Project initiated by

Testonica

- Estonian National Institute of Chemical Physics and Biophysics (NICPB)

- Development in collaboration with NICPB and TalTech

- On-going project: started in 2020 and to be continued until 2024

- Key challenge: process 10 billion objects (particle data) per second on a single FPGA

<del>\</del>♦∙

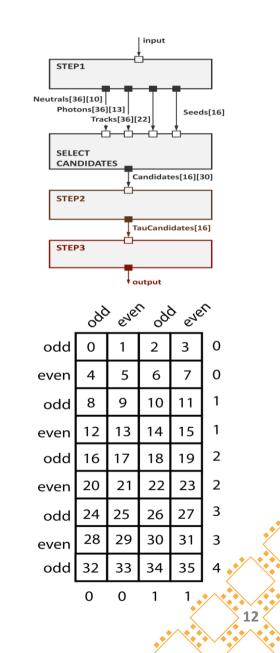

# Requirements

Allowed latency

Testonica

- IuS (max time before the processing results must be ready)

- Obsign clock frequency: 360MHz

O Platform

- VirtexUltrascale+ FPGA (the most advanced on the market)

Tool-chain: Vivado and Vivado HLS (High-Level Synthesis)

Used languages: C++ (HLS version) and VHDL

- Challenge: fit and route the design inside the FPGA while maintaining the required level of throughput

F♦

€⊘·

#### DEVELOPMENT OF AN FPGA-BASED I/O AND CONTROL SYSTEM FOR ESS/ERIC

# **ESS/ERIC Projects at TalTech**

- Embedded control SW, driver extensions, FPGA design and test

- strategy development in 3 projects (2016-2021):

- Development FPGA-Based I/O and Control System

- Embedded software development and HW design

- Implementation of an EtherCAT slave card

- Project is run and coordinated by TalTech

- Testonica provides consultancy and engineering support

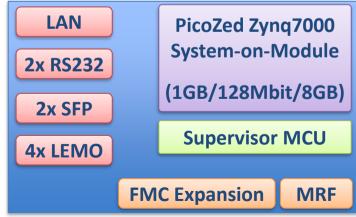

## **FPGA-Based I/O and Control System**

#### • Technical Specifications

- Synq7000 SoC-FPGA

- System-on-Module (SoM) based

- Ready-made Linux SW package

- IGB DDR3 memory

- ③ 128Mbit QSPI Flash (boot)

- 8GB eMMC Flash (application)

#### Interfaces

- +24V DC, passive cooling

- ③ Gigabit Ethernet

- ⊗ 2x SFP (up to 6.6Gbps)

- Ax LEMO connectors

- MRF expansion slot

- ITAG interface

#### Testonica

(�)

#### • Custom BERT Equipment – 2011

• Tau lepton decay triggering algorithm – 2020

Control System

ESS/ERIC: FPGA-Based I/O and Control System

Testonica

In collaboration with

$(\diamond)$

# Thank You! We love solving problems

$\cdot$