TIPP 2021 A. ZABI

# OUTLINE

Context of triggering @ HL-LHC: scientific case and system requirements (technological choices)

- Phase-2 L1 trigger conceptual design and instrumentation: System interfaces & Architecture. Key features and hardware prototyping.

- Phase-2 Level-1 trigger algorithm design, firmware developments & testing: selecting physics with sophisticated firmware algorithms and expected performance. System demonstration.

# TRIGGERING @ HL-LHC INTRODUCTION & DESIGN REQUIREMENTS

MIRUDOGIJUM & DESIGN RELUMENTO

The scout of the HL-LHC

TIPP 2021 A. ZABI CMS L1 TRIGGER @ HL-LHC

# INTRODUCTION: CONTEXT OF TRIGGERING

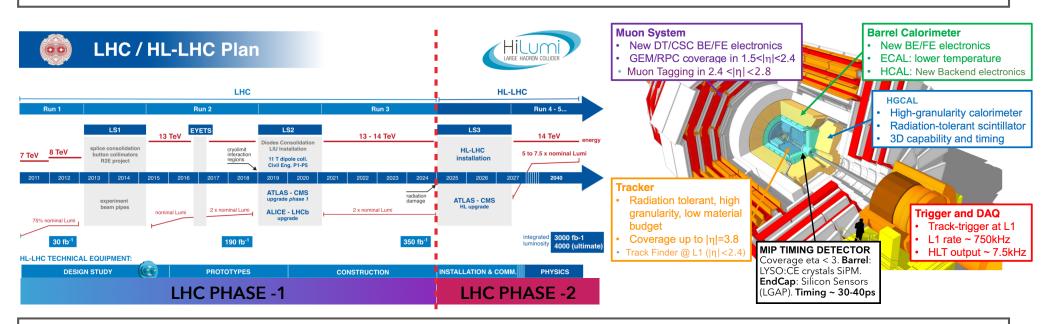

- <u>HL-LHC Upgrade Project</u>: offers an unprecedented opportunity to explore uncharted lands and achieve scientific progress.

- A new LHC machine and a new CMS Detector:

The HL-LHC and the CMS Phase-2 detector

→ Set the context of triggering & define system requirements

High-Luminosity-LHC: 13 TeV (Nominal:  $5x10^{34}$  & 140 PU, Int Lumi = 3000 fb<sup>-1</sup>)

- Ultimate:  $7.5 \times 10^{34}$  & 200 PU, Int Lumi = 4000 fb<sup>-1</sup> (baseline for all TDR studies)

- $\rightarrow$  unprecedented running conditions, exceeding machine design values 7 fold.

# PHASE-2 TRIGGER UPGRADE: KEY PARAMETERS & STRATEGY

## ► <u>CMS Phase-2 Trigger</u>:

- ▶ CMS keeps a 2-level triggering approach: L1 & HLT

- Level-1 (hardware) system

- Increase bandwidth 100 kHz → 750 kHz

- Increase latency 3.8 us  $\rightarrow$  12.5 us

- ▶ Benefiting from upgrade of the CMS detector:

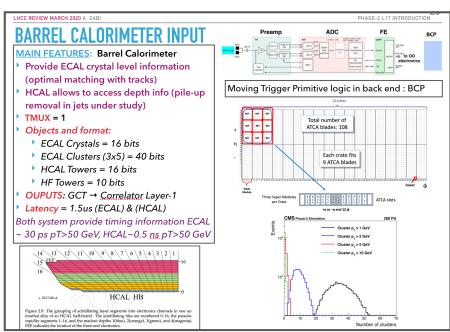

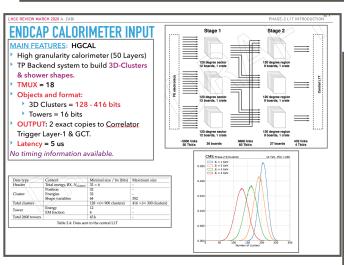

- ▶ Include high-granularity information (calo&µ)

- Include tracking information (first time!)

- → Manageable object rate (L1 Physics Menu)

- Strategy:

- Exploit sub-detector back-end electronics

- Sophisticated reconstructed objects and correlations → Enhanced physics selectivity

- Expand reach with Scouting System

TDR approved in 2020

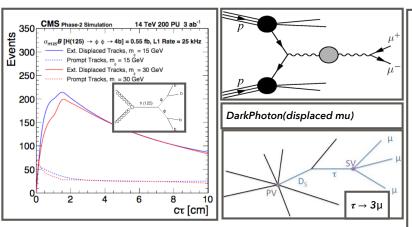

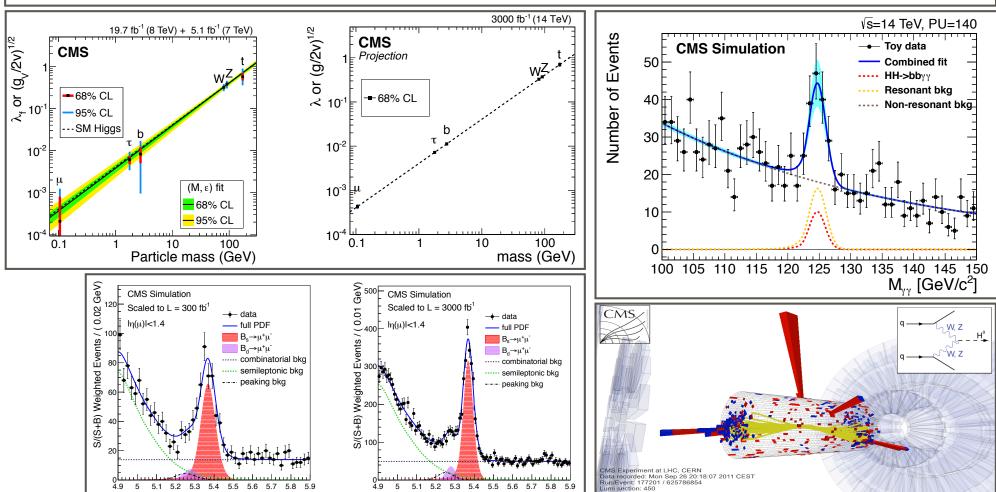

# L1 PHASE II TRIGGER UPGRADE: SCIENTIFIC CASE

Maintaining thresholds is  $\underline{NOT}$  the only motivation for upgrading the L1 trigger. HL-LHC research program opens a door to the unknown  $\rightarrow$  the Phase-2 Level-1 Trigger system is our scout!

The goal is to extend the physics reach by increasing the available phase space

### L1 Trigger algorithm requirements:

- higher-level trigger objects (particle-flow) w/ optimised response and resilient to pileup (up to 200)

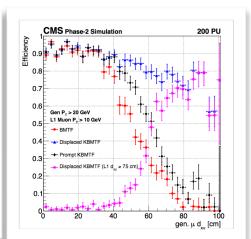

- Production, rare B-meson decays (tracking@L1), forward muon trigger for τ → μμμ (muon extended coverage), dedicated algos for displaced jets and muons, etc.

- Expand reach: Low mass resonances

# Phase-2: scouting datapath TRIK EC EB HB HF DT RPC CSC GEM EB HB HF DT RPC CSC GEM Track Finder Track Finder Track Finder Trigger Calo Trigger Correlator Trigger Correlator Trigger Correlator Trigger Correlator Trigger L1 Trigger Project Barrel Calo Trigger Correlator Trigger Barrel Barrel Barrel Trigger Correlator Trigger Barrel Trigger

### Scouting into HL-LHC data @ 40 MHz:

- Physics objects: reconstructed from L1 objects

- Storage: Only high-level information (selected events)

- Specific features: analyse multiple contiguous BX, identify signatures unreachable through standard trigger techniques

# L1 PHASE II TRIGGER UPGRADE: TECHNOLOGICAL CASE

The Phase-2 Level-1 Trigger system performs precise physics selection using a global event reconstruction based on enhanced granularity already at hardware level.

Considering: Inputs > 60 Tb/s (vs 2 Tb/s during LHC Phase-1), operate: 7.5e34 along w/ 200 PU events

- Cutting-edge hardware: modern technology

- → FPGA VU9P x 8 resources of Virtex 7 (Phase-1), 28 Gb/s links

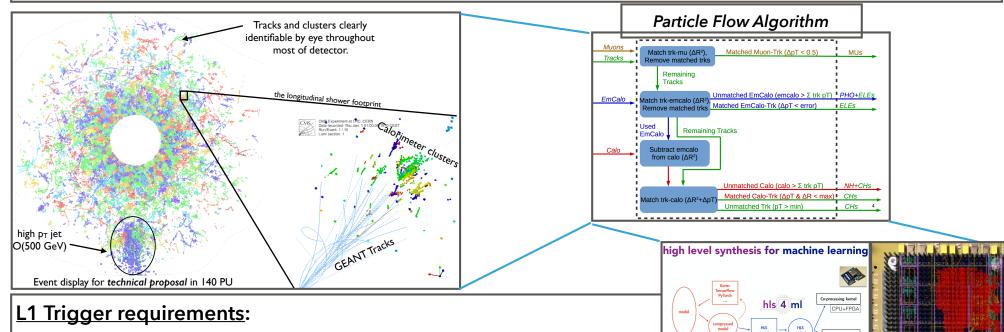

- High-Level-Synthesis: used successfully, much faster turn-around, novel techniques based on machine learning → The Phase-2 L1 Trigger can do much more!

- Advanced Architecture: platform and interconnections (ATCA) → robust, flexible & modular design

- Handling all technical issues: integration, commissioning, etc.

TIPP 2021 A. ZABI

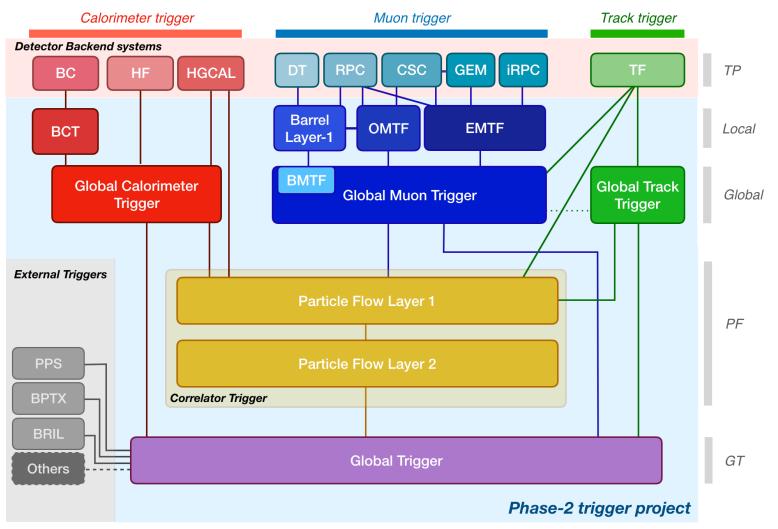

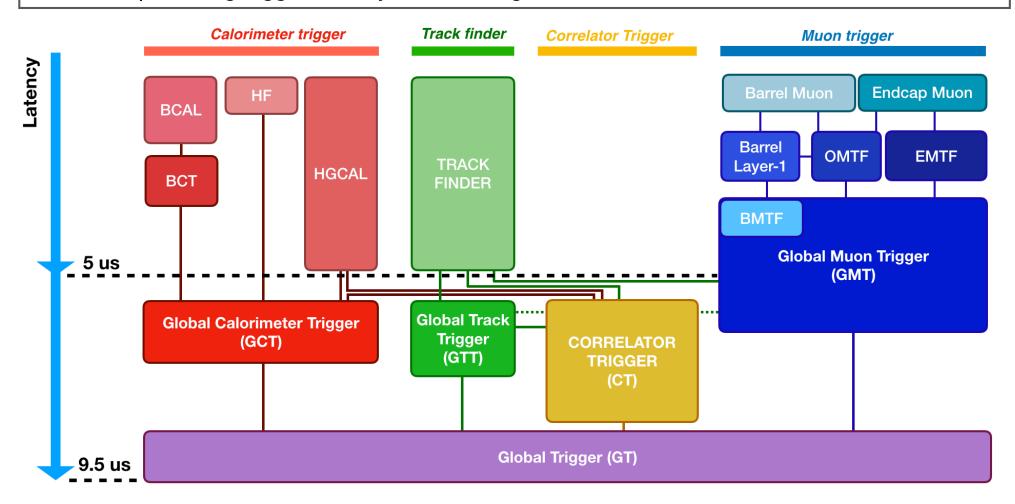

# LEVEL-1 PHASE II TRIGGER UPGRADE SYSTEM

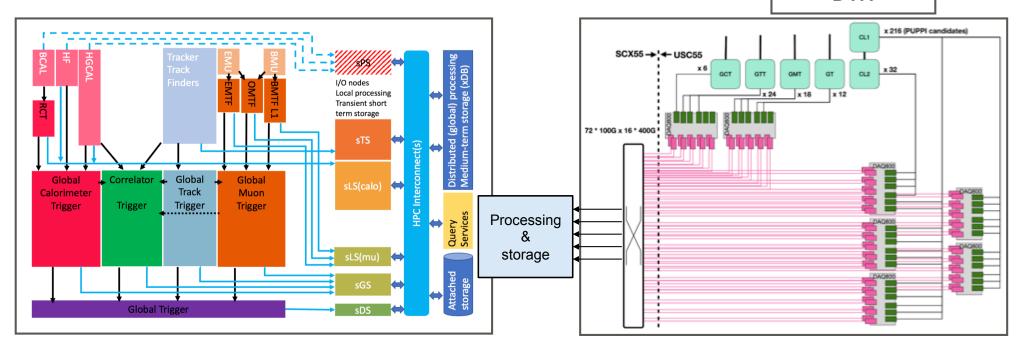

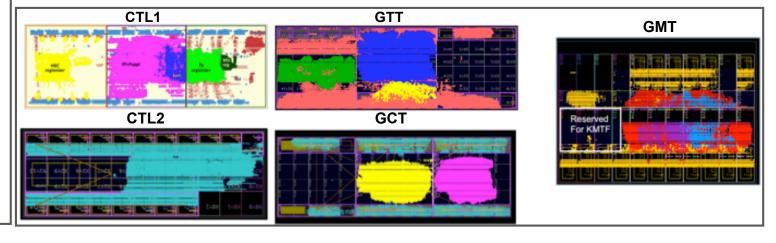

- Level-1 Architecture: Efficient distribution and processing of trigger primitives, provision appropriate resources and interconnections, retain enough headroom future flexibility & Robustness

- Level-1 technological choices: generic processing engines (inspired from Phase-1 upgrade)

- Key design feature: Correlator Trigger. Collects all inputs and feed sophisticated algorithms

- Design Constraints: HW processors ~ 100 links, FPGA resources < 50 %, Latency (< 9.5 us (keep 20%) while HGCAL/TF~5us)

CMS I 1 TRIGGER @ HI -I HO

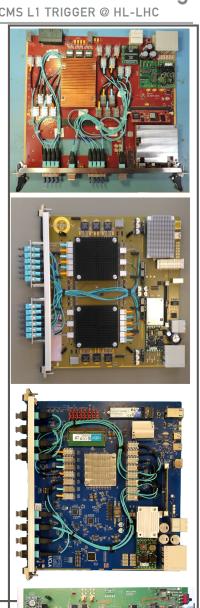

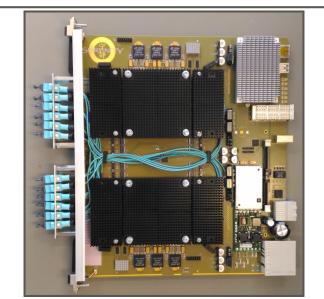

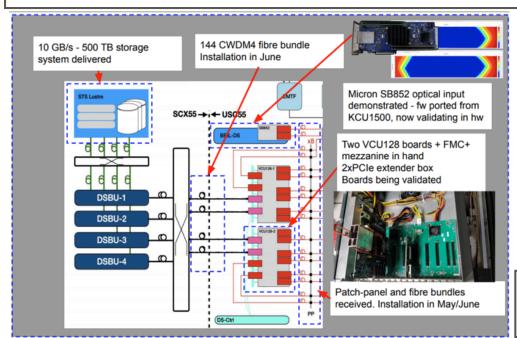

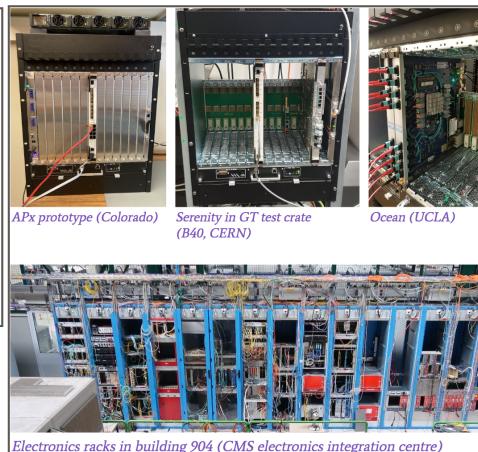

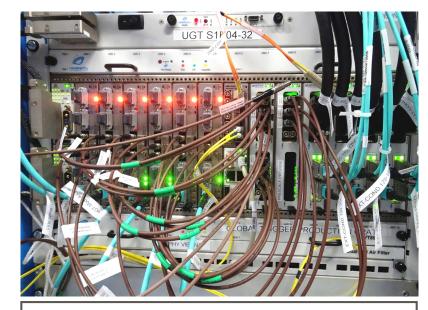

# HARDWARE PROTOTYPES

Design philosophy: Generic Processing Engines → I/O, FPGA

- FPGA: Xilinx Virtex Ultrascale / Ultrascale+

- Optics : Samtec Firefly x4 flyover

- 32 modules for 120 RX + 120 TX links

- ► A single optical module has 4 RX + 4 TX

- Processors on board running commercial linux for flexible configuration and monitoring

### **Serenity:**

- Carrier board w/ 2 sites hosting daughter cards (any combination of FPGA)

- Up to 144 bidirectional links (extendable to 192)

25 Gb/s

- Control & Monitoring: COM express (x86 processor)

- ▶ IPMI management through CERN IPMC

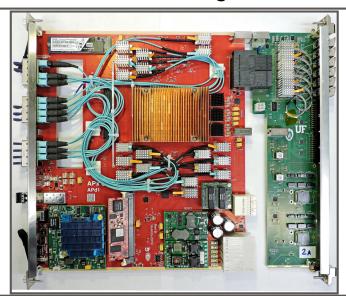

### **APX**:

- Powered by a VU9P FPGA with 2.5M logic cells

- ▶ 100 bidirectional links up to 28 Gb/s

- Control, management, and monitoring by an embedded linux mezzanine (ELM) (ZYNQ SoC)

- Shelf management via custom IPMI mezzanine (OS)

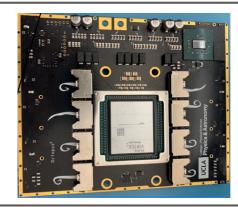

# HARDWARE CAN DO MORE: EVOLUTION

Design evolution (since TDR): increased I/O and computing power  $\rightarrow$  sophisticated algo, flexibility

- FPGA: larger A2577 pin package FPGA from Xilinx (Virtex UltraScale 13P)

- Optics: New denser version of on-board flyover Samtec Firefly, alternatives (ex: QSFP)

<u>Variant:</u> Intensive processing in muon trigger. Octopus Mezzanine (A2577-VU13P)

### **X20:** Evolution from OCEAN Prototype

- Modular design (x2 FPGA)

- Optical Module

- Up to 28 QSFP cages (112 links)

- Compatible with 25G and 10G transceivers

- Power Module: Off-the-shelf ZYNQ mezzanine, DC-DC converters, IPMC running on the ZYNQ

- Inter-module connections with cables

### Samtec Firefly x12

- ▶ One module: x12 RX or x12 TX

- Note Module in alpha-stage

- Ongoing test:

### Alternatives: QSFP

- widely used in industry

- ▶ x4 TX / x4 RX (x8 TX / x8 RX QSFP DD)

- Under qualification (BER etc)

**QSFP on X2O**

# SCOUTING @ 40MHZ: SCRUTINISING THE DATA

- Enables many features: real-time diagnostics (even at lower level systems), monitoring, testing new algorithms and developing menus, selecting an reconstructing physics objects w/o rate limitation.

- Analyses conducted trough queries (from storage)

- Demonstrated during LHC Run-2 with Level-1 Phase-1 muon output, now being prepared for Run-3 data taking

- Uses DTH board (DAQ800) designed for large readout detectors

DTH

# THE PHASE-2 L1 TRIGGER ALGORITHMS, FIRMWARE & TESTING

selecting physics

# PHASE II LEVEL-1 TRIGGER: ALGORITHMS & MENU

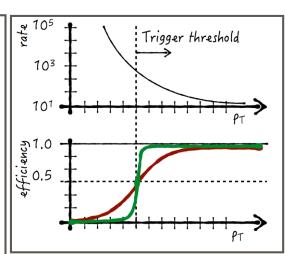

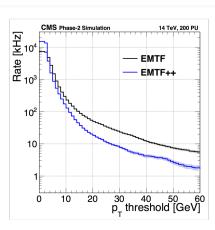

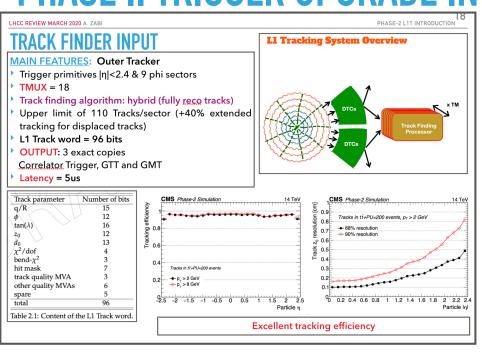

### Algorithms for the Level-1 trigger:

- Extensive use of tracking to reach near offline performance (sharper efficiency turn-on curves) + reconstruction of Primary Vertex.

- Exploit complementarity of different object flavour:

- Standalone objects: robust triggers based on independent sub-detectors

- Track-matched objects: tracking used to confirm standalone Muon and Calo objects, significant improvement with simple design

- Particle-flow objects: ultimate performance improvement, combine all information to match offline algorithms, require most processing time and resources for calculation

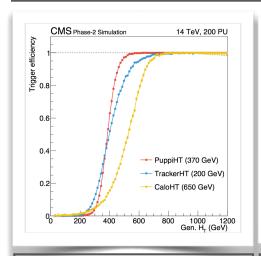

### Level-1 Menu:

- Simplified: Phase-1physics built from Run-2L1 Menu (346 kHz)

- Extended: new triggering strategy to expand physics reach

(+110 kHz)

### Particle-flow/PUPPI HT

Standalone forward Muon reconstruction Endcap Displaced Muon trigger Barrel (Kalman Filter) → Run-3

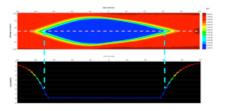

# **GLOBAL EVENT RECONSTRUCTION @ LEVEL-1**

- Availability of tracks & high-granularity calos

- Implement global event reco @ L1 (like PF)

- Additionally it makes sense to mitigate pileup

- Challenge: can we run full PF+PUPPI in time w/ hardware for I 1?

### Can we run a PF takes in PF is **PF Links** local PU Algo? everything local Assemble PUPPI is local Assemble Particle flow Can parallelize it All detectors Things in combines local regions everything together by region to Particls nxΦ **HGCal** Also its the CMS default PU algo Hcal Muons Tracks

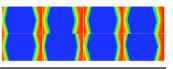

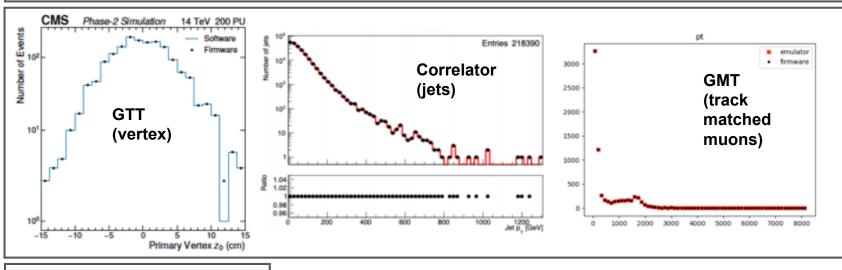

- Demonstrated a working PF+PUPPI algorithm

- PF+PUPPI hugely reduces the event complexity

- Allows for a lot of flexibility in downstream design

- L1 Algorithms looks like offline reconstruction

- PF+PUPPI developed with Vivado HLS (a lot of written by physicists along with engineers)

Sang Eon Park's poster: The Particle Flow Algorithm in the Phase II Upgrade of the CMS Level-1 Trigger

• What are the advantages of particle flow? PF+Puppi A simpler event with the core physics preserved · Better resolution Ease of use → build particle level algorithms

demonstrator

CMS Collaboration, Particle Flow CMS JINST 12 (2017) P10003, arXiv:1706.04965. D. Bertolini, P. Harris, M. Low, and N. Tran, PUPPI, JHEP 10 (2014) 059, arXiv:1407.6013.

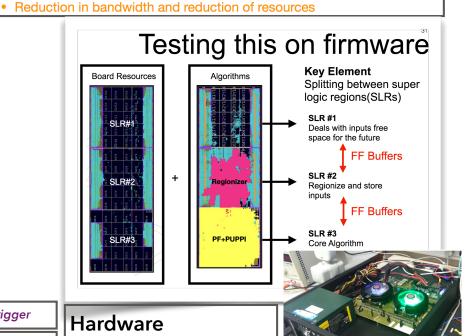

# **ALGORITHM INTO FIRMWARE**

### Firmware design:

- Algorithm developed mostly in C → High Level Synthesis (HLS)

- ▶ New fixed point arithmetic in C++ [taken from Xilinx libraries]  $\rightarrow$  emulator firmware

- Continuous integration of the firmware in repository

Excellent correspondance firmware & emulator

### Firmware integration:

- All algo & manage I/O

- Verify timing, resources utilisation & latency.

- Common framework wrapper → firmware implementation board agonistic

# **TESTING AND SYSTEM DEMONSTRATION**

### Phase-2 Level-1 Trigger system demonstration

- Single-board and multiple board tests

- Integration centers across the globe: larger scale integration planed @ CERN (904)

- Board connection: protocol

- Links (asynchronous) operation @ 25.78 Gb/s

- L1 Trigger boards sending packets only once (no retransmission) → error proof

- Protocols (64/66b or 64/67b) encoding achieved low error rate, validated recovery mechanism etc.

Scouting System for LHC Run-3

# CMS PHASE II L1 TRIGGER UPGRADE

- ▶ CMS proposing solid solutions to triggering and data acquisition challenge @ HL-LHC

- ▶ Phase-2 Level-1 Trigger Upgrade project: TDR approved in 2020 (https://cds.cern.ch/record/2714892?ln=en), steady progress with construction

- Level-1 Hardware trigger with enhanced capabilities complying with physics requirements. Sophisticated algorithms (particle-flow) are prototyped in FPGAs and exploit target hardware (VU9P/ 28Gb/s links)

- Modular and flexible architecture

- Hardware development lines pursuing 4 flavours of ATCA boards meeting the requirements of the project.

- Hardware demonstration ongoing and planned for testing with live data during LHC Run-3

CMS L1 TRIGGER @ HL-LHC

# PHYSICS @ HL-LHC

### **CMS Phase-2 physics drivers**

- **Exploring the unknown**: Searches for new physics beyond the Standard Model (SM) DM, LLP, etc.

- Standard Model as tool for discovery : Precise knowledge of SM processes, probe anomalous couplings, 4 tops, VBS, VBF, etc. Higgs Sector: couplings (Hcc, Hμμ), differential xc, self-coupling HH

- Understanding the Standard Model: parton shower, underlying event, differential measurements

m<sub>uu</sub> (GeV)

CMS L1 TRIGGER @ HL-LHC

# LEVEL-1 PHASE II TRIGGER UPGRADE SYSTEM

### Phase-2 L1 trigger: latency

Latency budget = 9.5 us (20% margin to get to 12.5 us)

- 5 us on region processing

- 4.5 us on producing triggerable objects (including correlations) & final decision

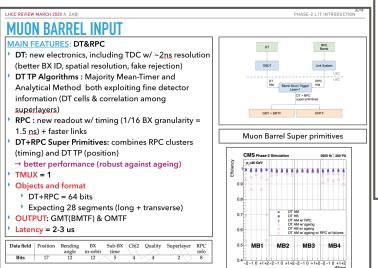

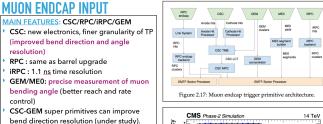

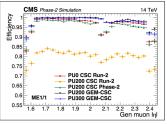

# PHASE II TRIGGER UPGRADE INTERFACES

Could also CSC + (i)RPC

CSC segment = 32 bits

RPC Clusters = 15 bits

▶ iRPC Clusters = 41 bits

▶ GEM Clusters = 14 bits

Latency = 1 us - 1.75 us (CSC)

**OUTPUT: OMTF & BMTF**

▶ GEM ME0 segment = 24 bits

Objects and format

TMUX = 1

# **TECHNOLOGICAL CHOICES**

### Phase-2 L1 Trigger Design: Key technological features (inspired from the L1 Phase-1 upgrade)

- FPGA: The extensive use of state-of-the-art FPGAs → optimised reconstruction, identification, isolation and energy calibration of trigger objects using high-granularity detector information.

- High-speed optical links: facilitate the aggregation of data from across the entire detector

- → A complete view of the detector (evaluation of global quantities MET, pileup, specific VBF)

- Flexible and modular architecture: Reconfigured to adapt to HL-LHC running conditions and physics needs. Extra resources → Compute sophisticated quantities → richer menu and increased selectivity

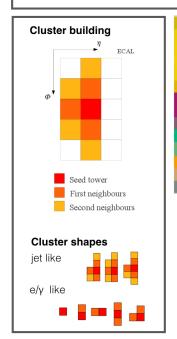

Phase-1 EG algo

Phase-1 Upgrade: increased calorimeter granularity

Phase-1 Upgrade: Expanded architecture