Institute for Astroparticle Physics (IAP)

# The upgraded electronics of the Pierre Auger surface detector Fabio Convenga on behalf of the Pierre Auger Collaboration

#### **Overview**

On the **Pierre Auger Observatory** [1], an upgrade called **"AugerPrime"** [2] is underway to obtain more detailed information about the mass composition and origin of the high-energy flux suppression.

The AugerPrime upgrade contains many improvements to the Observatory:

• an additional **small PMT** in the water Cherenkov detector (WCD) to increase the dynamic range,

### **Deployment current status**

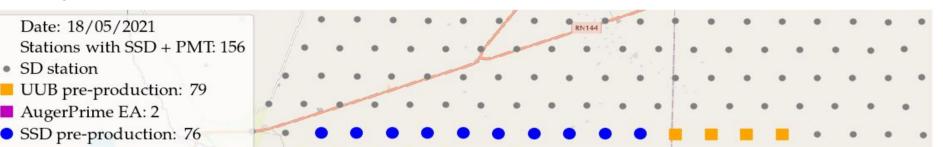

The deployment of (pre-)production UUBs to the field started in December 2020. There are currently a total of **79 surface stations** that have UUBs. These stations all have SPMTs and SSDs and monitored by the collaboration.

An Engineering Array of twelve AugerPrime stations has been in place since 2016 to test and monitor the performance of the upgraded detectors. Currently, two stations remain in this portion of the array.

• a surface scintillator detector (SSD) and a radio antenna (RD) above each existing WCD to provide a complementary measurement of the shower particles,

Figure 1: Prototype of AugerPrime detector

• **new electronics** for the surface station that will process signals from the new detectors.

# **Digital and analog functionality of the UUB**

The new electronics (Figure 2), dubbed Upgraded unified Board or UUB has:

- faster ADCs (120 MHz instead of 40 MHz) with greater dynamic range (12 bits each instead of 10 bits);

- a Xilinx Zynq-7020 All Programmable SoC FPGA (Artix-7 FPGA and associated ARM Cortex A9 Dual 333 MHz co-processor) instead of the older Cyclone series Altera FPGAs used in the original electronics;

- Xilinx PetaLinux runs on the embedded ARM processor.

The FPGA (for more information, see Ref. [3]):

- uses firmware primarily written in Verilog and Xilinx Vivado for the overall structure and standard modules;

- implements **ADC readout** and the **interfaces** to the LED flasher, GPS receiver, and memory interfaces;

- manages the generation of local station triggers. The current surface station triggers are implemented using filtered and down-sampled traces to simulate the characteristics of the old telectronics so as not to interfere with data taking during deployment. A new trigger has been 10<sup>4</sup> implemented to account for the new SSD.

Figure 4: SSD and UUB pre-production array. The small gray circle indicates normal SD stations, the orange square indicates stations with SSD and new electronics, the purple square indicates the remaining stations in the EA, and the large blue circle indicates stations with old electronics and (pre-)production SSD.

# Performance

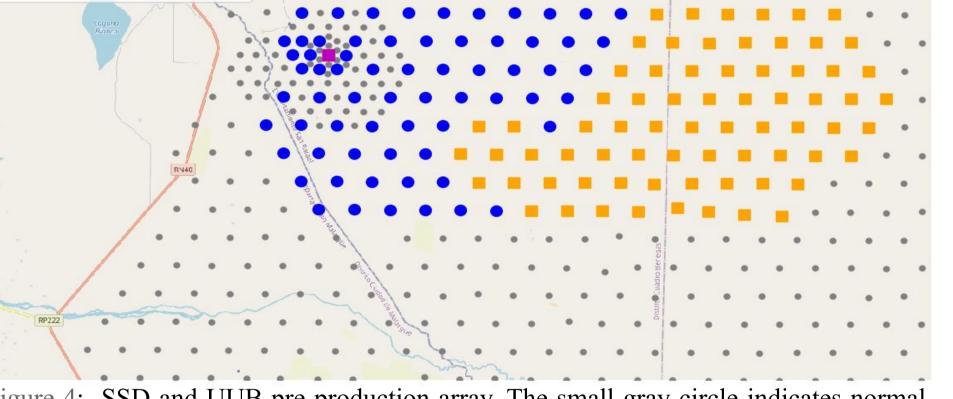

Currently the stations with the UUBs are under control and monitoring by the Collaboration. **Noise studies**, **timing studies**, and **calibration studies** for SPMT and SSD are being done on the array. Noise levels measured in the array are consistent with those in the design phase. Figure 5 shows the baseline RMS distribution in April 2021 acquired from the all stations with UUB.

Detector synchronization:

is done by tracking the variations of the local 120 MHz clock with respect to the GPS 1 PPS signal. For the new electronics was chosen the **Synergy SSR-6TF timing GPS receivers**. The FPGA, through the time-tagging module, manages the GPS and the data timing.

Figure 2: The latest version of the new electronics, dubbed Upgraded unified Board or UUB, during a test procedure.

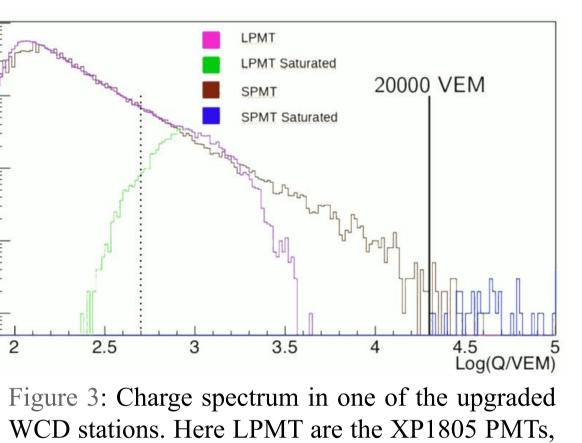

SPMT is the R8619 PMT [4].

The **anode channel** of the three large XP1805 PMTs of the WCD is split and amplified to reach a gain ratio of 32. To increase the dynamic range of the WCD, a fourth small PMT (Hamamatsu R8619, 1" diameter) is inserted in the WCD, dedicated to the measurement of large signals (Figure 3). The **anode of the SSD PMT** is split into two different channels, the first one amplified to have a gain ratio of 32 and the other attenuated by a factor of 4. This yields a total gain ratio of 128. The signals pass through a 60 MHz cutoff anti-aliasing filter and are digitized similarly to the WCD PMT signals.

10

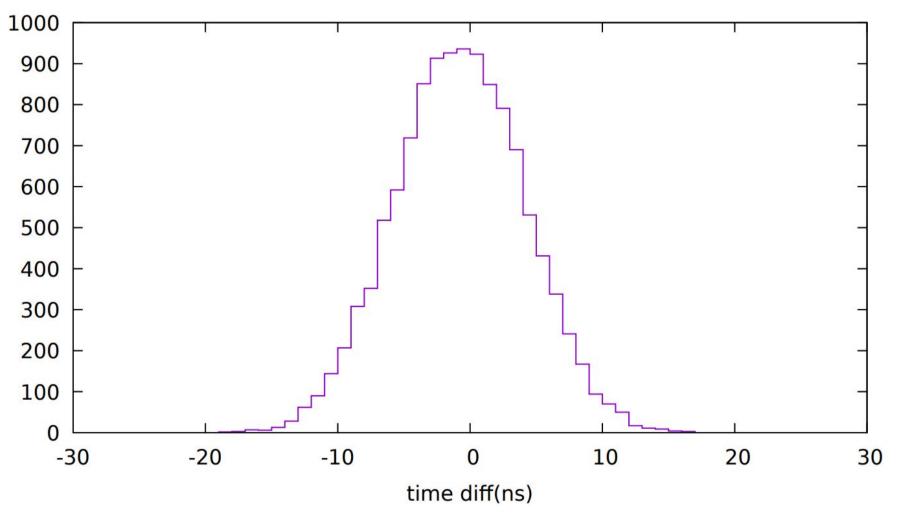

Timing resolution was measured using showers triggering 2 neighboring upgraded test stations dubbed Clais and Trak. The end-to-end timing accuracy (Figure 6) of a single station in real showers was measured to be better than 10 ns (vs. the current 13 ns).

Clais-Trak time difference - Feb/2021

Figure 6: Measured timing resolution on showers using two nearby test stations.

#### **UUB slow control functionality and calibration**

#### References

The UUB is equipped with a **micro-controller** (MSP430) for the control and monitoring of the PMT high voltage, the supervision of the various supply voltages, and reset functionality. More than 90 monitoring variables are managed by the slow-control software.

The Vertical Equivalent Muon (VEM) signal is used to calibrate the high-gain WCD [4]. It was previously evaluated on a test local station with an external hodoscope to give an average of 95 photoelectrons at the cathode of the XP1805 PMTs. The SPMT is calibrated with a selection of small showers that allows it to be cross-calibrated with the VEM signals of the LPMTs. SSD calibration is based on the signal of a **minimum ionizing particle** (MIP) passing through the detector. In addition, each WCD is equipped with two LEDs useful for monitoring and linearity testing.

[1] The Pierre Auger Collaboration, The AugerPrime Design Report, arXiv:1604.03637.

[2] A.Castellina [Pierre Auger Coll.], EPJ Web Conf. 210 (2019) 06002.

[3] D. Nitz [Pierre Auger Coll.], PoS(ICRC2019) 370.

[4] X. Bertou [Pierre Auger Collaboration], Nucl. Instrum. Meth. A 568 (2006) 839–846.

KIT – University of the State of Baden-Wuerttemberg and National Research Center of the Helmholtz Association