## Development of FPGA based 128-Channel TDC for Time Projection Chambers

Yuvaraj.E<sup>a</sup>, S.S. Upadhya<sup>a</sup>, M.N.Saraf<sup>a</sup>, Jim Jhon<sup>a</sup>, B.Satyanarayana<sup>a</sup>, Gobinda Majumder<sup>a</sup>, Chithra<sup>b</sup> India based Neutrino Observatory

<sup>a</sup>Tata Institute of Fundamental Research, Colaba, Mumbai - 400005, India. <sup>b</sup>Indian Institute of Technology Madras, Chennai - 600036, India.

precise position of interaction.

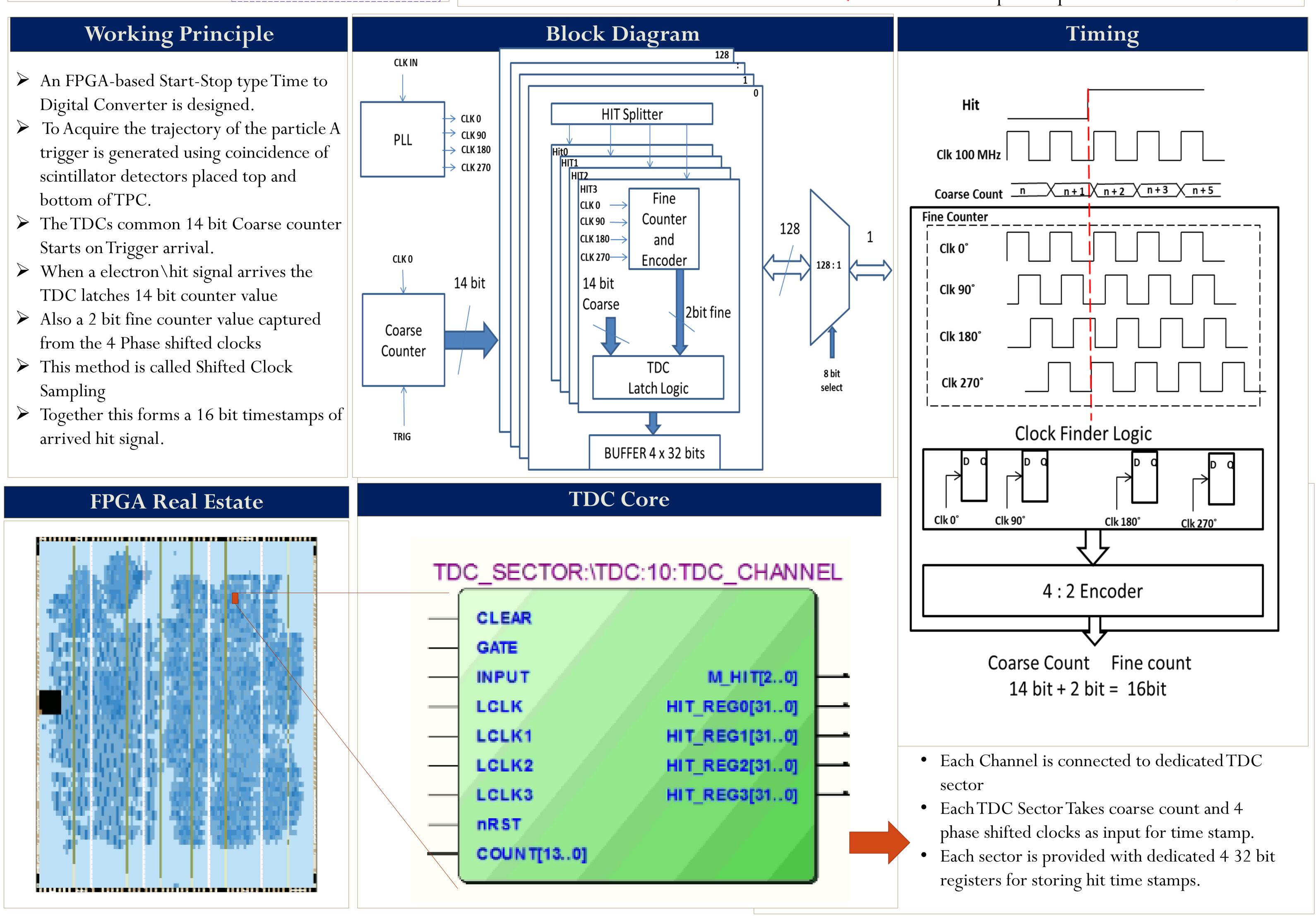

| FPGA Resources                 |  |

|--------------------------------|--|

| Family Cyclone IV E            |  |

| FPGA Device EP4CE115F29C7      |  |

| Total logic elements           |  |

| 40,620 / 114,480 ( 35 % )      |  |

| Total pins                     |  |

| 362 / 529 ( 68 % )             |  |

| Total memory bits              |  |

| 2,939,328 / 3,981,312 ( 74 % ) |  |

| Embedded Multiplier            |  |

| 4 / 532 ( < 1 % )              |  |

| Total PLLs 2 / 4 ( 50 % )      |  |

## **TDC Specifications**

- 100 MHz Coarse clock  $\bullet$

- 128 Channels lacksquare

- Dynamic Range 160us

- Resolution 2.5ns

- Multi hit up to 4  $\bullet$

- Both Leading and Trailing edge measurement

- 32 bit Time stamp

- Configurable Parameters

- Multiplexer based Timestamp Register Access

- Can be scaled to 256 Channels

## Conclusion

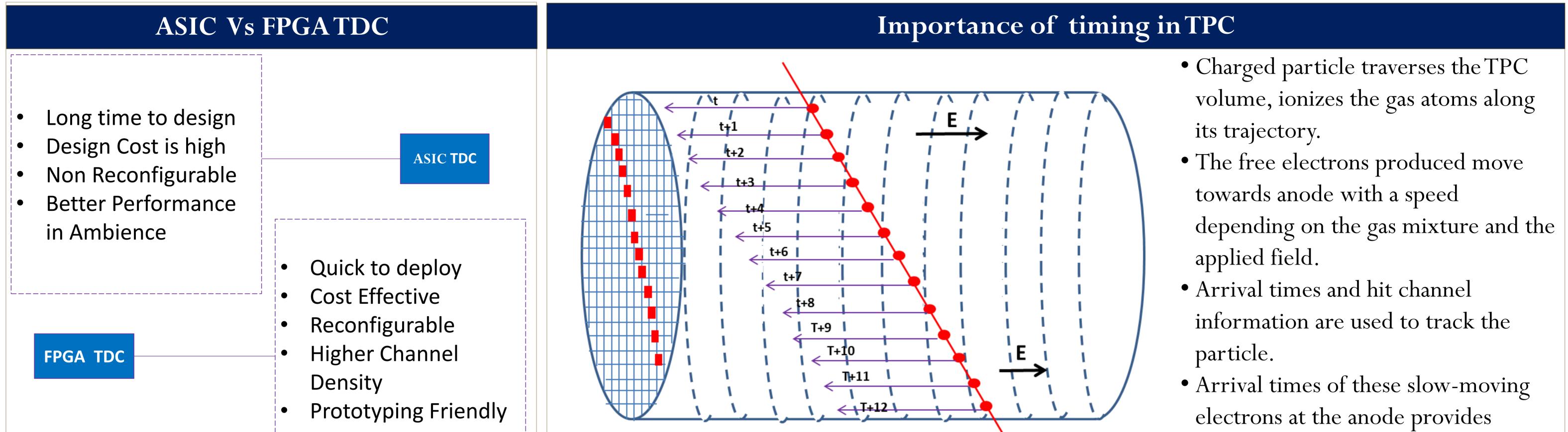

- TPCs requires marginally lower resolution of timing device but more channel density

- Designing an ASIC with more channel density complicates the design.

- FPGA based TDC can be easily scaled to more channels.

- Also with higher operating Frequency higher Resolution can be achieved.

- PLL and DCMs must be used to maintain jitter free clock

## Visiit: http://www.ino.tifr.res.in/ino/