## ID: 303

# Development of new high speed data acquisition system prototype for SOI pixel detector using 10 Gb Ethernet SiTCP

<u>R. Nishimura <sup>A</sup></u>, S. Kishimoto <sup>A</sup>, Y. Arai <sup>A</sup>, T. Miyoshi <sup>A</sup> <sup>A</sup>High Energy Accelerator Research Organization (KEK)

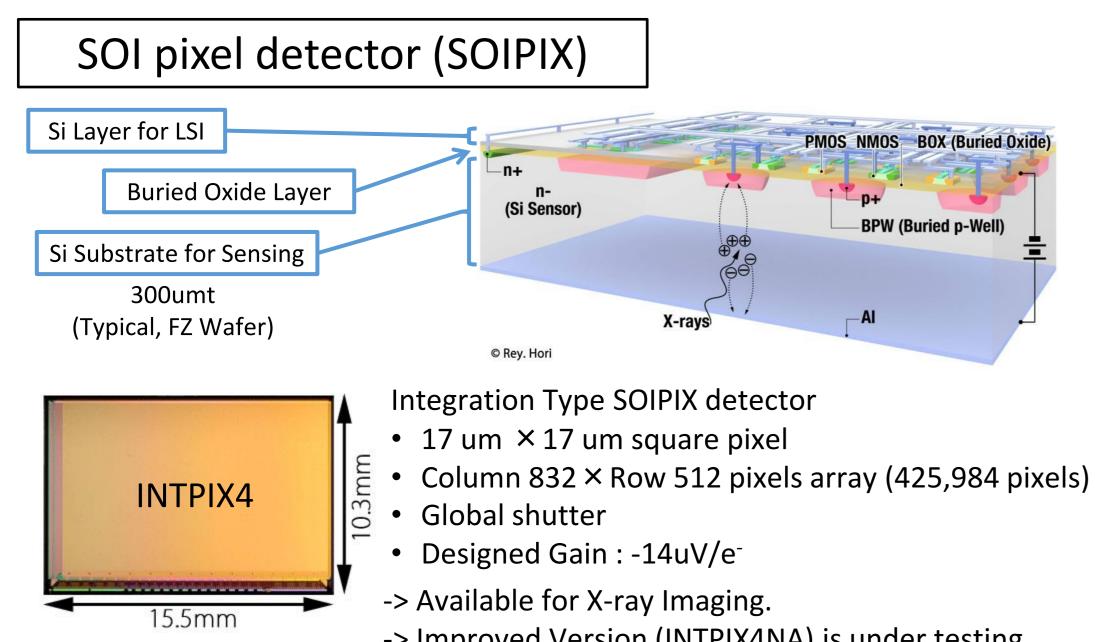

# Introduction

# **10GbE SiTCP Data acquisition system**

### Plan of data acquisition system production board

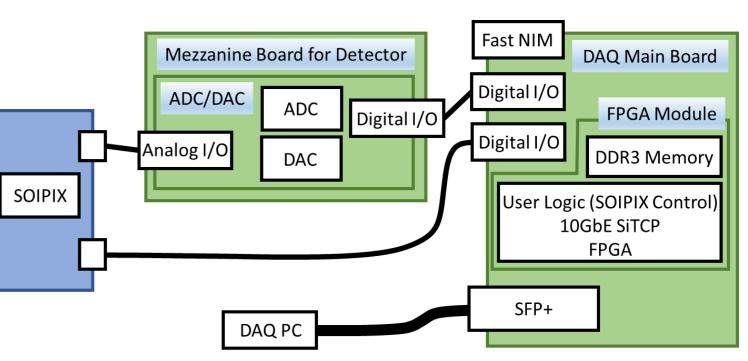

- System boards consists of DAQ main board and Mezzanine board for detector's Analog signal processing.

- Mezzanine board has 16 channels 12-bit Analog-to-Digital Converter and 8 channels Digital-to-Analog Converter.

- DAQ main board has Digital I/O (MIL interface) for

- -> Improved Version (INTPIX4NA) is under testing.

### 10Gb Ethernet SiTCP (SiTCP-XG)

- **<u>SiTCP</u>** is a network processor IP (Intellectual Property) core that can be implemented in an FPGA.

- Developed by Tomohisa Uchida (KEK ESYS), and currently developed and supported by Bee Beans Technologies.

- Small circuit size(~3000 Slice), simple FIFO like I/F, close to specification maximum transfer speed caused by Hardware-based implementation and easy to customize.

- Present system using 1GbE SiTCP, and it is not enough for advanced experiments. (high framerate, large area etc.)

-> 10Gb Ethernet SiTCP (SiTCP-XG) is upgrade version of SiTCP and strong solution for our readout system.

# **Experimental results**

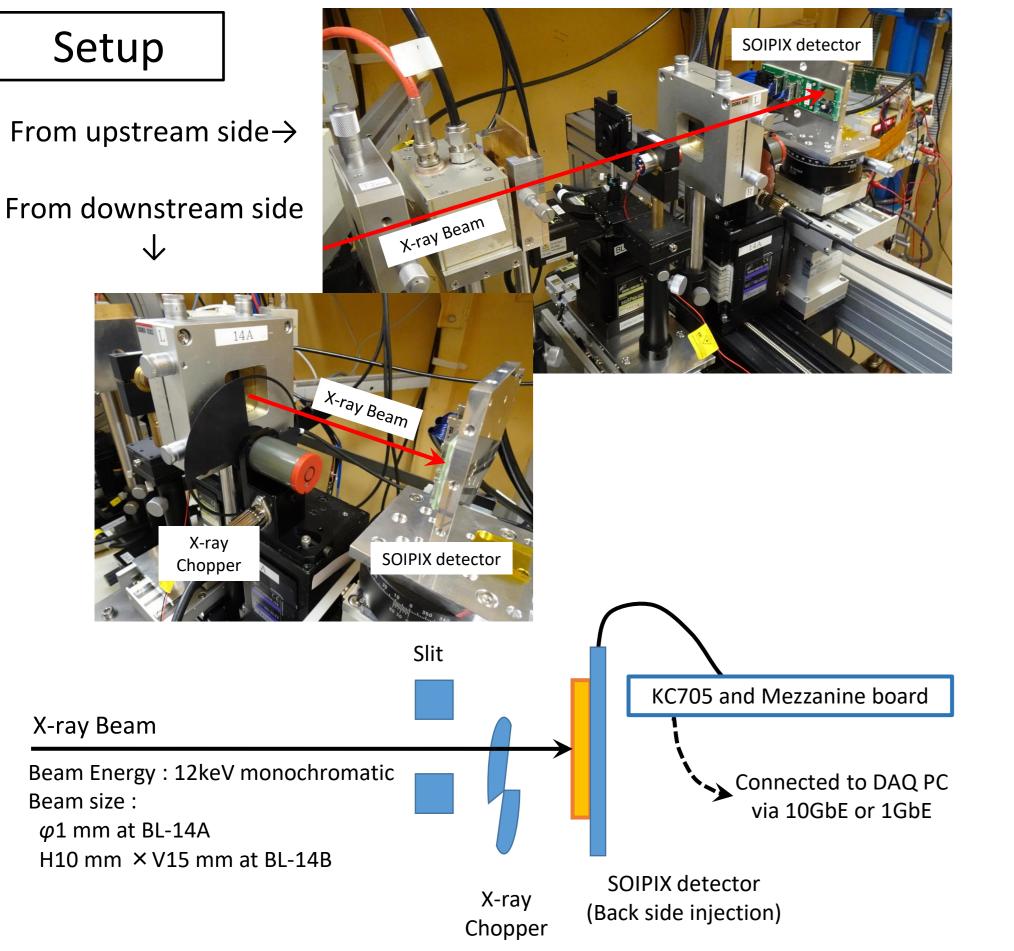

### Setup

#### Condition of Test 1.

#### Exposure time :

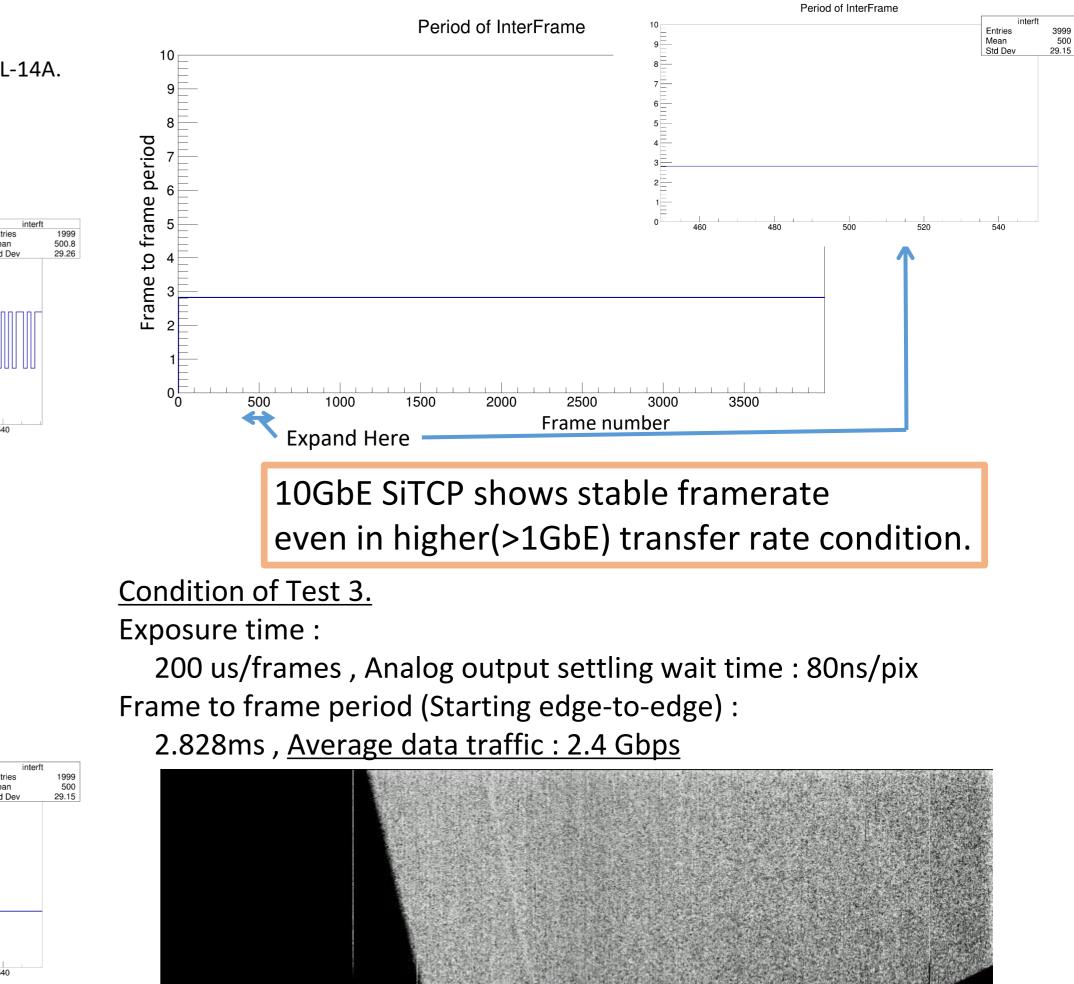

200 us/frames , Analog output settling wait time : 240 ns/pix Frame to frame period (Starting edge-to-edge) : 10 ms (Triggered by 100 Hz clock), Average data traffic : 682 Mbps (If one frame's data transfer wasn't completed in 10 ms, next frame's period will extended to 20 ms or 30 ms.)

- SOI pixel detector, Fast NIM interface for external trigger/synchronize control and SFP+ interface for 10 Gb Ethernet.

- Xilinx Kintex-7 FPGA and DDR3 memory were implemented on one ready-made module board and mounted on DAQ main board.

- 10GbE SiTCP was implemented to Kintex-7 FPGA, mixed implementation with SOIPIX control logic.

### Prototype of data acquisition system

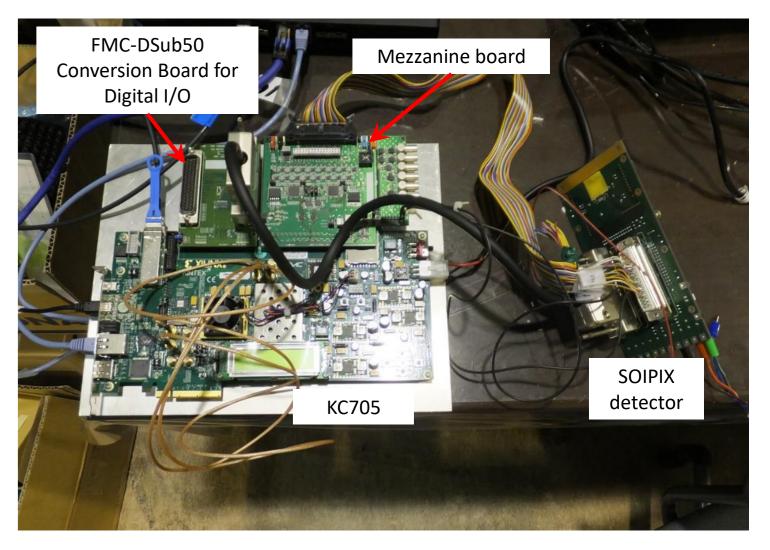

- KC705 commercial FPGA evaluation board was used as a substitute for the DAQ main board.

- Initial version of Mezzanine board was connected via FMC-LPC connector.

- Alpha release of 10GbE SiTCP was implemented to Kintex-7 FPGA on KC705, mixed implementation with SOIPIX control logic.

- Stable release of 1GbE SiTCP also available for comparison of the difference of performance.

#### Condition of Test 2.

#### Exposure time :

200 us/frames , Analog output settling wait time : 80ns/pix Frame to frame period (Starting edge-to-edge) : Limitation of detector specification 2.828ms, <u>Average data traffic : 2.4 Gbps</u> (If one frame's data transfer wasn't completed in 2.828 ms, next frame's period will shows longer time)

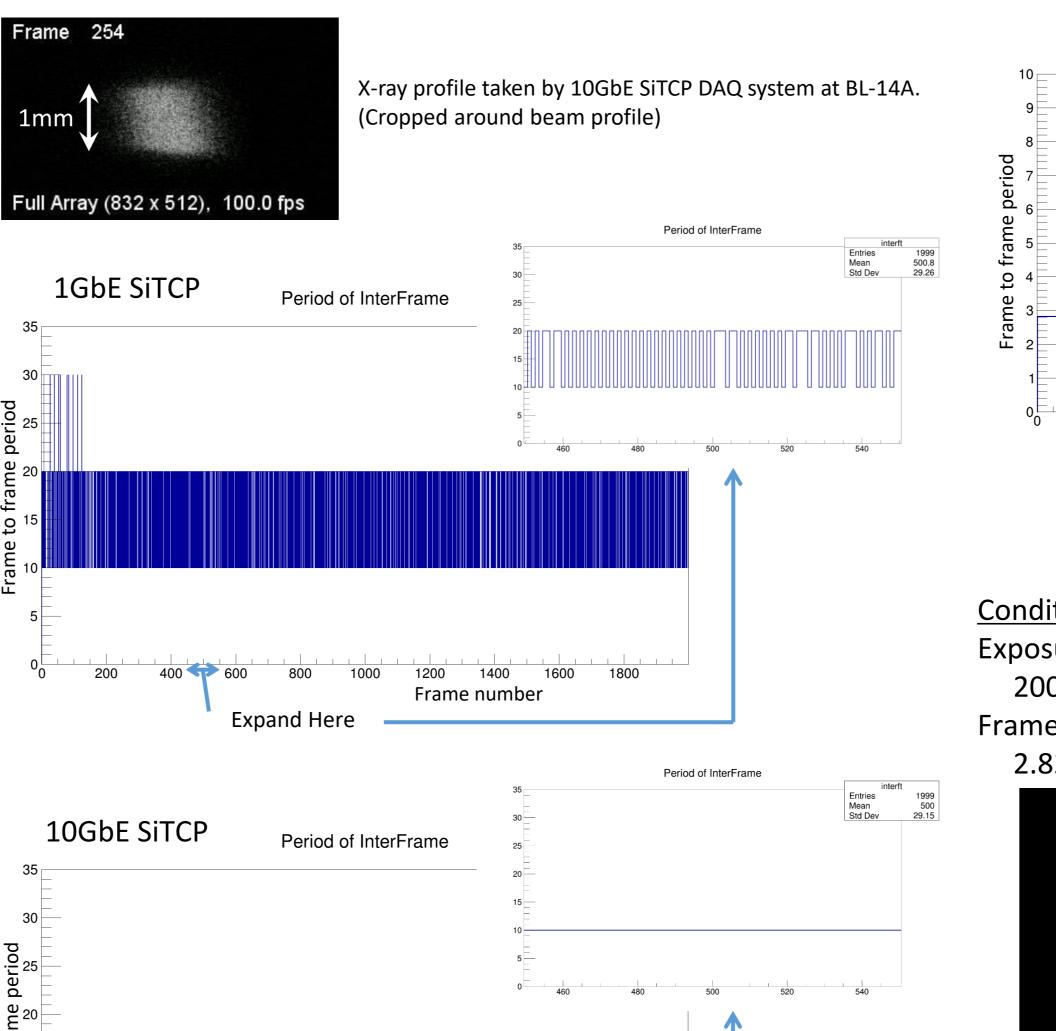

Tests for prototype DAQ system were done at KEK Photon Factory BL-14A and BL-14B.

X-ray beam (12keV monochromatic) was injected from backside of SOIPIX detector and was intercepted by an X-ray chopper with a duty ratio of 50%. It is easy to determine if the DAQ system is transferring data correctly by looking at the X-ray profile being captured.

This prototype DAQ system was tested with below 3 conditions :

1. Take 100 fps X-ray movie (framerate was controlled by 100 Hz internal clock) with 1 GbE SiTCP and 10 GbE SiTCP to compare the difference of performance. (at BL-14A)

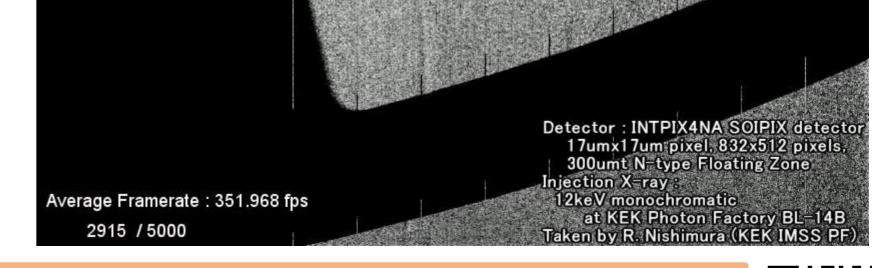

- 2. Take 350 fps X-ray movie (not controlled by internal clock) with 10 GbE SiTCP to determine the stability of transfer rate over than 1GbE speed. (at BL-14A)

- 3. Take 350 fps X-ray movie with larger field X-ray beam. (at BL-14B)

# Conclusion

Expand Here

**10GbE SiTCP result shows no fluctuation** caused by instability of transfer rate.

- SOI pixel detector's new DAQ system based on 10GbE SiTCP is now under developed.

- Prototype DAQ system was developed on KC705 FPGA board.

- Prototype system was tested with SOI pixel detector (INTPIX4NA) at KEK PhotonFactory BL-14A and BL-14B.

- 10GbE SiTCP result shows no fluctuation caused by instability of transfer rate in 682 Mbps average data traffic situation.  $\bullet$

- 10GbE SiTCP shows stable framerate at 350 fps (avereage data traffic is 2.4 Gbps).  $\bullet$

- These results were the initial result of X-ray imaging data taken by 10GbE SiTCP.

#### 10GbE SiTCP was advanced to Beta release and now you can try! Go to <a href="https://github.com/BeeBeansTechnologies/SiTCPXG">https://github.com/BeeBeansTechnologies/SiTCPXG</a> Netlist for Kintex7 or Scan right QR code

International Conference on Technology and Instrumentation in Particle Physics 2021 (TIPP2021)

You can see the movie data from below link or right QR code. (Dropbox link valid until 2021/05/31.) https://www.dropbox.com/s/9fhv06qofwnqkx1/201122-25\_BL-14B\_I4NA\_XG\_350fps\_Run00003.mp4