# INJECTION TEST: BUILDING A DATA INJECTOR FOR THE

2021 CAP VIRTUAL CONGRESS

### MAHEYER J. SHROFF UNIVERSITY OF VICTORIA

**JUNE 10 2021**

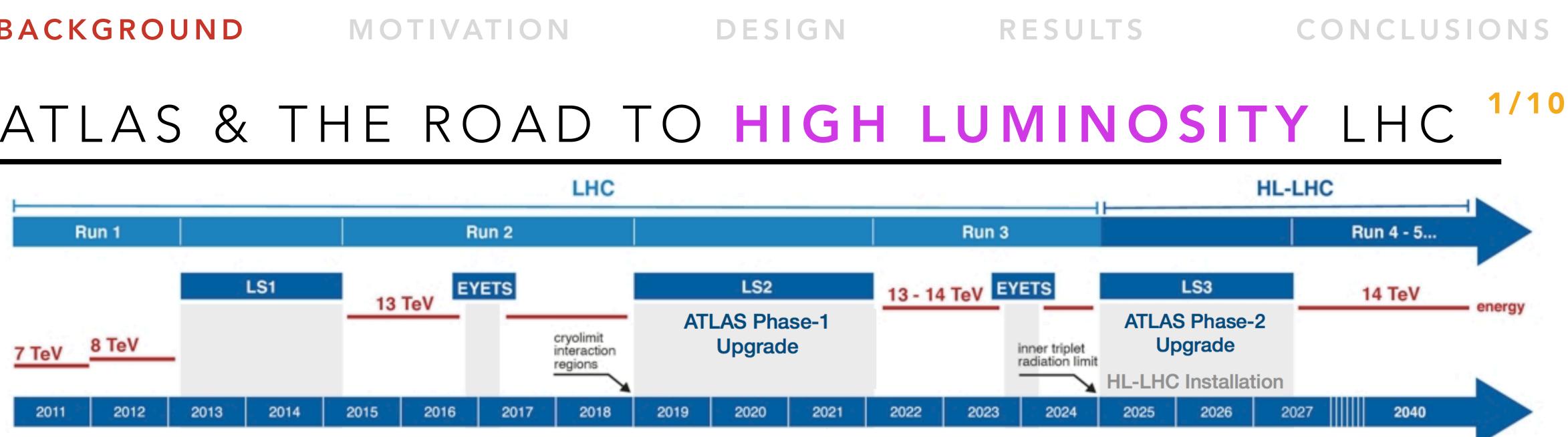

## ATLAS & THE ROAD TO HIGH LUMINOSITY LHC

FIG 1: PROJECT SCHEDULE OF LHC/HL-LHC PLAN [1]

- protons at  $\sqrt{s} = 14$  TeV and with a peak luminosity of  $7.5 \times 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>.

- As a result, detectors in the LHC ring like ATLAS need to undergo upgrades necessary to maintain good physics performance in the HL-LHC environment.

- One of these upgrades deals with the LAr calorimeter system carried out in 2 phases: Trigger: A more discriminating trigger<sup>†</sup> (and hence a readout system<sup>‡</sup>) is needed in a higher pileup environment.

- Radiation: Planned radiation dose exceeds capacity of existing readout system

• The Large Hadron Collider is due to undergo major design changes with the goal of colliding

† Planned for Phase I upgrade

**‡** Planned for Phase II upgrade

BACKGROUND

MOTIVATION

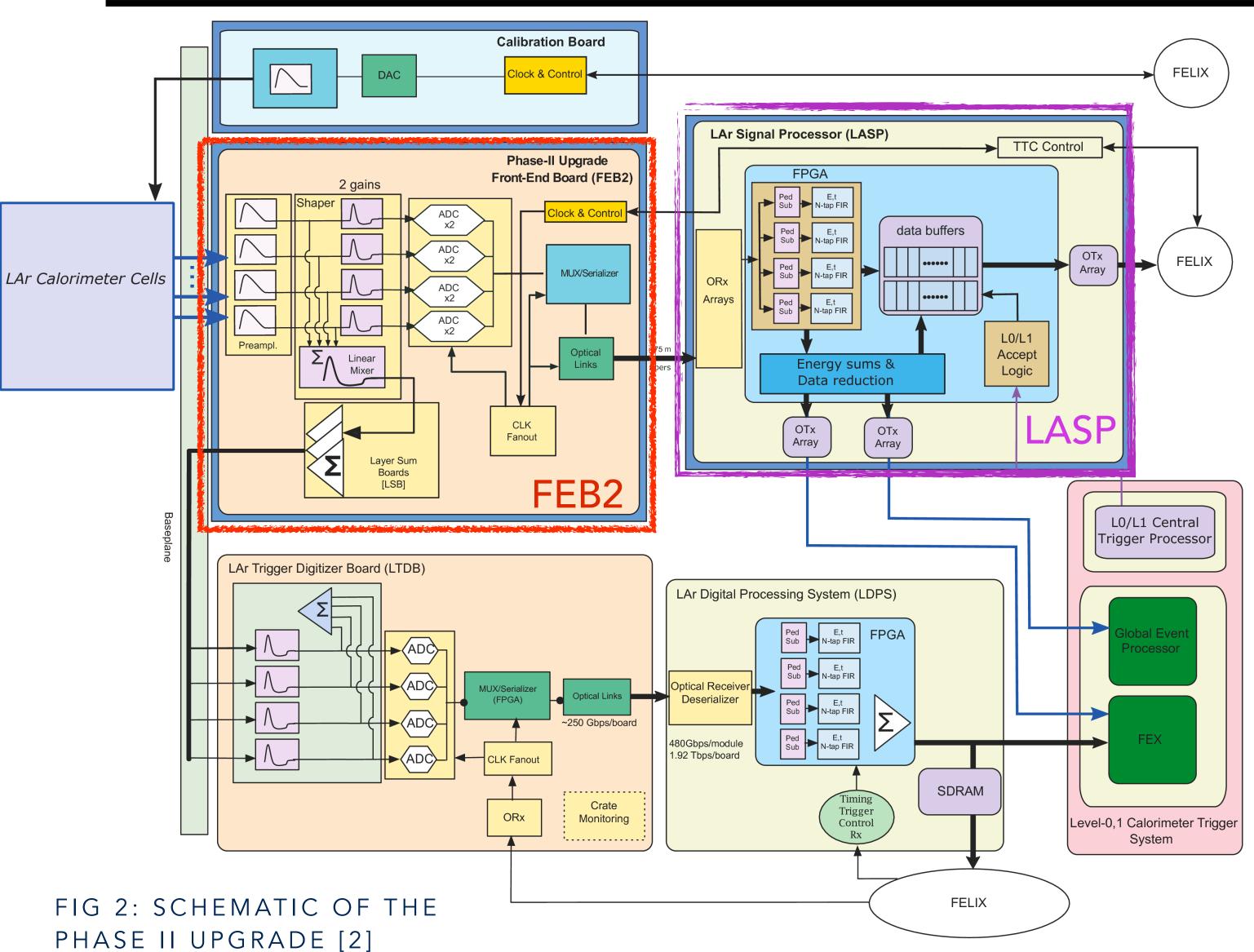

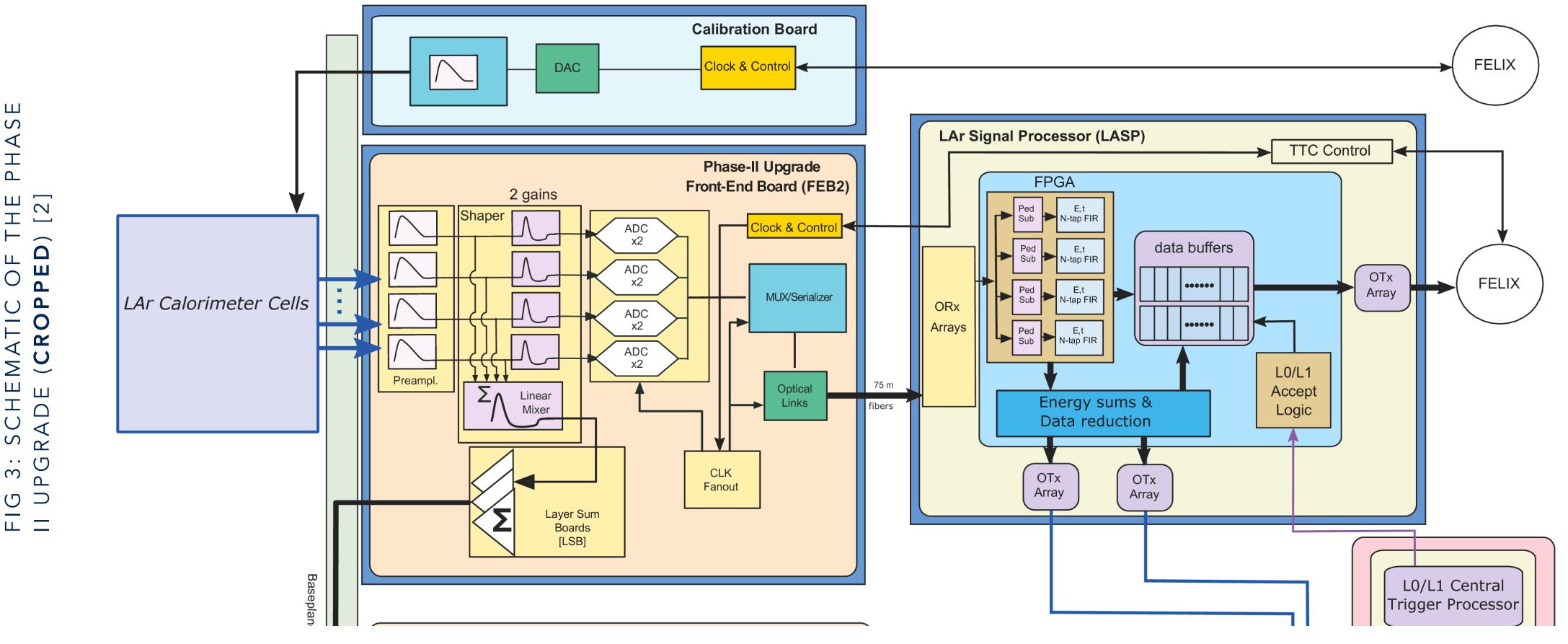

## LAR ELECTRONIC UPGRADES

Two major changes are planned for Phase II LAr Electronics upgrade

**1**. FEB2 (Front End Board 2)

Signals passed through an analogue filter shaper for two different gains (high & low gain) ADC digitize this into 16-bit words A serialized stream is sent to the LASP at 10.24Gbps using CERN-based lpGBT chips.

(LAr Signal 2. LASP **Processor**

LASP, **built on an FPGA**, will then

calculate energy/time of pulses \*

- transmit data to the trigger & DAQ ₩

- Buffer data until trigger decision \*

MOTIVATION

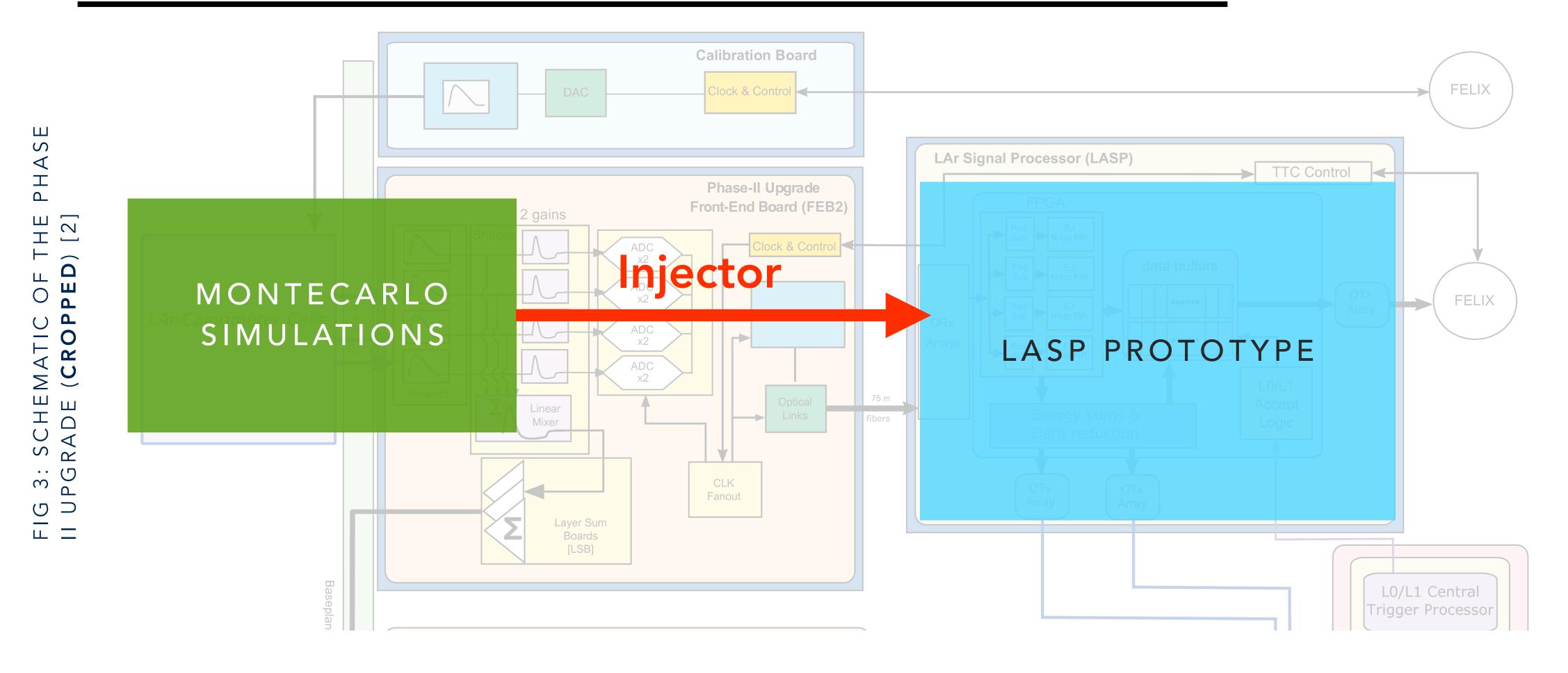

### THE NEED FOR AN INJECTOR

- Signals from the calorimeter and the FEB2 will not be available as the LASP is developed

- Montecarlo simulations can mimic FEB2 pulses for different physics events

- As the LASP is being developed, it needs to be tested with external test cases to verify operation.

### DESIGN

RESULTS

### CONCLUSIONS

MOTIVATION

## THE NEED FOR AN INJECTOR

- Thus, we need a data injector that will input pulses similar to those expected from the FEB2s

### DESIGN

RESULTS

### CONCLUSIONS

• As the LASP is being developed, it needs to be tested by external test cases to verify operation.

MOTIVATION BACKGROUND

## REQUIREMENTS FOR THE INJECTOR

• The Injector project is an integral part of the LASP test-bench.

"The data injector shall provide, with the highest fidelity, 22 channels of lpGBT payloads transmitted at 10.24 Gbps every 40 MHz. The payload should be user-controlled which can help test the LASP for different cases. Data injection should occur for as long as possible"

- → 10.24 Gpbs: lpGBT transmission speed → Highest fidelity: Ability to maintain transmission accuracy → 40 MHz: Bunch crossing frequency of LHC

- → 22 channels: 22 independent streams of data

- → **IpGBT payloads**: payload structure as transmitted by FEB2s i.e. 12 ADCs + 2 BCIDs

- SPECIFICATION (SUMMARIZED)

- → User-controlled: user having the ability to manipulate the values

- → As long as possible: duration of injection

## FPGAS

- (Field Programmable Gate Array)

- perform functions, while the programmable switches can be customized to provide interconnections between logic cells.

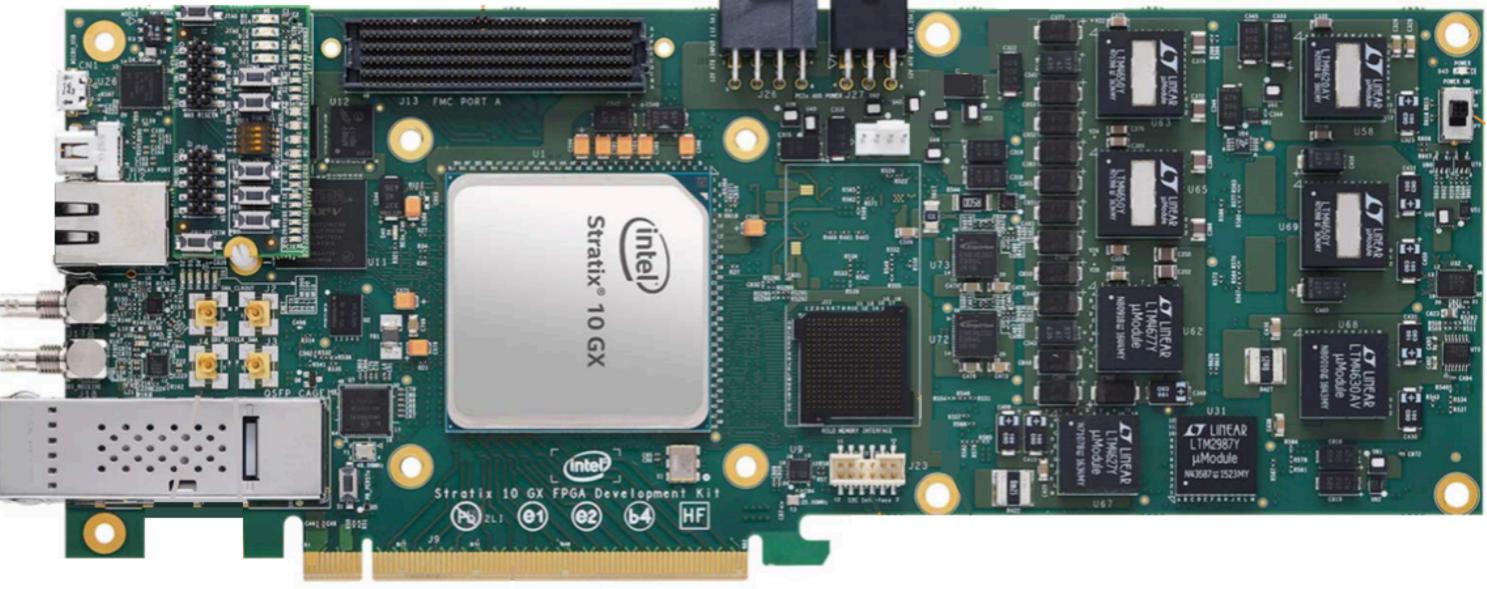

- The Injector is implemented on an Intel Stratix 10 GX FPGA board

• The Injector (and the LASP) is built on a firmware programmable integrated circuit called an **FPGA**

• FPGA devices contain logic cells and programmable switches. Logic cells can be programmed to

The Stratix 10 board has the following capabilities which are exploited for the Injector project

- ✓ 40 Gbps QSFP transceivers

- ✓ 1 Gbps Ethernet connector

- ✓ 2 GB external memory device

BACKGROUND MOTIVATION

## DESIGN SCHEME & IMPLEMENTATION

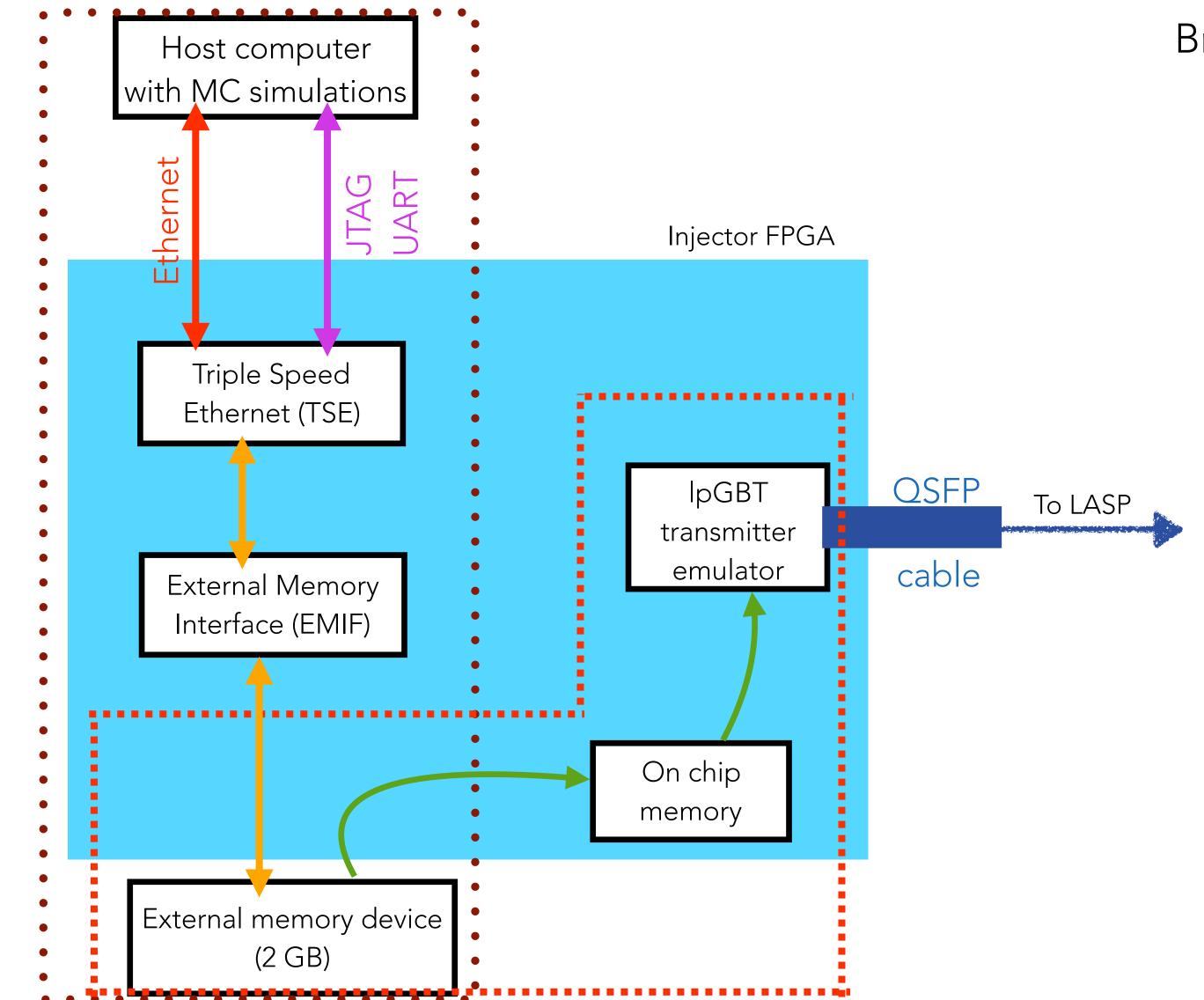

Broken down into two stages:

- 1. Transfer data from PC into storage via Ethernet using the UDP/IP protocol

- 2. Retrieval of data from storage. Packaging of data in a format that replicates the FEB2 payload

- The injector monitors incoming Ethernet frames and strips it down to provide a UDP payload only

- As a consequence, the Injector "lives" inside an Ethernet network

- Obtain the Ethernet is then stored in a 2GB External memory device.

- Once all 2GB of data is stored, the contents are retrieved, packaged and are sent to the LASP

- **M**Injection of contents can also be done manually

- Injection of contents continues until user intervention

## ETHERNET DATA TRANSFER

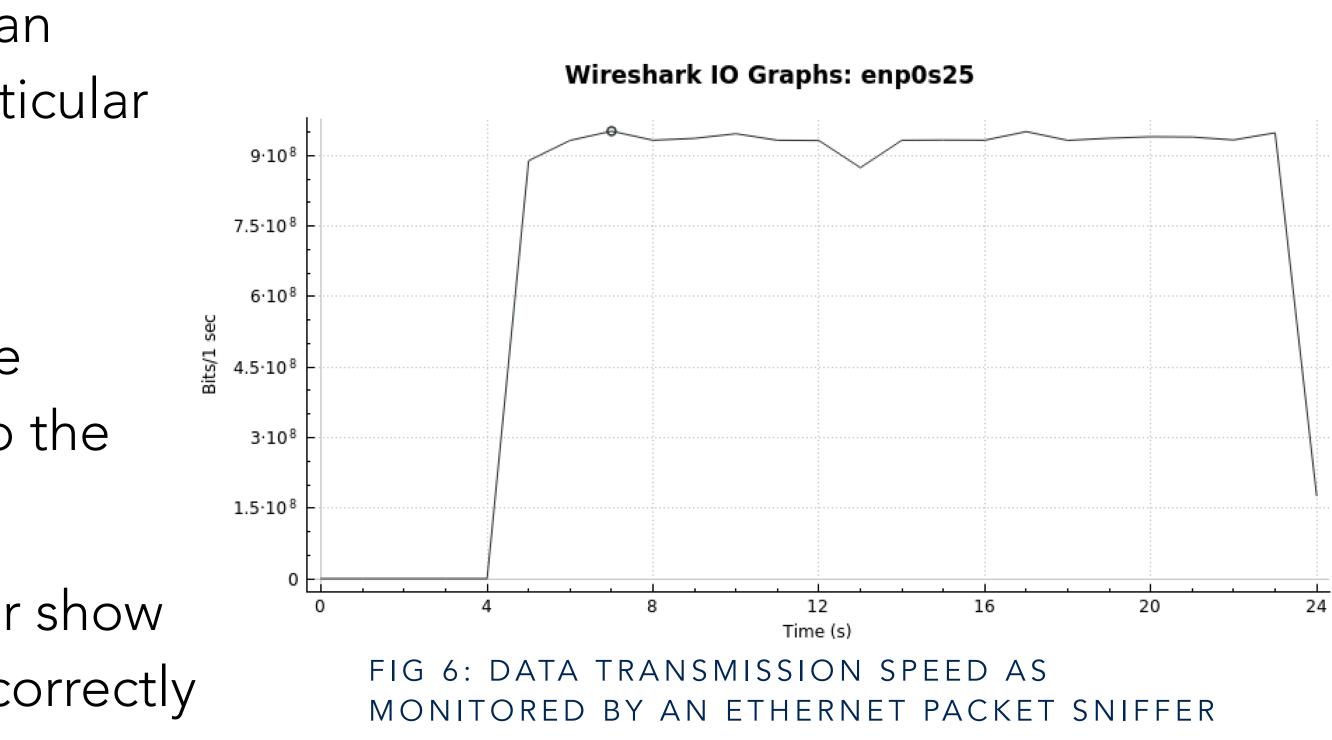

- Using a packet sniffer (e.g. Wireshark), one can intercept and monitor the traffic across a particular network.

- The injector is tested by connecting it to a moderately busy campus network switch. The workstation sending the data is connected to the same network switch.

- Dumping of contents received by the injector show that all the ethernet packets are transferred correctly

### CONCLUSIONS

The Ethernet throughput is measured @ ~930Mbps i.e. takes ~18s to send 2GB This is at the limit of the GbE protocol.

## DATA INJECTION TO LASP

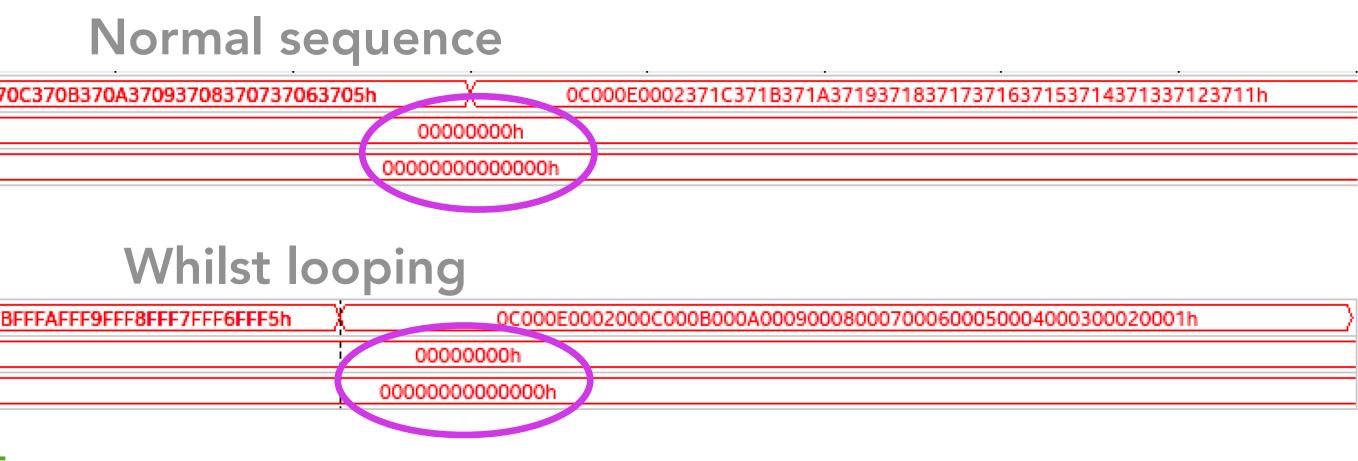

- Signals inside the FPGA can be probed and measured somewhat like an oscilloscope.

- receiving end to verify transmission accuracy

- The incoming signal from the injector as well as the error counter (checksum verification) is probed continuously.

| ر (۱ | IpgbtFpga_top_inst uplinkuserdata_o[2290]          | 0C001600023710370F370E370D370 |

|------|----------------------------------------------------|-------------------------------|

| Ĵ    |                                                    |                               |

| ۰Î   | \gen_downlink_data:verify_payload error_count[550] |                               |

|          | IpgbtFpga_top_inst uplinkuserdata_o[2290]          | 0CFFF600020000FFF | FFFFEFFFDFFFCFFB |

|----------|----------------------------------------------------|-------------------|------------------|

|          |                                                    |                   |                  |

| <b>_</b> | \gen_downlink_data:verify_payload error_count[550] |                   |                  |

|          |                                                    |                   |                  |

### Last 16 bit word = FFFF

### Transmission accuracy = 100%\*

• To verify the injection, the signals received by the LASP are monitored and are confirmed to be the same as sent by the injector. Additionally, a simple checksum is sent with every payload and recalculated at the

\* The checksum will not be able to detect a flipping of an odd number of bits. The IpGBT protocol has advanced correction features (e.g FEC) which ensures the integrity of data transmission

| 23711h |  |

|--------|--|

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

|        |  |

## CONCLUSIONS

• The Injector project is designed and built and is now being used within the LASP firmware community.

"The data injector shall provide, with the **highest fidelity**, **22 channels** of **IpGBT payloads** transmitted at 10.24 Gbps every 40 MHz. The payload should be user-controlled which can help test the LASP for different cases. Data injection should occur for as long as possible"

- → Highest fidelity: 100% transmission accuracy

- → 22 channels: Only 4 channels implemented (limited by FPGA hardware)

- → **IpGBT payloads**: 12 ADCs are extracted from the memory device ...

RESULTS

SPECIFICATION (SUMMARIZED)

- → 10.24 Gpbs: ... and are transmitted at the lpGBT speeds ...

- → 40 MHz: ... every 25 ns.

- → User-controlled: 2 GB of user-defined data

- → As long as possible: for an indefinite period

# THANK YOU!

### SPECIAL MENTION 🔌 🙏

This work has been made possible by the very gracious help and support of the following people • My supervisors - Prof. R. Keeler and Prof. R. McPherson

- Dr. Sam de Jong and the whole LASP Firmware group

### YOUR QUESTIONS/COMMENTS ARE MOST APPRECIATED

### REFERENCES

- (1) Project schedule of LHC/HL-LHC plan

- Report, 2018

- (3) Intel Corp. Intel Stratix 10 GX FPGA Development Kit User Guide, 2019

### REFERENCES

### https://project-hl-lhc-industry.web.cern.ch/content/project-schedule Accessed: May 2021 (2) The ATLAS Collaboration. ATLAS Liquid Argon Calorimeter Phase-II Upgrade Technical Design