MARCH 2021

Natalia Emriskova Stefano Mersi

# RD53A PIXEL CHIP

| RD53A Specificat       | ions                                                                     |

|------------------------|--------------------------------------------------------------------------|

| Technology             | TSMC 65 nm CMOS                                                          |

| Pixel size             | $50 \times 50 \ \mu m^2$                                                 |

| Chip size              | 20 × 11.8 mm <sup>2</sup><br>Half size of the final CMS chip             |

| Number of pixels       | $400 \times 192 = 76800$<br>Final CMS chip:<br>$432 \times 336 = 145152$ |

| Detector capacitance   | < 100 fF                                                                 |

| Leakage current        | < 10 nA                                                                  |

| (In-time)<br>threshold | (1200e <sup>-</sup> ) 600e <sup>-</sup>                                  |

| Noise hits             | < 10-6                                                                   |

| Radiation<br>tolerance | 500 Mrad at -12°C                                                        |

| Temperature            | [- 40°C; +40°C]                                                          |

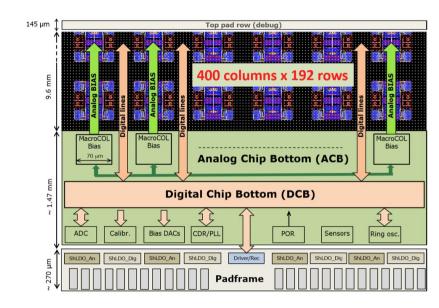

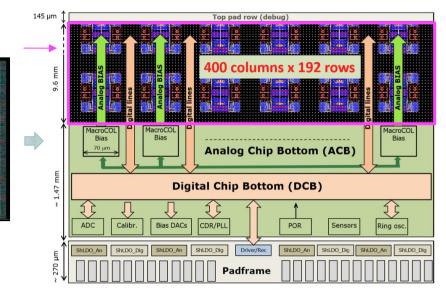

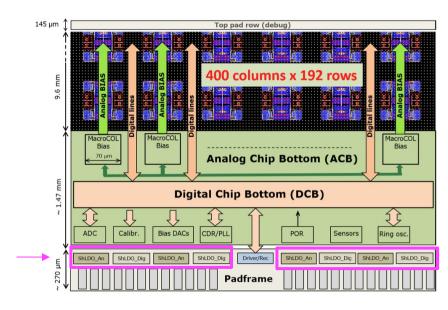

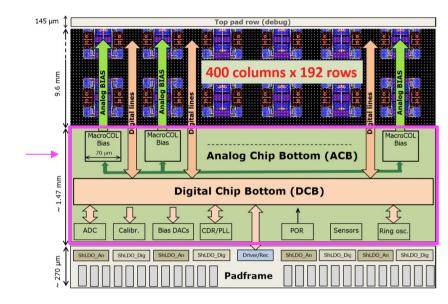

### Top test pad

- Row of test pads for debugging purposes

- Will be removed in the production chip

#### **Pixel matrix**

•  $192 \times 400 = 76800$  pixels

### **Chip Bottom**

all global analog and digital circuitry needed to bias, configure, monitor and readout the chip

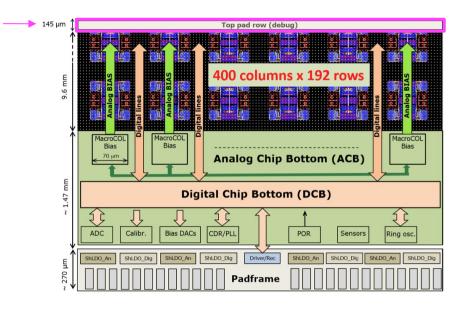

### Top test pad

- Row of test pads for debugging purposes

- Will be removed in the production chip

#### **Pixel matrix**

•  $192 \times 400 = 76800$  pixels

### **Chip Bottom**

all global analog and digital circuitry needed to bias, configure, monitor and readout the chip

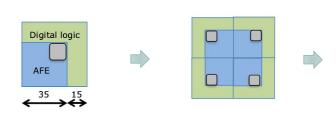

### **Pixel**

50% Analog 50% Digital + Bump pad

# **Analog** island

2×2 pixel quad

### **Pixel core**

in a fully

synthetized

digital sea

### **Pixel matrix**

All cores the same

### **Power distribution**

Power lines distributed from the bottom to the whole chip

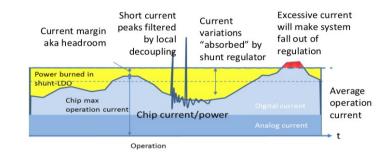

### **Serial powering**

- Baseline powering scheme for CMS and ATLAS

HL-LHC pixel detectors

- Pixel modules powered in series (chips in a module powered in parallel)

### **Shunt-LDO regulator**

- 2 Shunt-LDO regulators

(1 analog + 1 digital)

- supply constant input current independent of the load

- excess current is shunted to ground (headroom)

### **Analog chip bottom (ACB)**

- Providing current reference DACs (I<sub>ref</sub>) and voltage levels to the calibration injection circuit

- Monitoring: temperature, radiation, currents, voltages

- CDR/PLL recovers data and clock from input stream at 160 Mbps

### **Digital chip bottom (DCB)**

- Control and processing functionalities

- Input, Output and Configuration digital logic

### **Output Serializer & CML cable drivers**

- 4 Aurora lanes at 1.28 Gbps

- CML output driver with programmable preemphasis

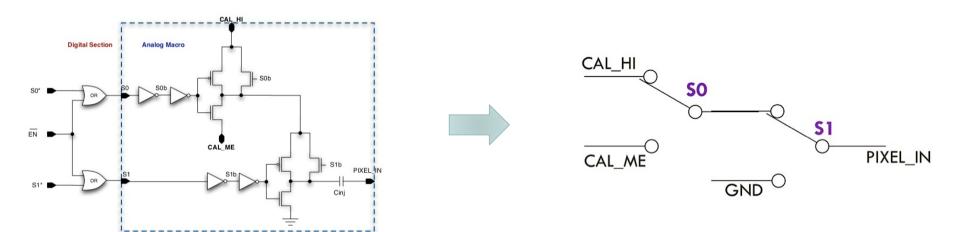

## CALIBRATION INJECTION CIRCUIT

### **Calibration injection circuit**

- Present in each pixel, picks charge from global voltage sources

- Same across the whole chip

- Equivalent to 2 switches

- controlled by 2 control signals (S0 and S1)

- switching between 3 voltage levels (CAL\_HIGH, CAL\_MED and GND)

### → injection of a known charge to pixels

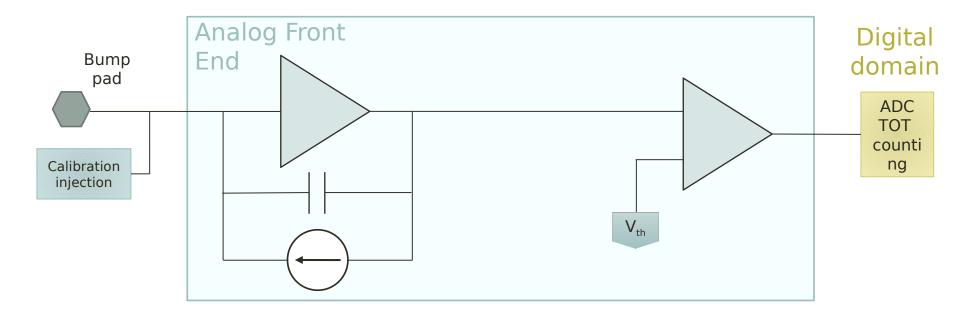

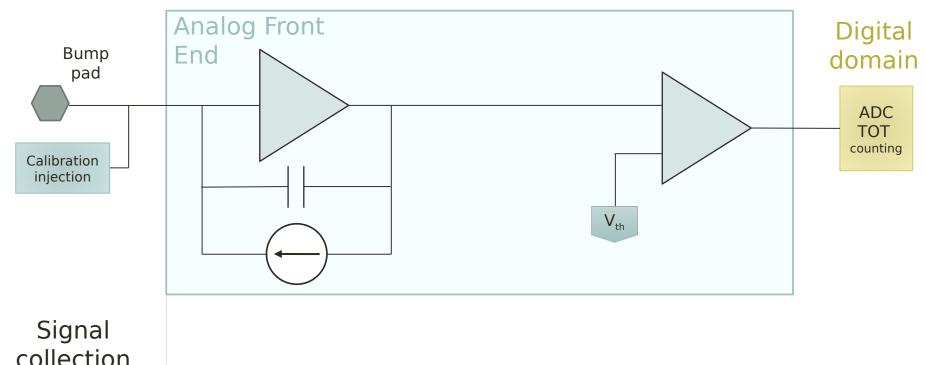

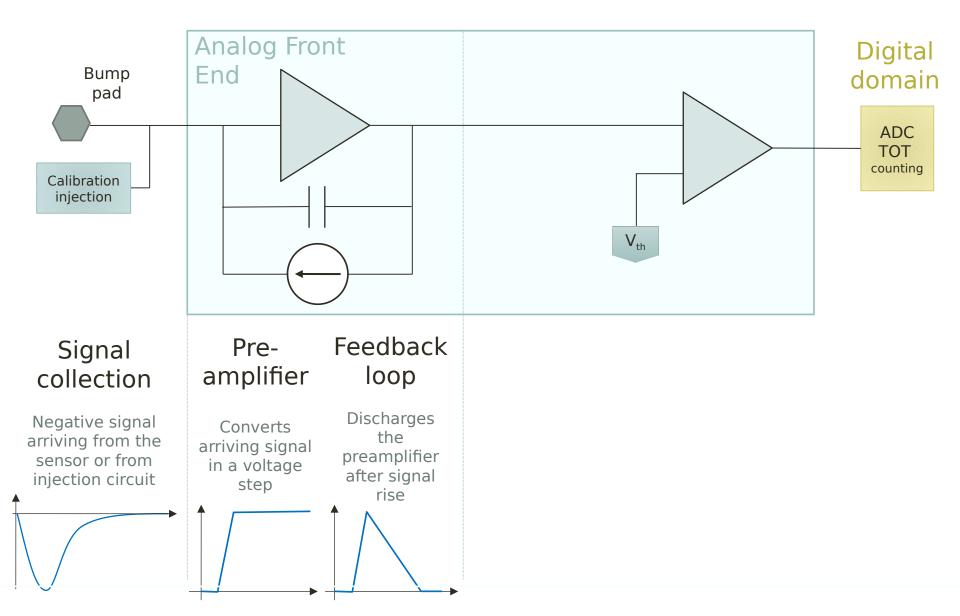

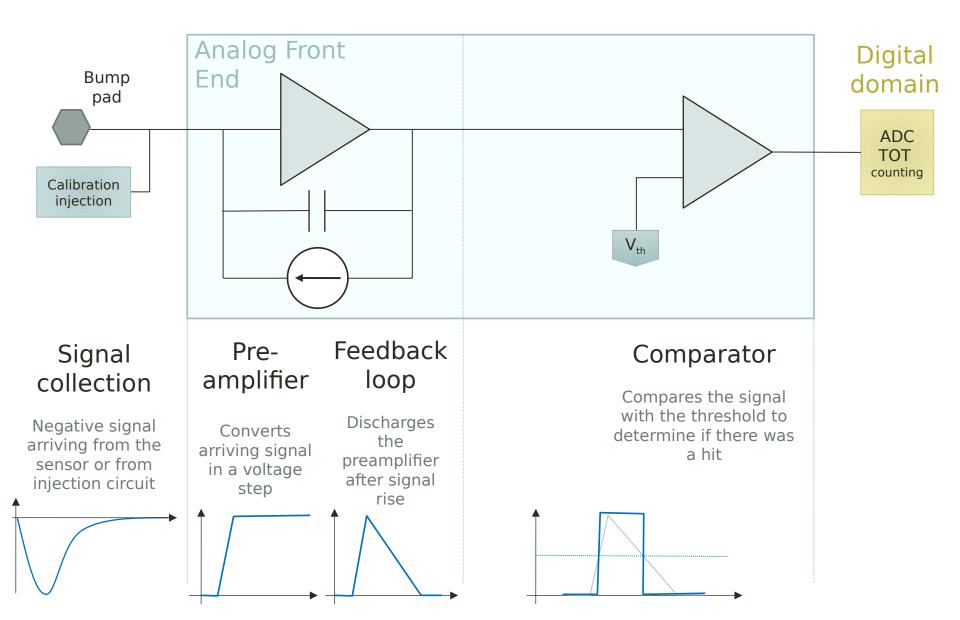

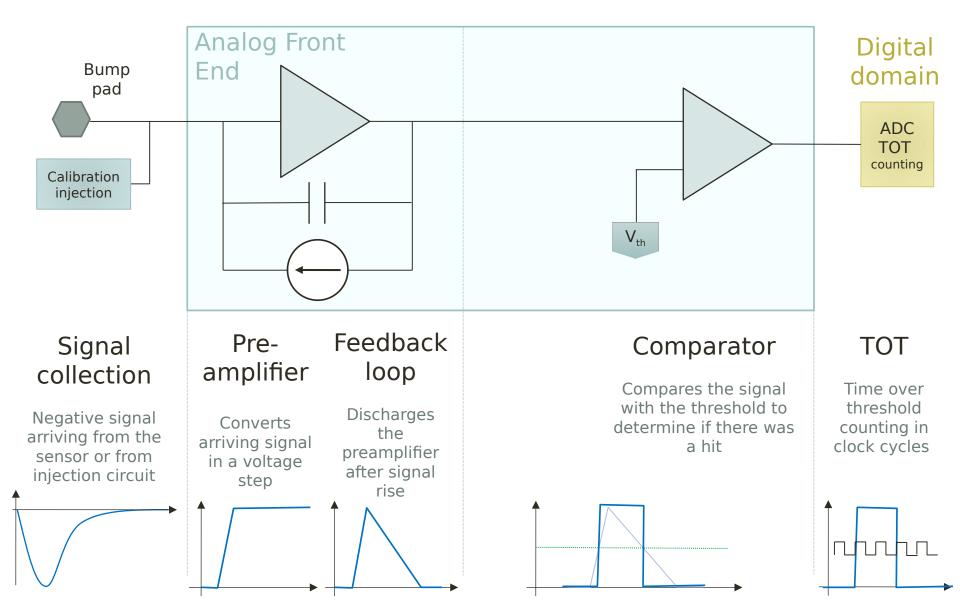

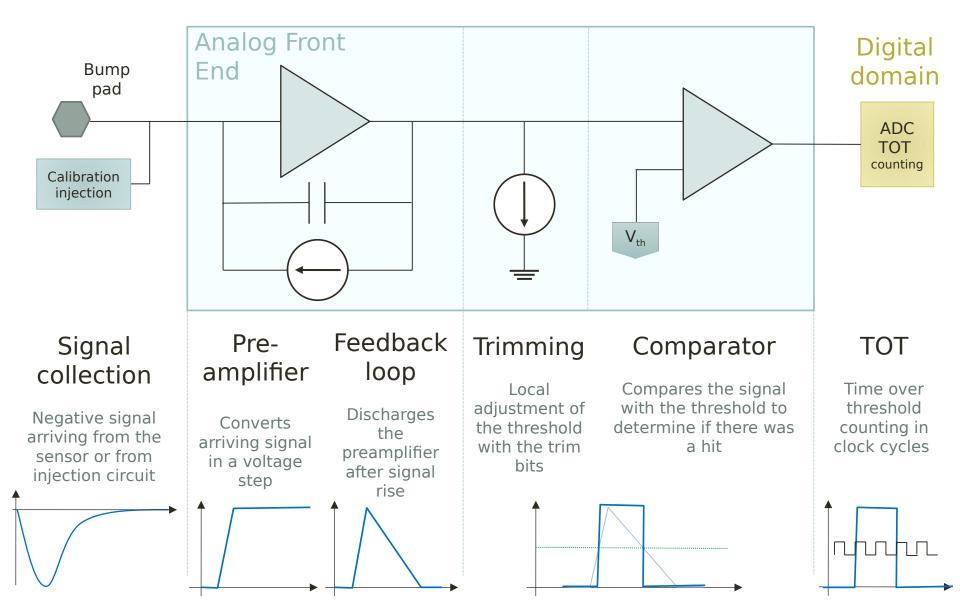

# collection

Negative signal arriving from the sensor or from injection circuit

# ANALOG FRONT-END PARAMETERS

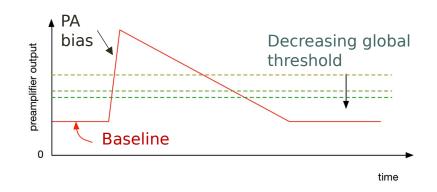

| Global threshold    | Sets the global threshold of the comparator                                                                       |

|---------------------|-------------------------------------------------------------------------------------------------------------------|

| Baseline voltage    | Sets the preamplifier output DC baseline                                                                          |

| Preamplifier bias   | Determines the speed of rise of the signal, main contribution to<br>the power consumption, influence on the noise |

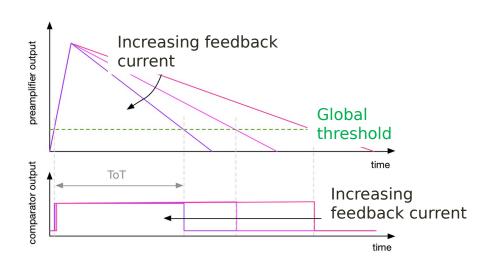

| Feedback<br>current | Determines the speed of the preamplifier return to baseline and therefore the time over threshold                 |

### TUNING PROCEDURES

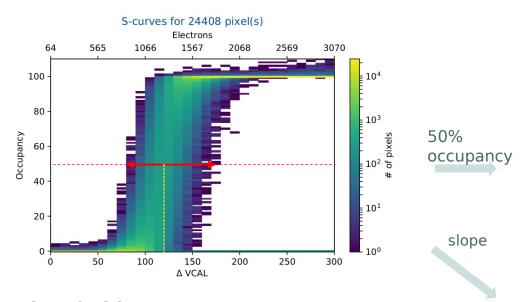

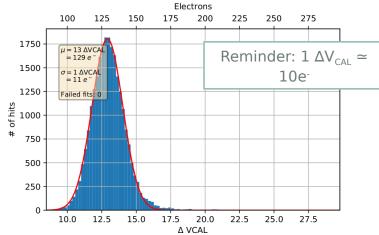

#### Threshold scan

Inject different charges, 100x to every pixel and check number of hits  $\rightarrow$  occupancy

#### **S-curves**

Occupancy vs. injected charge, for every pixel

#### **Threshold**

Charge at which 50% occupancy is reached, for every pixel

#### **Equivalent noise charge (ENC)**

Slope of the s-curve, for each pixel

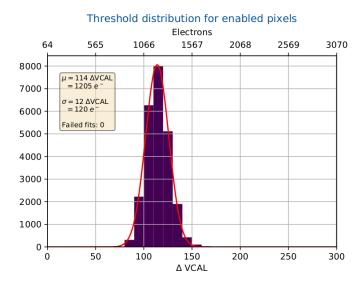

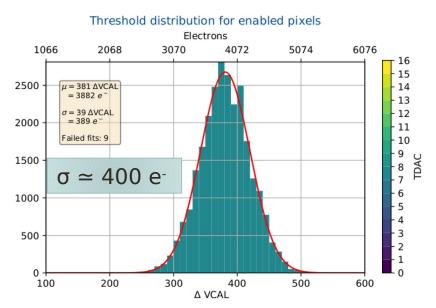

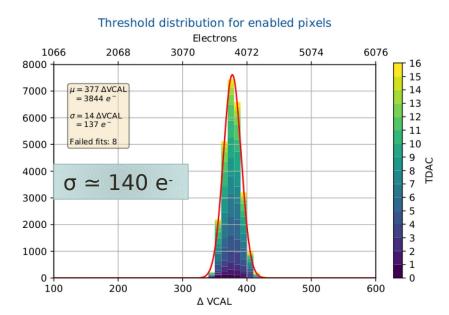

# THRESHOLD TRIMMING

• per pixel local compensation of comparator threshold dispersion

set a register in each pixel with a number of trimming bits

needed to bring local threshold as close as possible to the mean threshold

### **Before tuning**

- All trim bits set to 7

- Wide threshold distribution

### **After tuning**

- Each pixel with a different trim bit (7 as average trim)

- Narrow threshold distribution