HighRR seminar 21.04.2021

# Towards a novel, truly cylindrical, ultra-thin silicon detector for the ALICE Inner Tracker System

Bogdan Mihail BLIDARU

#### Overview

- ALPIDE @ ITS2, ALICE

- Motivation & design for ITS3

- R&D highlights

- → testbeam characterization of bent ALPIDEs

Bogdan Blidaru | HighRR seminar | 21.04.2021 | 1

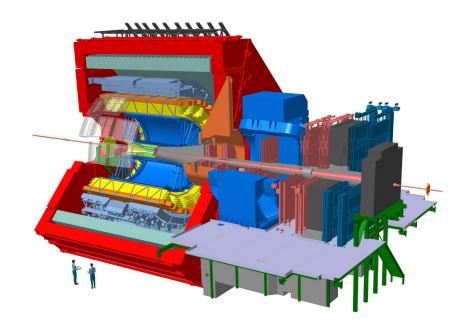

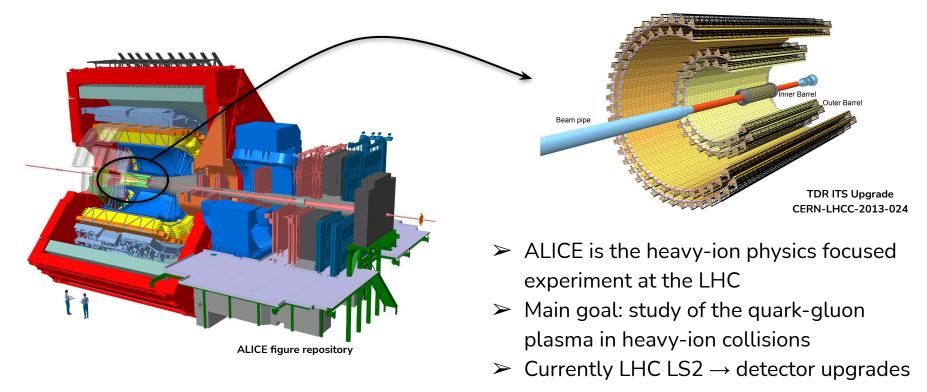

#### **ALICE** detector

- > ALICE is the heavy-ion physics focused experiment at the LHC

- ➤ Main goal: study of the quark-gluon plasma in heavy-ion collisions

- ➤ Currently LHC LS2 → detector upgrades

- Inner Tracking System 2 (ITS2)

# **ALICE detector - the Inner Tracking System (ITS2)**

#### **ALICE detector - ITS2**

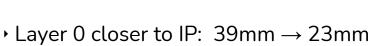

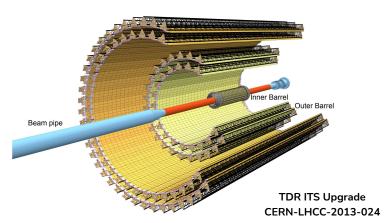

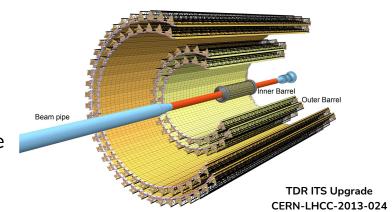

- > ITS2 (LHC LS2, currently under installation)

- Novel, MAPS based, detector design

- Seven layers of ALPIDE sensors

- Increased vertexing and tracking performance with respect to ITS

- Reduced material budget (x/ $X_0$ ) per layer: 1.14%  $\rightarrow$  0.3%

- Rate capability:  $1kHz \rightarrow 100 kHz$  (Pb-Pb)

- → Higher granularity (pixel size):  $50\times425 \,\mu\text{m}^2 \rightarrow 29\times27 \mu\text{m}^2$

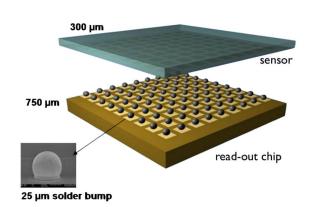

# Hybrid vs monolithic pixel sensors

ITS2

$50 \times 425 \, \mu m^2$

$29 \times 27 \mu m^2$

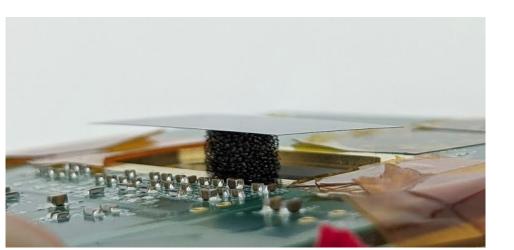

#### ALPIDE - a closer look

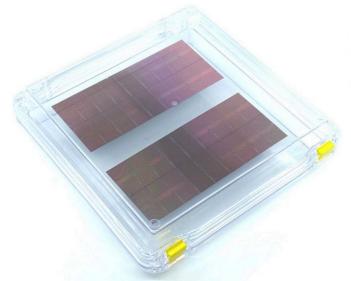

Alpide on carrier card

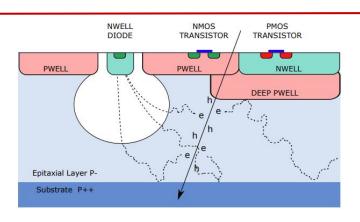

- ➤ MAPS produced in the 180nm TowerJazz CMOS IP

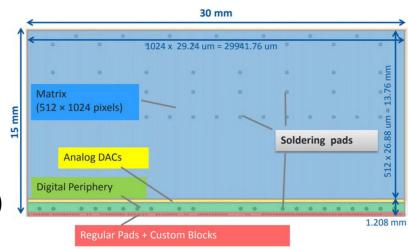

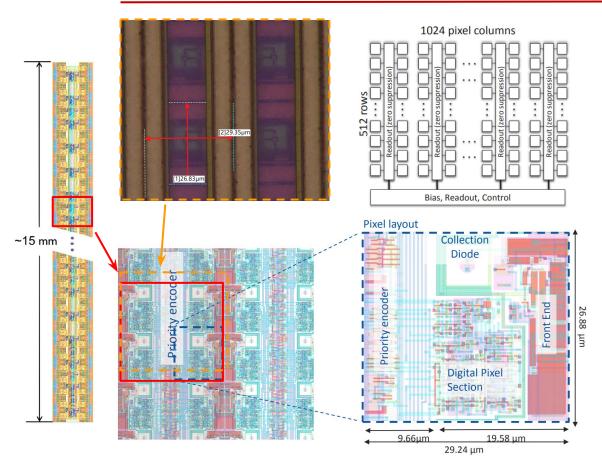

- > 30 × 15 mm<sup>2</sup> matrix of pixels

- ightharpoonup Pixel pitch 29.24 × 26.88 µm<sup>2</sup> (1024 × 512 px)

- ➤ Silicon thickness 50µm

- Spatial resolution ~5μm (required: 5μm)

- > Time resolution ~1µs

- Detection efficiency>99% (req: >99%)

- ➤ Fake hit rate

« req. 10<sup>-6</sup> /px /event

- Power consumption (7mW/cm² matrix, 150mW/cm² periphery)

~40mW/cm²

# **ALPIDE** layout features

- Readout of the pixel data from the matrix based on combinatorial readout

- ALPIDE readout is binary (hit / no hit information)

- Data transfer from matrix to periphery is zero suppressed via a priority encoder circuit

- No free running CLK distributed in the matrix, no signaling activity if no hits to read

Very low power consumption!

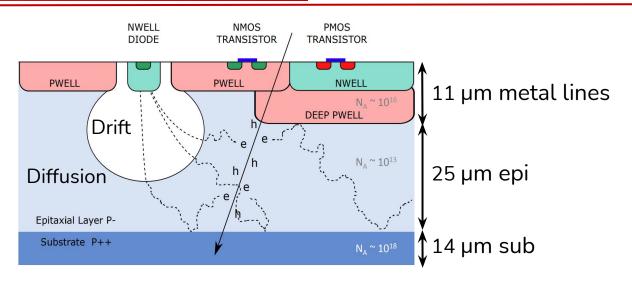

## **ALPIDE** - the pixel

- Charge is created in the high resistivity (>1k $\Omega$ cm) epitaxial layer (half the sensor thickness)

- Highly doped P substrate and PWELLs act as reflective barriers and contain the charge

- Deep PWELL shields NWELLs, allowing PMOS transistors (full CMOS within active area)

- Small NWELL diode (2µm diameter)  $\rightarrow$  low capacitance (2fF)  $\rightarrow$  large S/N

- Reverse bias (-3V) used to increase depletion of the diode

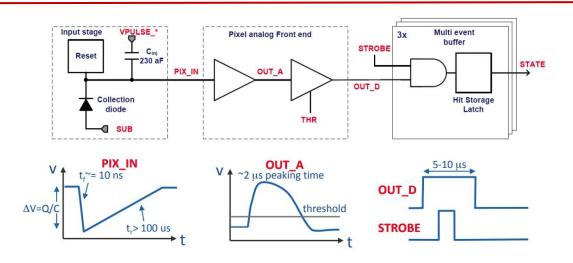

# ALPIDE - the pixel; signal processing

- Charge is collected, amplified, discriminated and strobed to in-pixel memory

- The analogue front-end is continuously active (non-linear response); it acts as analogue delay line; rise-time (<2μs) defines time resolution</p>

- Global shutter (STROBE) latches discriminated hits to memory

#### **ALICE detector - ITS2**

- > ITS2 (LHC LS2, currently under installation)

- Novel, MAPS based, detector design

- Seven layers of ALPIDE sensors

- Increased vertexing and tracking performance with respect to ITS

- ► Layer 0 closer to IP:  $39mm \rightarrow 23mm$

- Reduced material budget (x/ $X_0$ ) per layer: 1.14%  $\rightarrow$  0.3%

- Rate capability:  $1kHz \rightarrow 100 \text{ kHz}$  (Pb-Pb)

- → Higher granularity (pixel size):  $50\times425 \,\mu\text{m}^2 \rightarrow 29\times27\mu\text{m}^2$

- ITS2 is a state of the art MAPS detector

- Further improvements are possible

#### **ALICE detector - ITS3**

- ITS2 (LHC LS2, currently under installation)

- Novel, MAPS based, detector design

- Seven layers of ALPIDE sensors

- Increased vertexing and tracking performance with respect to ITS

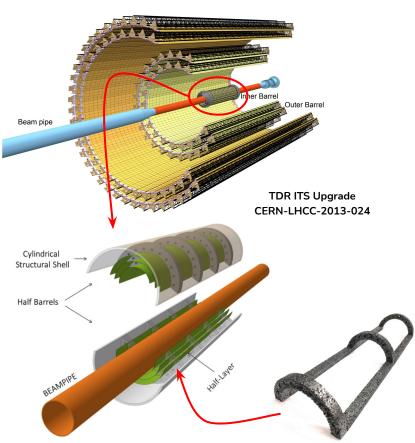

- ITS3 (LHC LS3, 2025-2027)

- Aim: replace the three ITS2 IB layers

- Ultra-light, wafer-scale, curved sensors

- Currently: R&D based on bent ALPIDE

- First testbeam results with bent ALPIDE

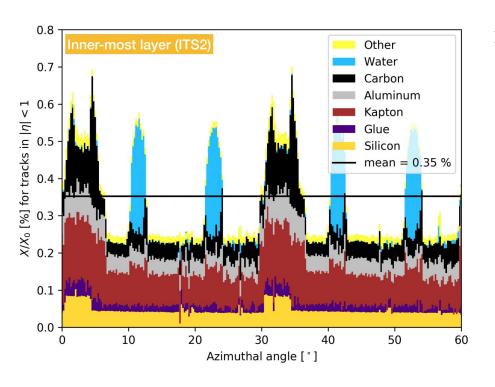

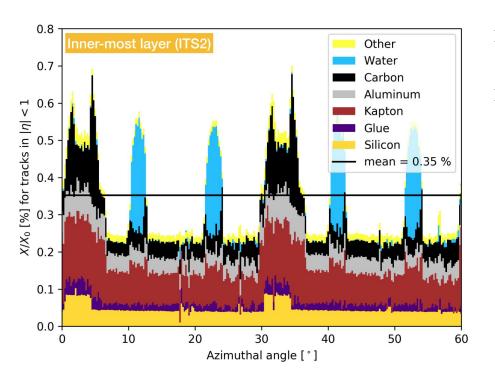

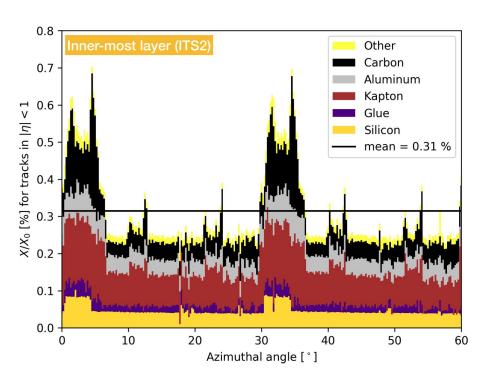

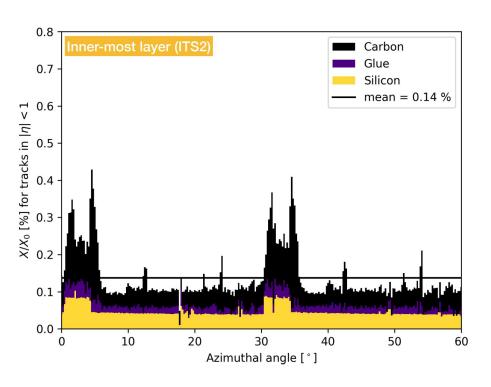

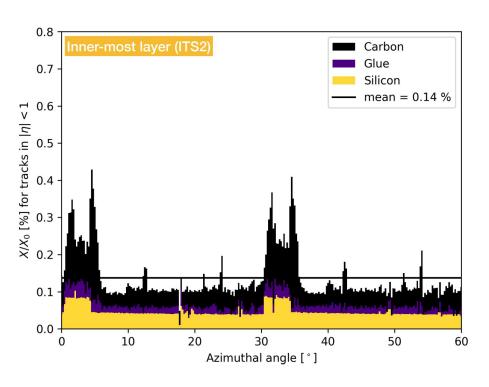

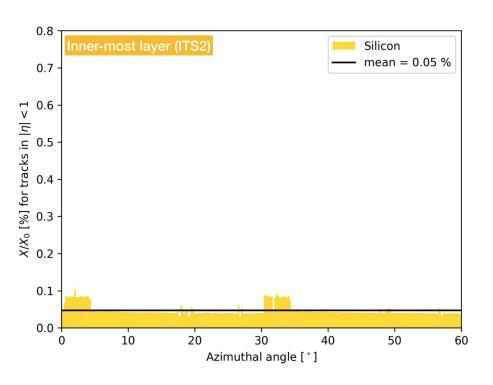

➤ Si accounts for **1/7**<sup>th</sup> of the total material (irregularities due to support/cooling)

- Si accounts for 1/7<sup>th</sup> of the total material (irregularities due to support/cooling)

- Removal of water cooling possible

- $\rightarrow$  if power consumption < 20 mW/cm<sup>2</sup>

- Si accounts for 1/7<sup>th</sup> of the total material (irregularities due to support/cooling)

- > Removal of water cooling possible

- $\rightarrow$  if power consumption < 20 mW/cm<sup>2</sup>

- Si accounts for 1/7<sup>th</sup> of the total material (irregularities due to support/cooling)

- Removal of water cooling possible

- $\rightarrow$  if power consumption < 20 mW/cm<sup>2</sup>

- Removal of the circuit board for power distribution and data lines possible

- → if integrated on chip (make single large chips, use CMOS metal layers)

- Si accounts for 1/7<sup>th</sup> of the total material (irregularities due to support/cooling)

- Removal of water cooling possible

- $\rightarrow$  if power consumption < 20 mW/cm<sup>2</sup>

- Removal of the circuit board for power distribution and data lines possible

- → if integrated on chip (make single large chips, use CMOS metal layers)

- ➤ Si accounts for **1/7**<sup>th</sup> of the total material (irregularities due to support/cooling)

- ➤ Removal of water cooling possible

→ if power consumption < 20 mW/cm²</li>

- ➤ Removal of the circuit board for power distribution and data lines possible

→ if integrated on chip (make single large chips, use CMOS metal layers)

- ➤ Move mechanical support outside acceptance → benefit from bent Si structure (+ ultra-light carbon foam)

- Si accounts for 1/7<sup>th</sup> of the total material (irregularities due to support/cooling)

- ➤ Removal of water cooling possible

→ if power consumption < 20 mW/cm²</li>

- ➤ Removal of the circuit board for power distribution and data lines possible

→ if integrated on chip (make single large chips, use CMOS metal layers)

- ➤ Move mechanical support outside acceptance → benefit from bent Si structure (+ ultra-light carbon foam)

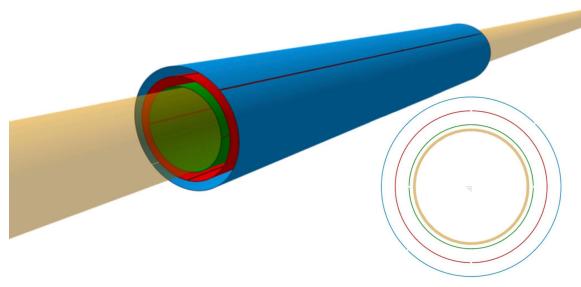

## ITS3 detector concept

| Beam pipe inner/outer radius (mm) | 16.0 / 16.5 |          |         |

|-----------------------------------|-------------|----------|---------|

|                                   | Layer 0     | Layer 1  | Layer 2 |

| Radial distance from IP (mm)      | 18          | 24       | 30      |

| Pixel sensor dimensions (mm²)     | 280×56.5    | 280×75.5 | 280×94  |

| Sensitive area length (mm)        | 300         |          |         |

| Pixel size (μm²)                  | O(10×10)    |          |         |

- Ultra thin and closer to the interaction point

- Layer 0:  $23 \rightarrow 18 \text{ mm}$

- Layer thickness:

$$0.35 \rightarrow < 0.05\% X_0$$

(beampipe:  $500\mu m$  Be 0.14%  $X_0$ )

- Uniformly distributed material (no system. errors)

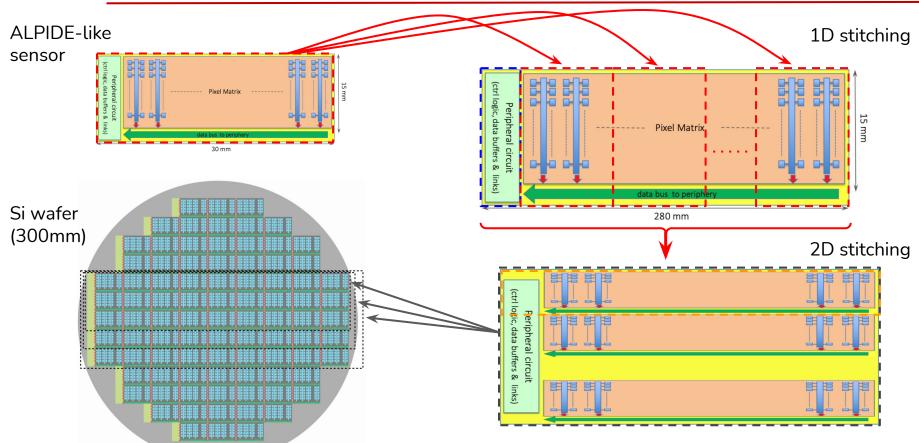

- ➤ Wafer scale ← stitching

- Layout based on air cooling

# **Architecture & stitching**

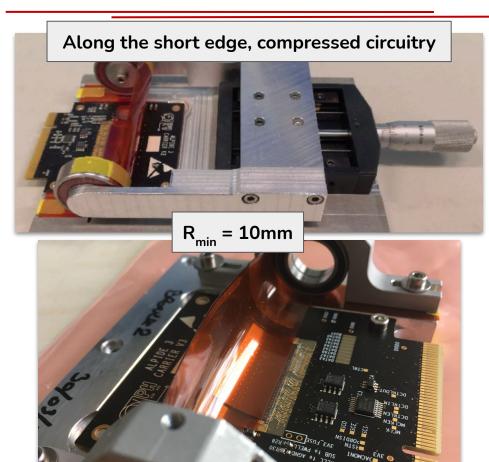

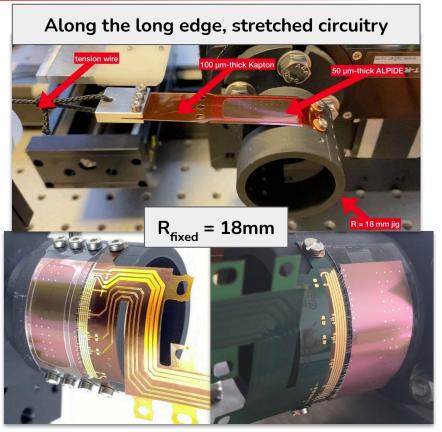

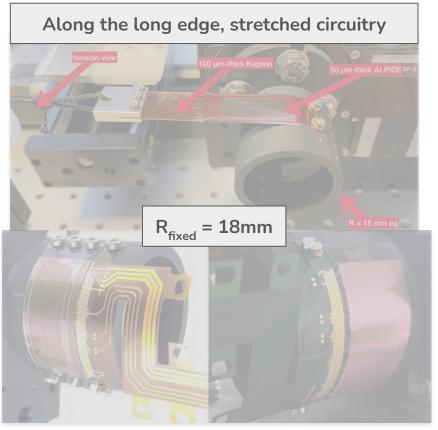

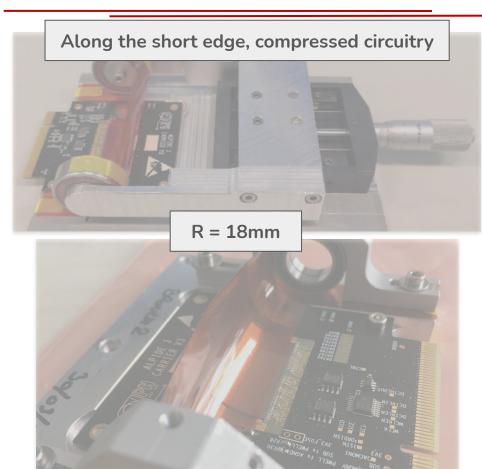

# **Bending ALPIDEs**

# **Bending ALPIDEs - part I**

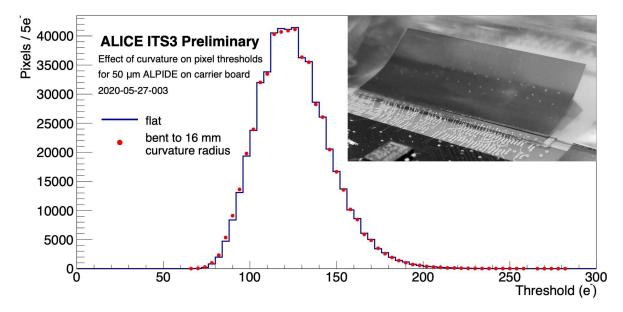

#### Bent ALPIDE - part I - electrical characterization

- Electrical performance

of the chip is

unchanged with respect

to the flat state

- Threshold and noise unchanged

- No variation in the number of dead pixels

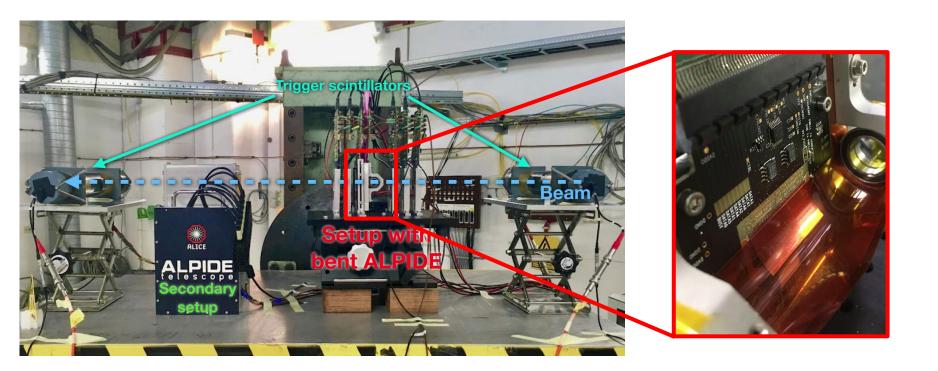

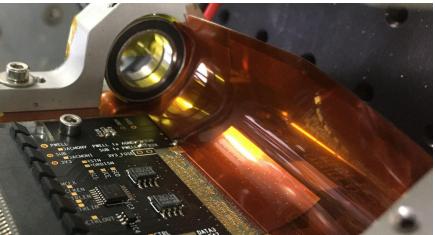

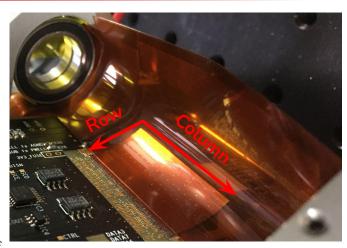

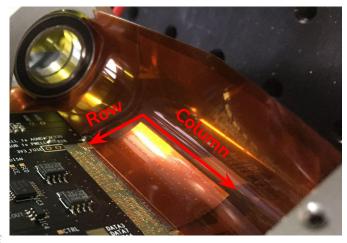

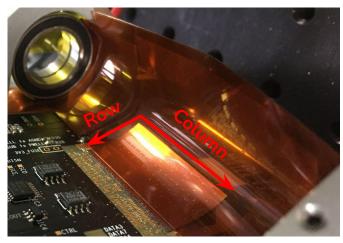

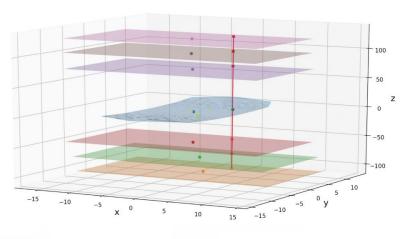

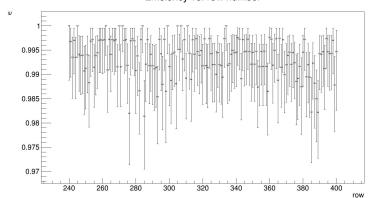

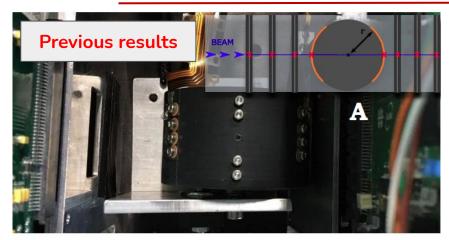

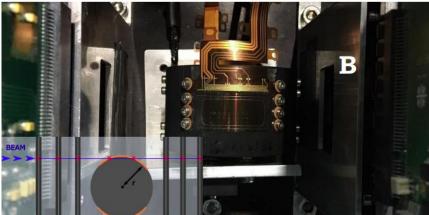

# Bent ALPIDE - part I - testbeam

- > First ever testbeam with bent silicon pixel sensors

- > 5.4 GeV e<sup>-</sup>, DESY

- > 6 flat ALPIDEs as reference planes (track reconstruction)

- > Determine: efficiency of bent sensor. position resolution

- Corryvreckan\* used for data analysis

<sup>\*</sup> https://cern.ch/corryvreckan

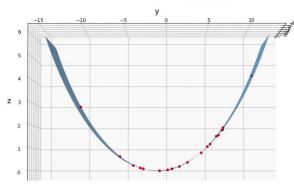

# Bent ALPIDE - part I - testbeam

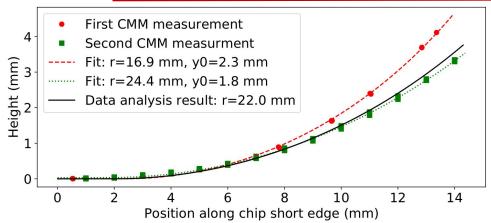

- Sensor bent to 16.9 mm measured with Coordinate Measurement Machine (CMM) before the testbeam

- Re-measured after testbeam: observed relaxation (R<sub>new</sub>=24.4mm)

- Results of the testbeam analysis show a radius of 22 ± 1 mm

- Cylindrical geometry model used to describe the bent chip

- ➤ Radius free parameter ← minimization of the residuals

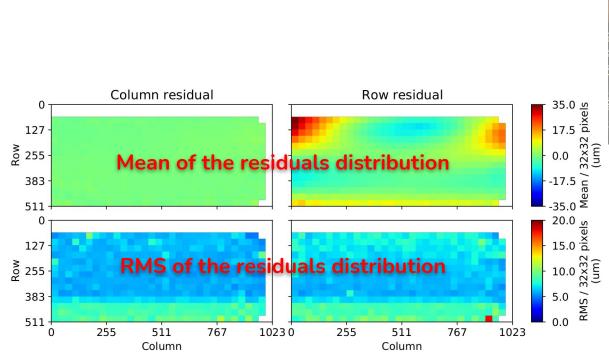

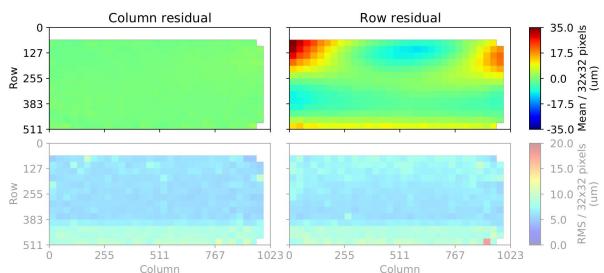

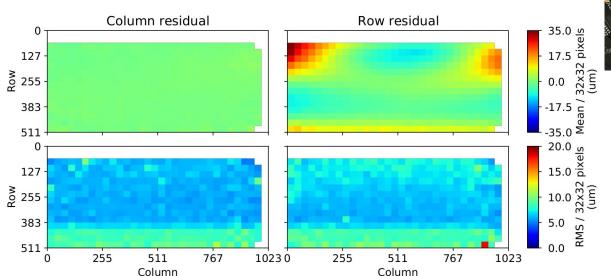

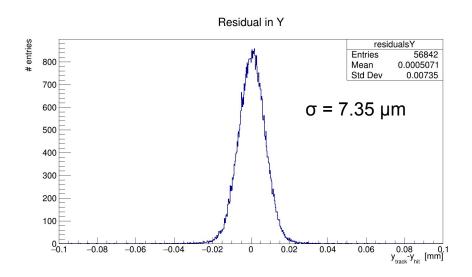

# Bent ALPIDE - part I - spatial residuals

#### Mean of the residuals distribution

- Invariant to rotation around column axis

- Row direction compatible with cylindrical geometry model up to 35 µm

#### RMS of the residuals

- Larger where the chip is glued to PCB (due to scattering)

- Row direction increase with the incident angle of the beam

#### Mean of the residuals distribution

- Invariant to rotation around column axis

- Row direction compatible with cylindrical geometry model up to 35 µm

#### RMS of the residuals

- Larger where the chip is glued to PCB (due to scattering)

- Row direction increase with the incident angle of the beam

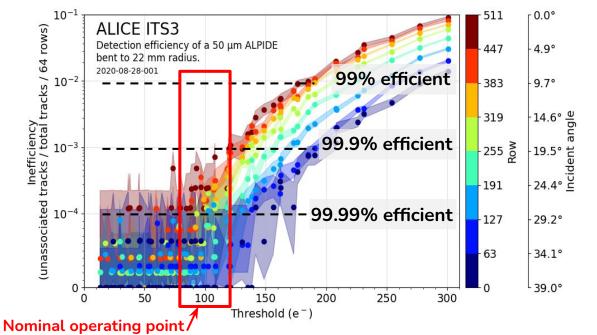

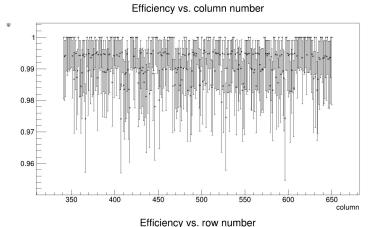

## Bent ALPIDE - part I - efficiency of bent sensor

- Inefficiency as a function of pixel threshold for various chip rows (= incident angles)

- ➤ Linear-logarithmic plot

- Only 0V back-bias!

- More than 8000 tracks per data point

- Below a threshold of 100 e<sup>-</sup>, only 1 in 10<sup>4</sup> tracks is inefficient

- ➤ Above 100 e<sup>-</sup>, the inefficiency increases with decreasing beam incident angle (increasing row number)

- Excellent detection performance retained!

- Publication under internal review

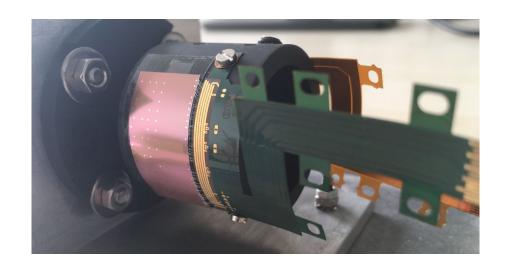

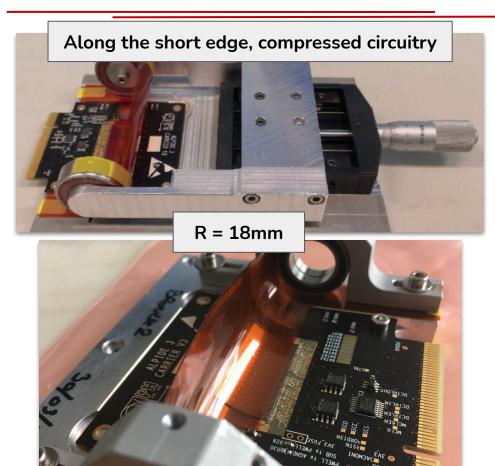

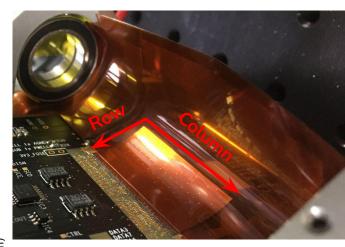

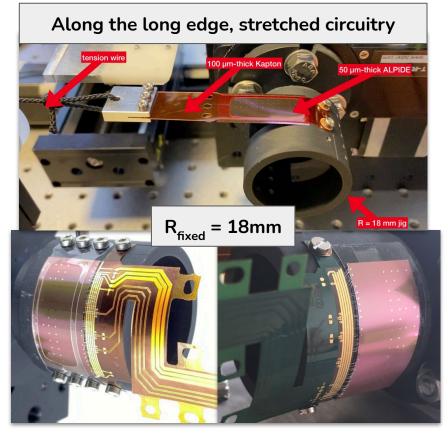

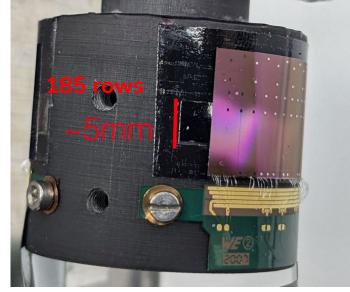

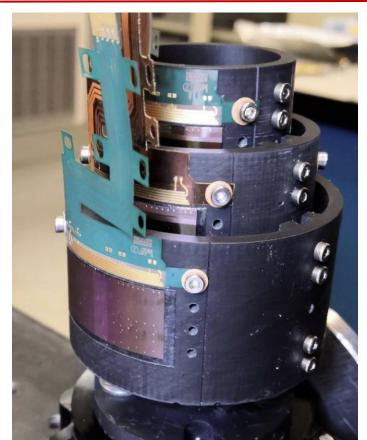

# **Bending ALPIDEs - part II**

# **Bending ALPIDEs - part II**

- More rigid construction

- ➤ Bent along the long side (decompressed circuitry) → piezoresistive effect (change in electrical resistivity)

- Connection to DAQ board done via flex-print-cable (FPC)

- Bonded after bending

- Multiple radii (18,24,30 mm), corresponding to ITS3 layers

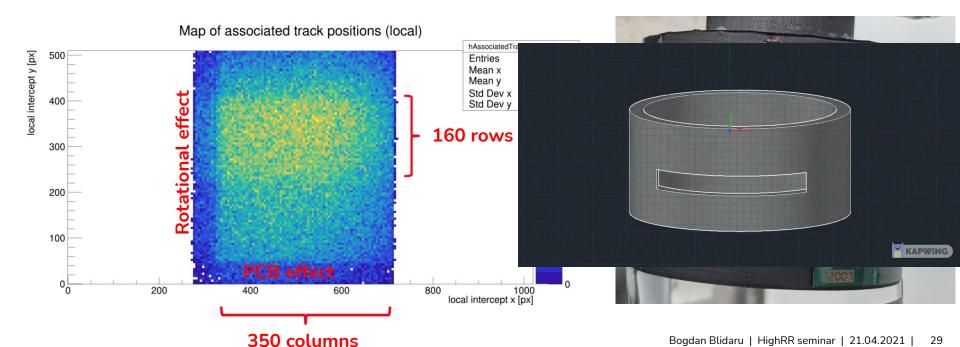

# Bending ALPIDEs - part II - new geometry

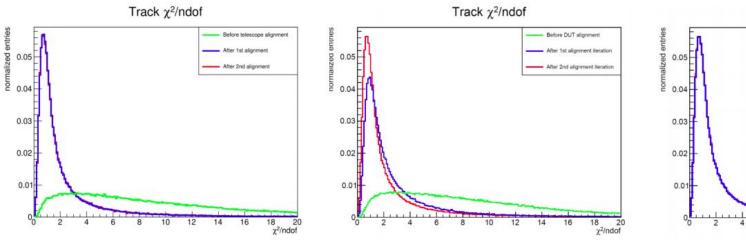

- Include cylindrical geometry in code

- ➤ Account for change of coordinate transformation (local → global)

- Correct for different z track intercept (no curved detectors previously studied)

- Ensure all DOFs are accounted for

- Check that tracks/clusters lie on the same plane

# Bending ALPIDEs - part II - tracking

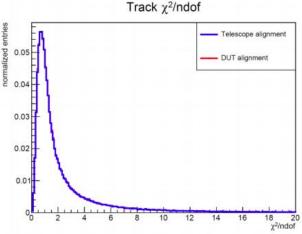

- Align telescope planes with tracks from the reference planes only

- Include and align the DUT with respect to the telescope

- Straight tracks only (not accounting for scattering)

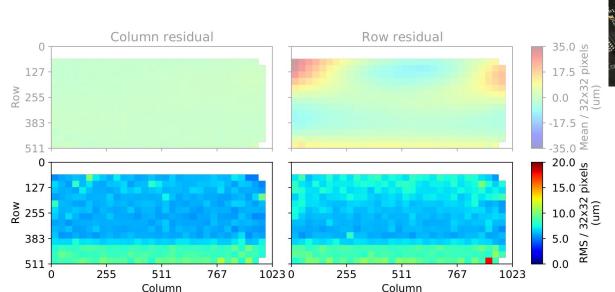

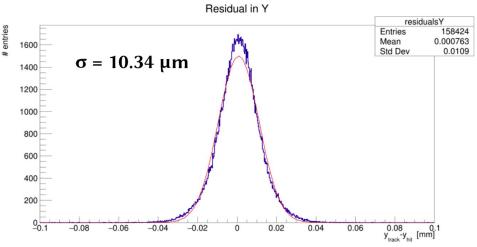

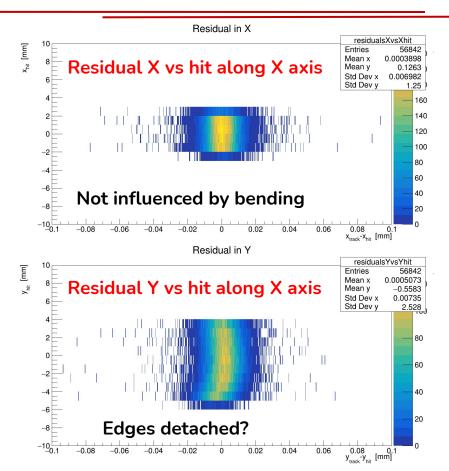

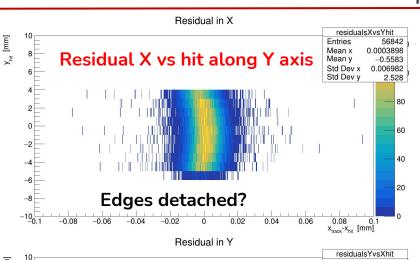

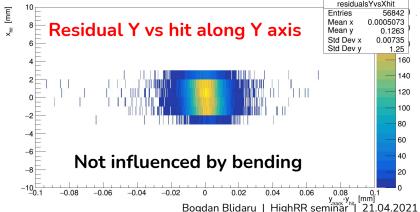

## Bending ALPIDEs - part II - spatial residuals

- Broad residuals

- Convolution of effects?

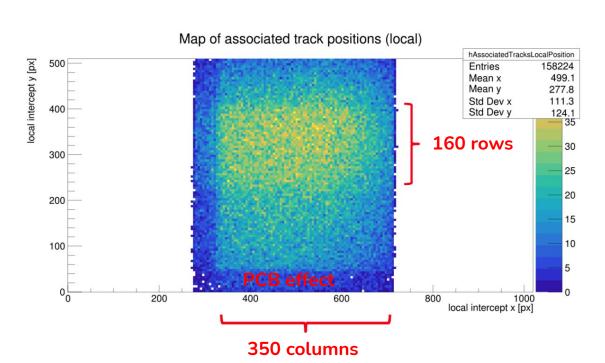

## Bending ALPIDEs - part II - ROI definition

- Tracks associated to clusters on DUT

- Region of interest (ROI) selection chose part of the sensor to characterize

# Bending ALPIDEs - part II - ROI definition

- Tracks associated to clusters on DUT

- Region of interest selection chose part of the sensor to characterize

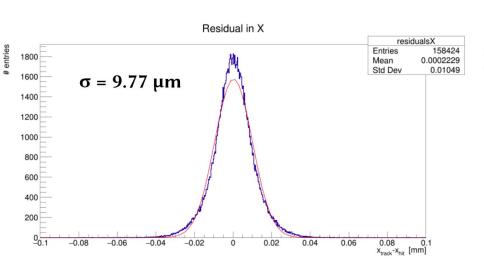

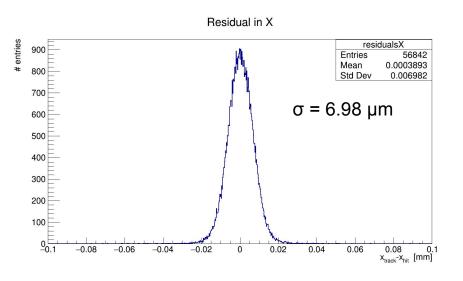

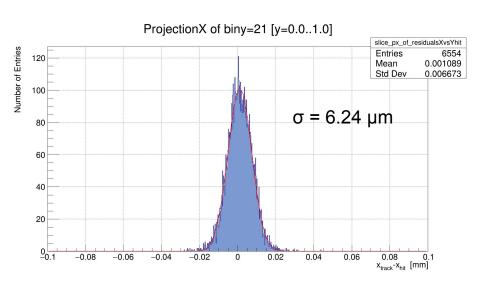

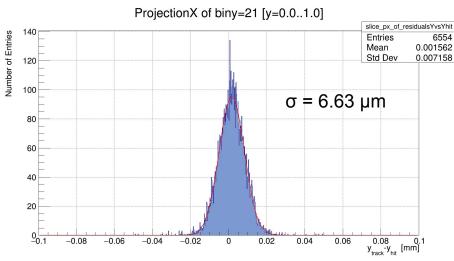

# Bending ALPIDEs - part II - residuals

## Bending ALPIDEs - part II - residuals

> Residuals are still a convolution of Gaussians, due to curvature effect

#### Bending ALPIDEs - part II - residuals

- > Residuals are still a convolution of Gaussians, due to curvature effect

- A single bin, deconvoluted ~6-7 μm

- $\triangleright$  Need to subtract telescope resolution (tracking)  $\rightarrow$  resolution  $\sim$ 5 µm

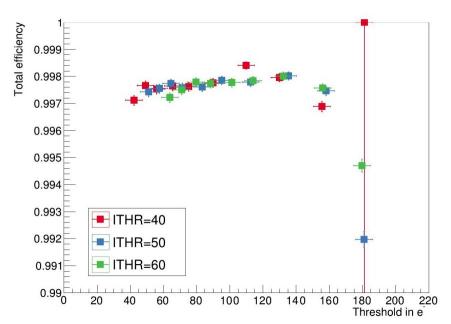

# **Bending ALPIDEs - part II - efficiency**

- Still highly efficient (@ 0V back bias)

- Efficiency decreases as a fc. of threshold (increasing number of inefficient pixels)

## Bending ALPIDEs - part II - configurations

- More than one configuration possible

- A single crossing per sensor

- B double crossing / grazing

- Example hitmap grazing events

- Can probe epitaxial layer

#### Conclusion

- ALICE proposes to build a next-generation Inner Tracking System in LHC LS3

- ightharpoonup Based on 300mm wafer scale, ultra-thin bent MAPS ightharpoonup ITS3 will push the technology even further, approaching a massless detector

- R&D started with bending current ALPIDE sensors and testing them in beam

- Laboratory and testbeam results show no performance deterioration of the sensors after bending

#### **Outlook - now!**

- - → mimics ITS3 same radii (18, 24, 30 mm)

- $\rightarrow$  4 out of 6 layers bonded, operational

- $\triangleright$  Carbon foam  $X_0$  measurement

- $\rightarrow$  measure scattering on foam, determine  $X_0$

#### Outlook - further out

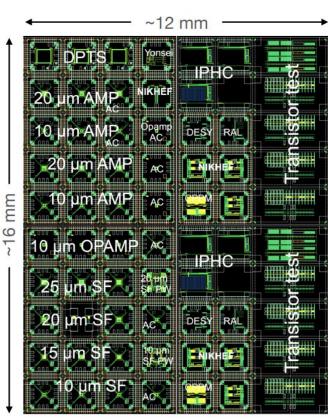

- MLR1 (Multi Layer Reticle 1)

- → chip submitted in 65 nm technology node

- → back end of May, then testing starts

- Super ALPIDE

- → 18 ALPIDE dies/ superchip

- → not stitched, but interconnected