# A Tracker detector module for particle discrimination: Hybrid design challenges

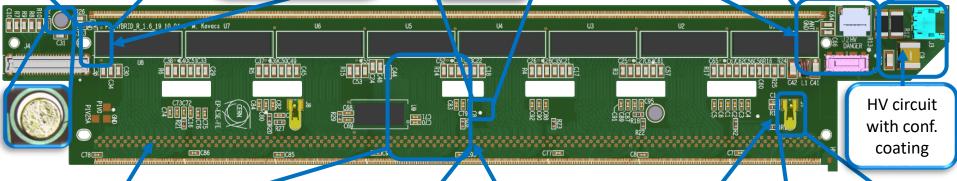

A PS-FEH-R18 prototype

Mark Istvan Kovacs on behalf of the Hybrid Working Group

Contact: mark.istvan.kovacs@cern.ch

#### **Outline:**

- 1. Introduction of CMS Phase-2 upgrade

- 2. Introduction of hybrids, architecture, build-up and design practices

- 3. History of hybrid prototypes, tests, prototype issues and solutions

- 4. Current hybrid designs for the pre-production

- 5. Hybrid testing, test system, test cards and system verification

- 6. Co-design example, conclusion of hybrid part

#### 1. Introduction of the CMS detector

The Compact Muon Solenoid (CMS) is a general-purpose detector designed to cover the widest possible range of physics at the LHC, from the search for the Higgs boson to supersymmetry (SUSY) and extra dimensions.

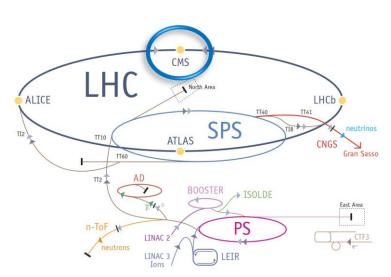

The collider complex of CERN

| Size          | 46 m long, 25 m high and 25 m wide |

|---------------|------------------------------------|

| Weight        | 7000 tonnes                        |

| Design        | barrel plus end caps               |

| Material cost | 540 MCHF                           |

| Location      | Meyrin, Switzerland.               |

CMS technical parameters

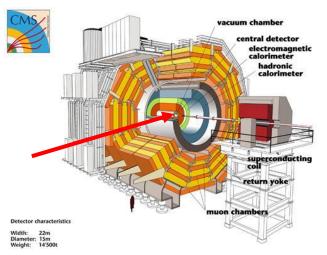

3 dimensional cross section of CMS

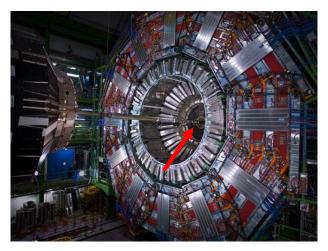

CMS in real, location of the Tracker

## 1. Introduction of CMS Phase-2 upgrade and the Tracker outer barrel

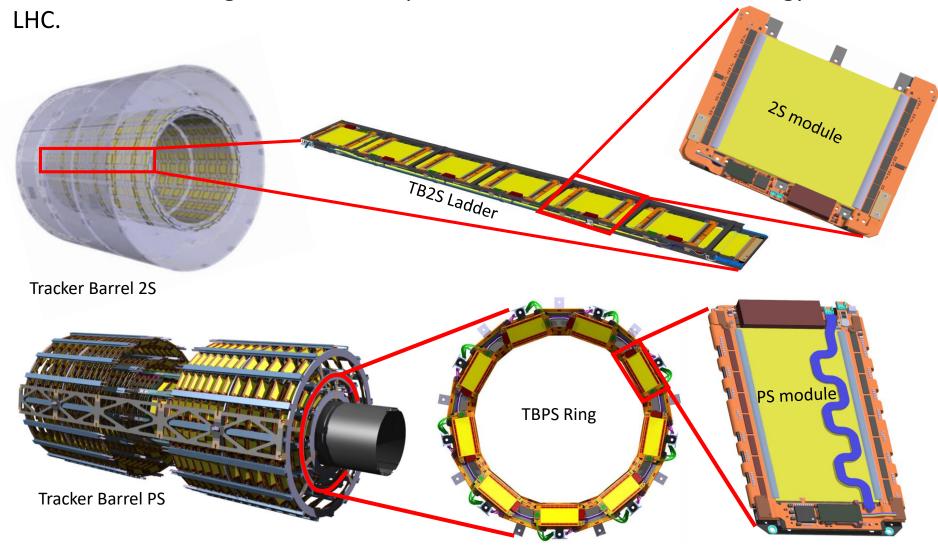

The CMS Tracker Phase-2 Upgrade is required to adapt the CMS detector to the 3000 fb<sup>-1</sup> total integrated luminosity and 14 TeV centre-of-mass energy of the HL-

**TB** – Tracker Barrel; **2S** – Strip-strip module; **PS** – Pixel-Strip module

#### 1. Introduction of the Pixel-Strip and Strip-Strip modules

Sensor module prototypes are assembled from multiple pieces, including hybrids, sensors, spacers and stiffeners, in order to validate the ASICs, circuit design and the module design.

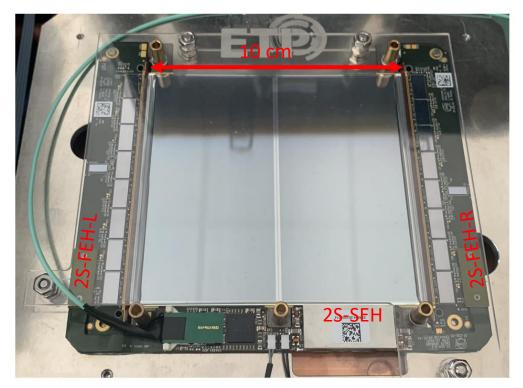

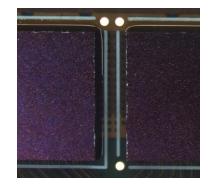

A Strip-Strip (2S) module prototype constructed from the latest hybrid prototypes.

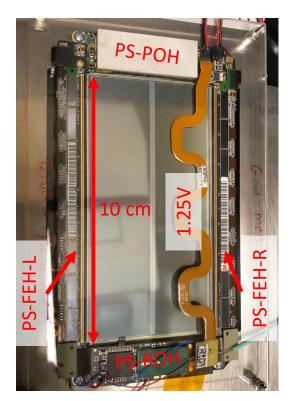

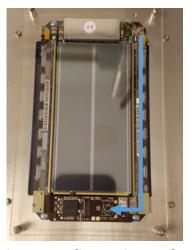

A Pixel-Strip (PS) module prototype constructed from the latest hybrid prototypes.

#### 1. Introduction – Requirements for the electronics

# The requirements for the electronics are the following:

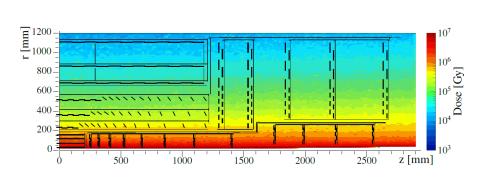

- Tolerate radiation (max. 77 and 14 Mrad expected for PS and 2S respectively).

- Reduce mass and size as much as possible.

- Reliable operation for 15 years.

- Low power consumption (~5.4W per 2S module; 7.8W per PS module[1]).

- Operation in cold, minimize heat transfer to sensors.

- Total number of modules planned: PS: 6730, 2S: 9140

Expected radiation levels in the CMS PH-2 tracker [1]

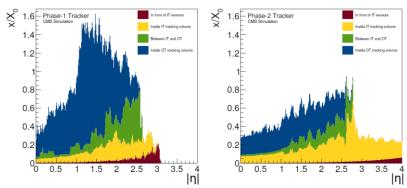

Estimated material in the upgraded CMS tracker [1]

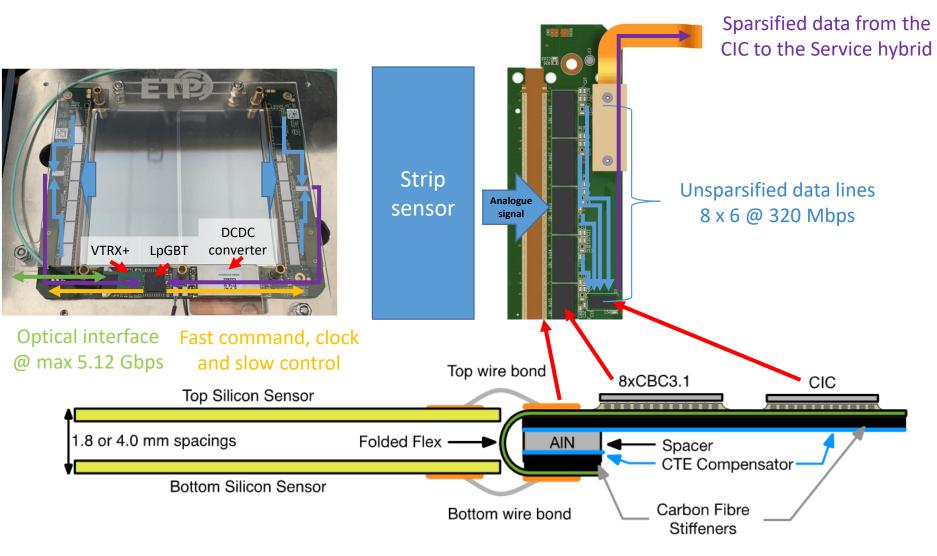

#### 2. System architecture of the 2S module

Cross section view of the 2S front-end hybrid construction in a module

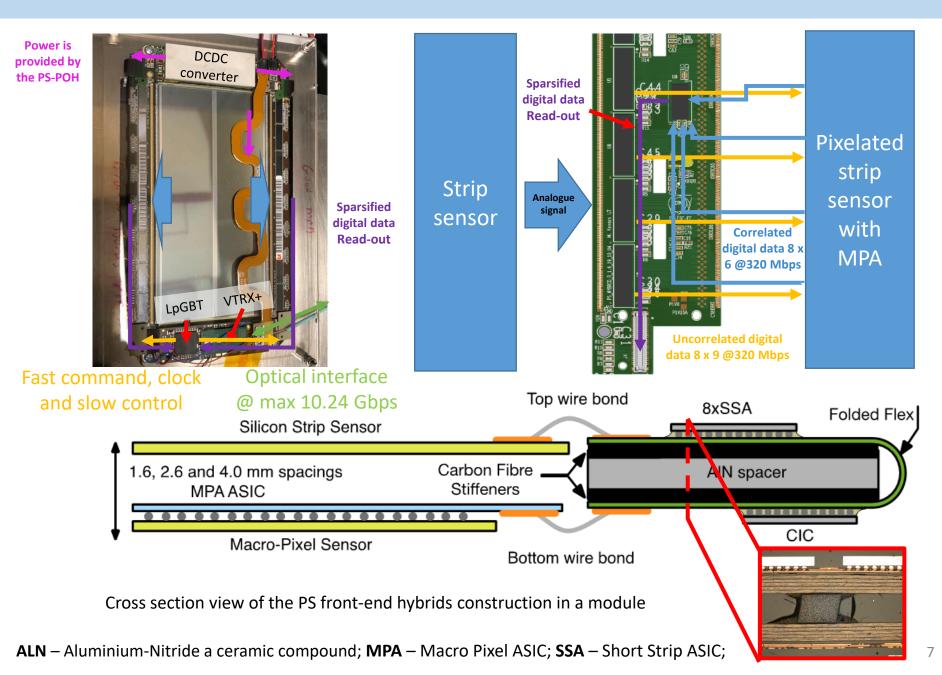

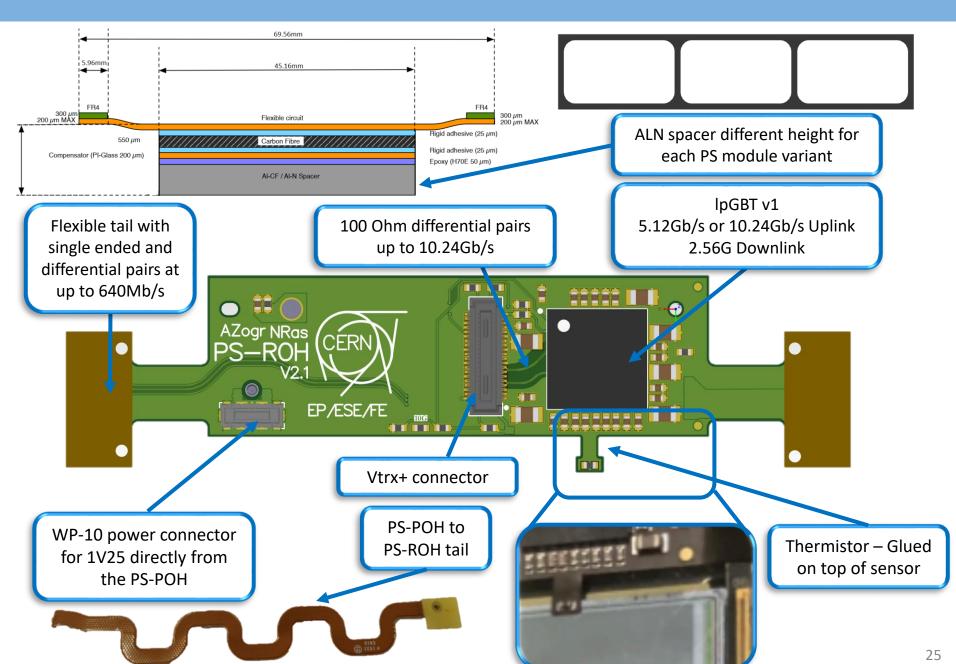

#### 2. System architecture of the PS module

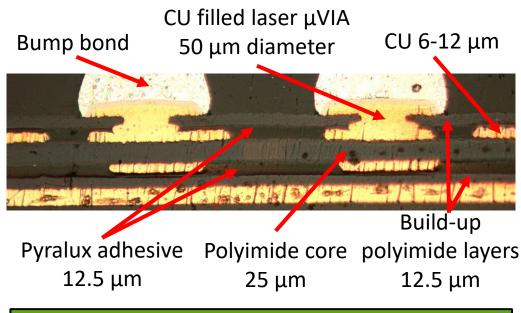

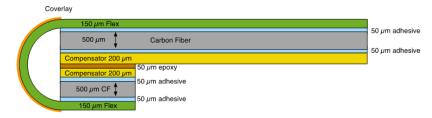

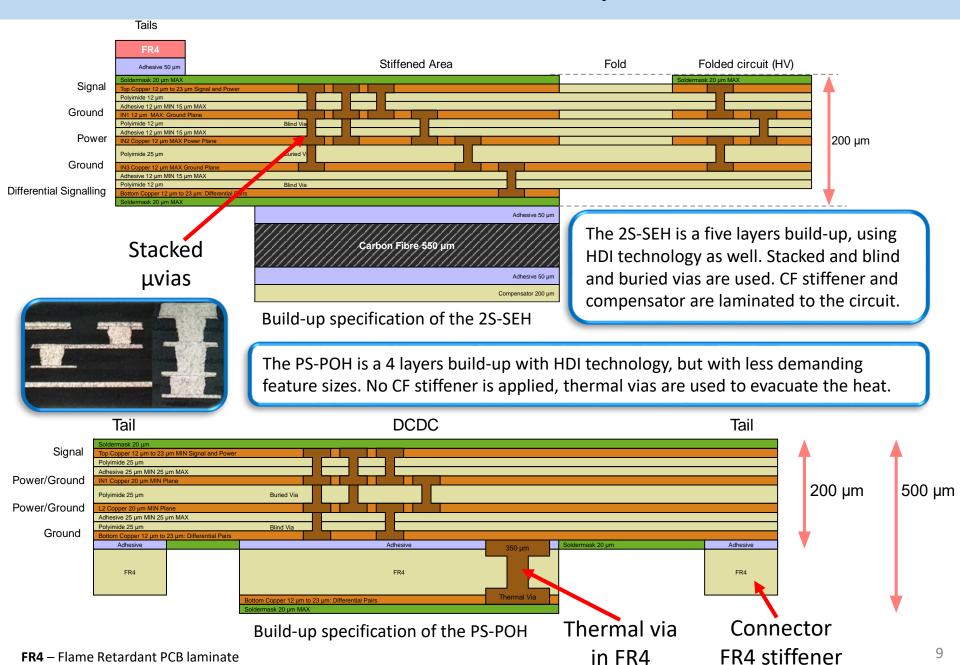

#### 2. Build-up of the Front-End hybrids and the PS-ROH

Build-up specification of the 2S-FEH, PS-FEH and PS-ROH

#### **Details:**

- 4 layers flex circuit

- HDI interconnect technology

- Linewidth and spacing 45/45 μm

- Laser μVias with 25-50 μm drill and 110 μm capture pad

- Carbon fibre reinforced with CTE compensation layer

- Flip-chip ASICs for reduced size and quick assembly

- Folded in order to match sensor wirebonding level

Build-up specification of the folded 2S-FEH

#### 2. Build-up of the 2S-SEH and the PS-POH

#### 2. HDI design practices and advices

## Few important HDI design practices:

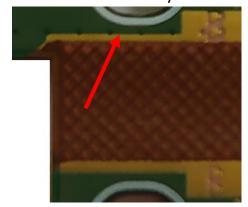

- Use crosshatched copper pattern to improve flexibility.

- Use "teardrops" at trace to pad connections to increase reliability.

- Avoid stacked uvias to further increase reliability.

- Balance copper area to achieve a flat surface, fill unused areas.

- Use "vent holes" to speed-up circuit drying process.

- Use silkscreen or solder mask barriers to control underfill flow.

- Use simulation tools with small size conductors to estimate impedance.

Underfill "barrier"

"vent holes" placed every mm

X-hatch can improve flexibility

Teardrop will decrease stress

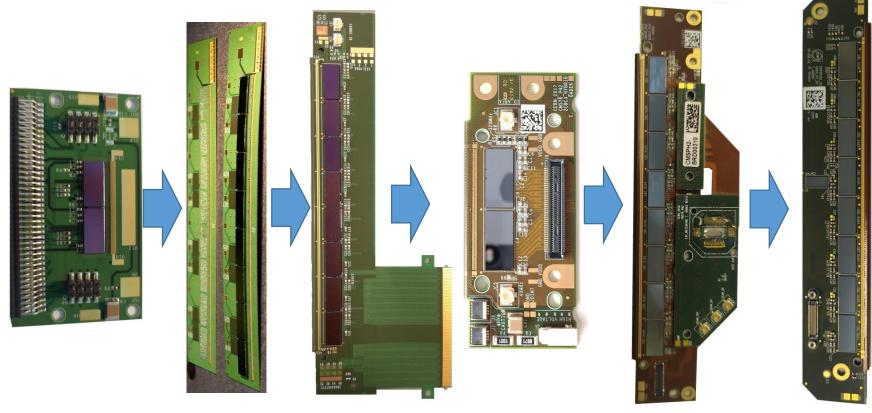

## Many prototype circuits were done for the 2S-FEH development:

The CF lamination technology was developed using these circuits.

2CBC2 hybrid with rigid 6 layers substrate

8CBC2 mechanical circuit with rigid 6 layers substrate

8CBC2 hybrid with CF stiffener glued with double-sided adhesive

2CBC3 hybrid with FR4 stiffened 4 layers flex 8CBC3 hybrid +

CIC mezzanine

with CF stiffened 4

layers flex and

compensator

2S-FEH-L with CF stiffened 4 layers flex and compensator, final geometry

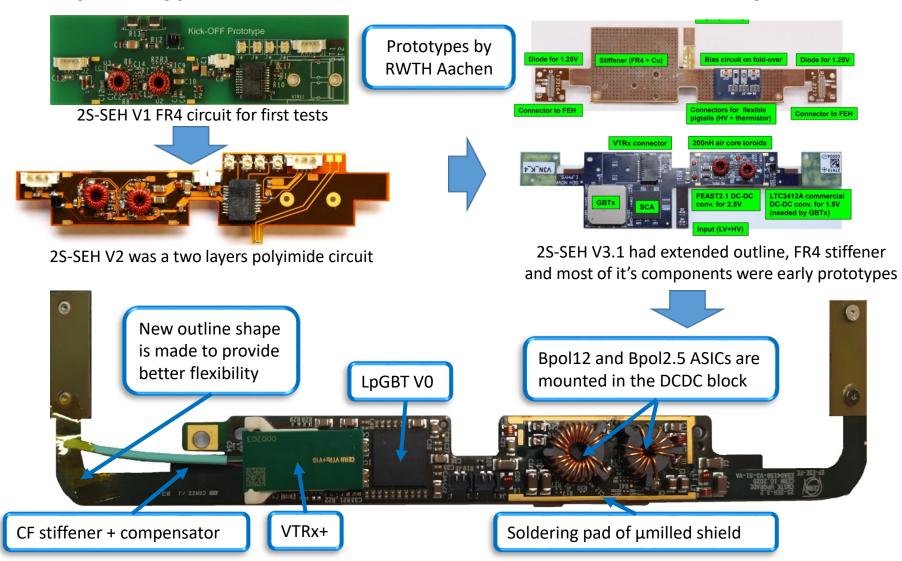

## Four prototype circuits were done for the 2S-SEH development:

The 2S-SEH V4.1 already uses close-to-final prototypes of all the components. The outline is nearly final.

# The PS-FEH development started in later phase:

• The experience with PS-MCK and 2S prototypes was essential to succeed with the first prototype.

PS-MCK circuit with 4 layers flexible circuit glued with soft adhesive to CF stiffener and folded

PS-FEH circuit with 4 layers flexible circuit glued with rigid adhesive to CF stiffener and folded

**CF** – Carbon Fibre

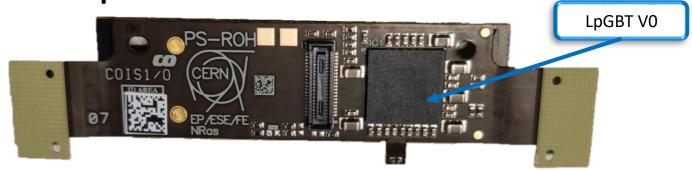

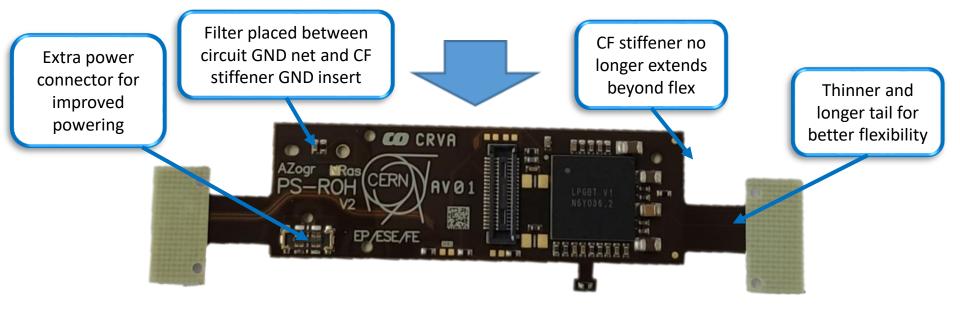

The PS-ROH had two prototypes as it was one of the latest prototype developments:

The PS-ROH V1 had an FR4 stiffened version to validate the design.

PS-ROH V2 is an FR4 stiffened prototype in order to validate the design changes before the pre-production. Assembly of these circuits was recently completed and validation is ongoing. V2.1 will be the pre-production version.

14

#### 3. Evolution of PS-POH circuits

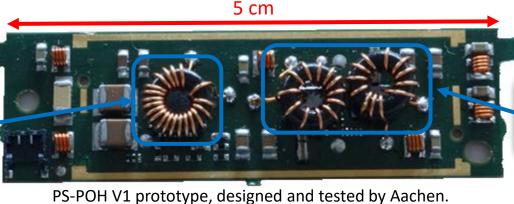

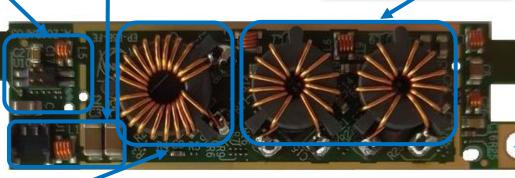

The PS-POH current version is the second prototype, one previous prototype was made by Aachen.

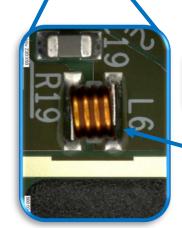

FEAST2 with 200nH hand-

made toroid. F= 1.9 MHz

bPOL2V5s with 100nH hand-made toroids.

1.25V and 1V output

2V5 output filter and additional

power connector.

Input connector and input filter

bPOL2V5s with  $100nH,18m\Omega$  industrial toroids, f=4Mhz.

Connector extension width was increased, alignment hole added.

GND tab added

bPOL12 with 220nH,30m $\Omega$  industrial toroid, f= 2.5Mhz.

PS-POH V2 prototype, with the latest design updates from CERN.

### 3. Issues discovered during the prototype production

### Soft adhesive

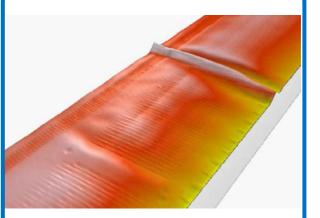

Wave formed during the reflow of a PS-MCK circuit due to insufficient adherence of the soft glue

Any surface non-flatness causes partial or catastrophic failure in the flip-chip assembly

# Hard adhesive

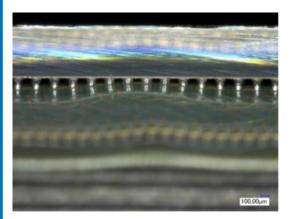

Bow formed due to the CTE mismatch of the flex substrate and the CF stiffener

Delamination formed by "popcorn effect" due to insufficient drying of the CF stiffener laminates

# Hard adhesive with compensator

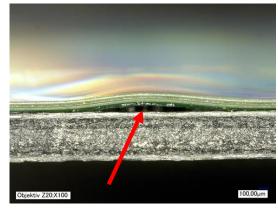

Polyimide-glass CTE compensator laminated on an 8CBC3 circuit with extended dry cycle.

Compensator can delaminate as well during the reflow soldering if the assembly is exposed to ambient for even few hours

#### 3. Other issues and solutions

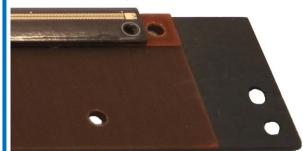

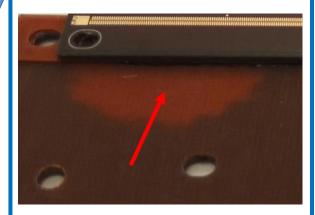

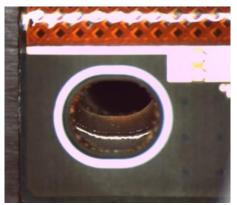

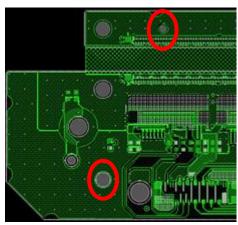

# Blockage of alignment holes

Alignment hole blocked by misaligned internal layers or adhesive leakage

Solution: New alignment holes to be used during the lamination process

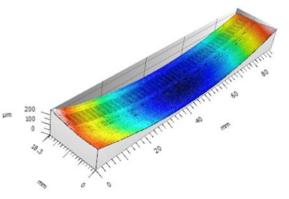

# Circuit stretch after CF lamination

| Object | Av. dev. | RMS   |

|--------|----------|-------|

| PS-FEH | 140 μm   | 23 μm |

| 2S-FEH | 147 μm   | 22 μm |

On average the wire-bonding array was  $140-147~\mu m$  longer than nominal after the CF lamination. Solution: Gerber data will be scaled.

# **Elevated noise in case** of floating CF stiffener

Solution: gold plated aluminium inserts are press fitted into the CF stiffeners and connects them to the hybrid's GND

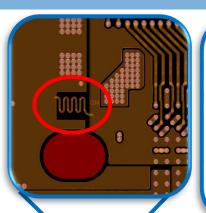

# Soldermask – coverlay transition cracking

Crack in the soldermask in the transition zone between soldermask and coverlay

Solution: Plated transition zone between coverlay and soldermask next to the bend-zone

#### 3. Performance of 2S module prototypes from current prototypes

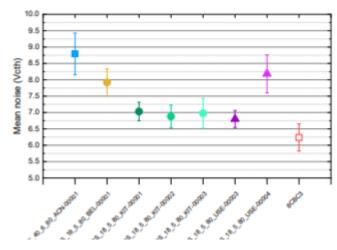

Several module prototypes were built at different assembly centres. Modules are fully functional, powering, communication and control works as intended. Noise level is slightly higher than expected, investigation is currently on-going.

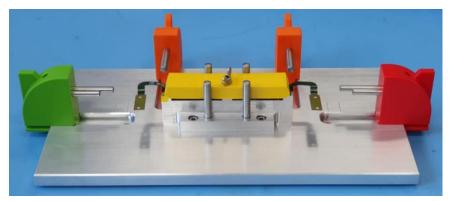

2S-SEH pre-bend tool in operation

2S skeleton being assembled for a module

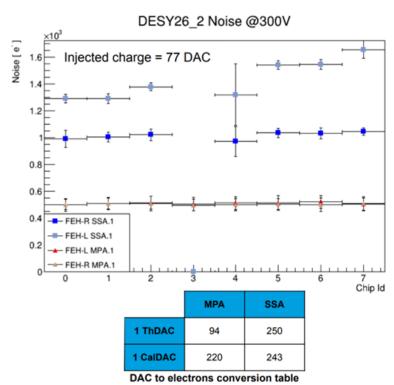

Noise levels measured with new 2S-modules. Expected noise level from simulations is 1000 e (6.41 Vcth). 1Vcth = approx. 156e

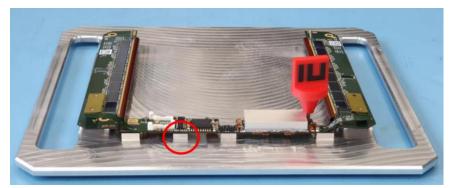

#### 3. Performance of PS module prototypes from current prototypes

There is a smaller number of PS modules constructed compared the to 2S modules. Modules are fully functional, powering, communication and control works as intended. The noise level in PS modules is also slightly higher than expected. Thermal performance and noise performance in the detector structures are under investigation.

# Assembled functional modules

DESY. | System Test Meeting | 04.11.2021 | Younes Otarid

|        | DESY26_1         | DESY26_2                      | DESY40_3          |

|--------|------------------|-------------------------------|-------------------|

| Module |                  |                               |                   |

| кон    | ROH-v1, lpGBT-v0 | ROH-v1, lpGBT-v0, (I2C patch) | ROH-v1 - lpGBT-v0 |

| РОН    | POH-v2           | POH-v2                        | POH-v2            |

| FEH-L  | _                | CIC1, SSA1, MPA1              | CIC1, SSA1, MPA1  |

| FEH-R  | CIC2, SSA1, MPA1 | CIC1, SSA1, MPA1              | CIC1, SSA1, MPA1  |

| Status | Damaged          | Functional                    | Work in progress  |

Current PS modules constructed or being constructed

Expected noise level for SSA: 800e Current noise level of SSA: 1000e – 1500e

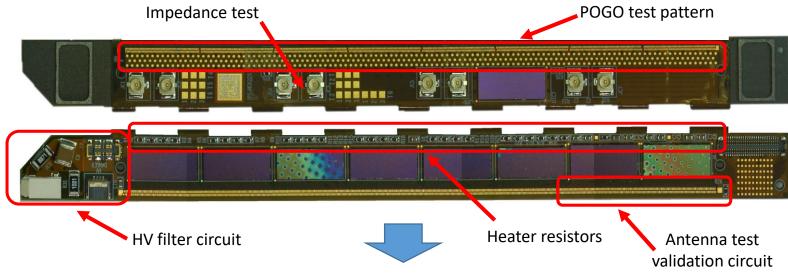

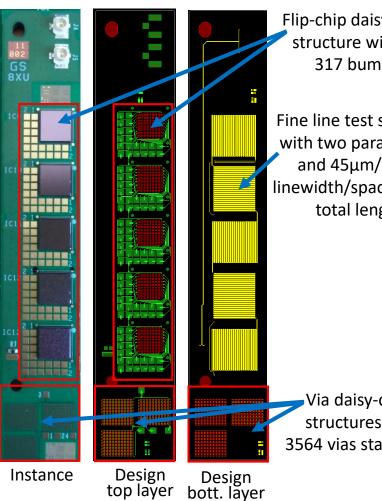

#### 3. Reliability testing of test coupons

#### One of the test coupon geometry used

Flip-chip daisy-chain structure with 5 x 317 bumps.

Fine line test structure with two parallel nets and 45μm/50μm linewidth/spacing 1.6m total length.

Via daisy-chain structures with 3564 vias staggered.

Flip-chips with SAC305 bumps.

top layer

Connector test coupons.

Daisy-chain test flip-chip with 254 µm pitch.

## **Key points:**

- Irradiated samples @ 1MGy

- 1000 thermal cycles from -35 °C to 65 °C, max 7 °C/min slope.

- No via failures, no fine line failures were detected.

- Only very bad quality flip-chip assemblies failed after 1000 cycles.

- HDI circuits and Flip-chip technology are robust.

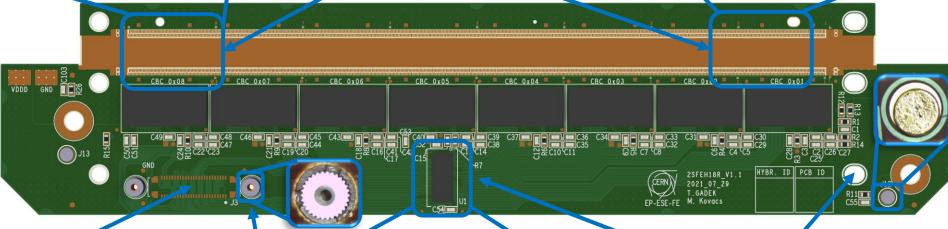

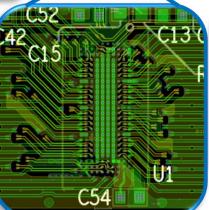

#### 4. 2S-FEH design for pre-production

High-density analogue routing designed to minimize cross-talk and noise pick-up Coverlay applied in the bend-zone to prevent from soldermask cracking observed in previous prototypes

Variable connector placement in different versions to reduce 2S-SEH types

MSO4 M1 self-clinching nut for connector alignment and fixing

CIC differential fanout with 56 pairs, all referenced to GND to improve signal integrity Additional alignment holes and slots for better alignment and less adhesive flow during lamination

#### 4. 2S-SEH design for pre-production

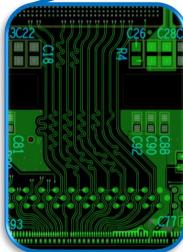

#### 4. PS-FEH design for preproduction

GND plane under analogue part of the front-end ASICs is isolated with resistive and inductive connection to reduce DC drop and noise coupling

Spacer airpocket vent holes

Locking insert fitting in the 1 mm alignment hole can be installed to secure the power connector in place

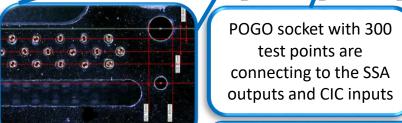

The POGO connector pattern provides connection for all the SSA output and MPA input signals, providing a full-scale functional testing

SSA to MPA

interconnection

is fully length

match in order

to assure

maximum signal

quality

Spring connectors are installed on the hybrids in order to provide sufficient GND connection for the CF structures

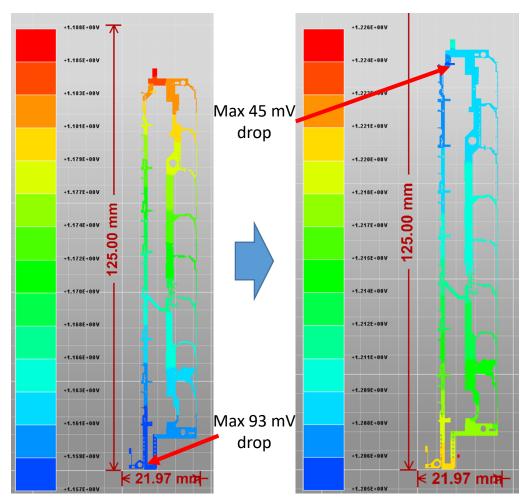

# DC drop simulations were made on the prototype design:

The simulation results concluded in a change in the powering scheme for 1.25V

Voltage drop on the 1.25V rail of PS-FEH-R, original scheme

Voltage drop on the 1.25V rail of PS-FEH-R, updated scheme

Original current flow scheme for 1.25V

Updated current flow scheme for 1.25V

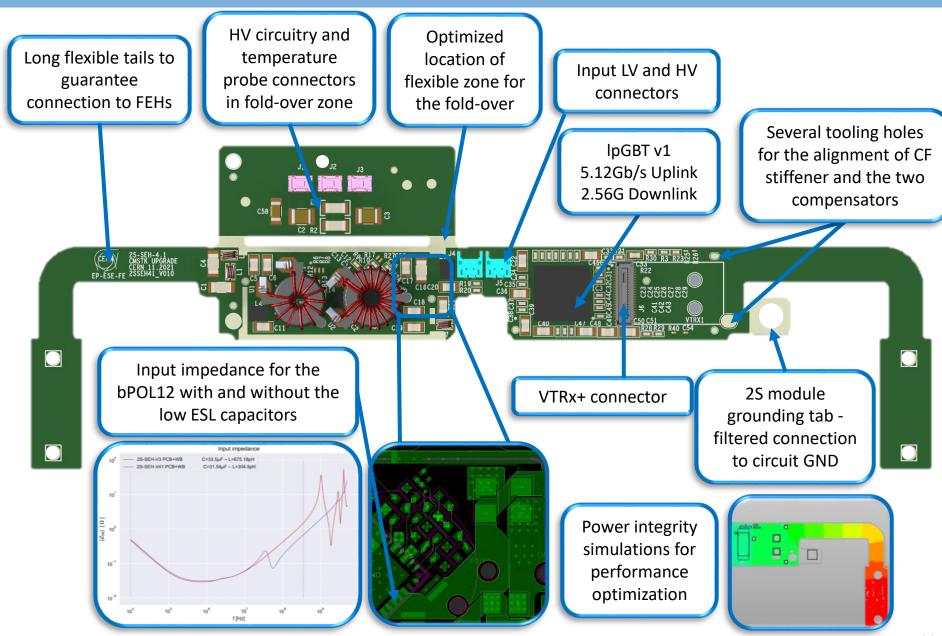

#### 4. PS-ROH design for pre-production

#### 4. PS-POH design for pre-production

PS module GND tab – filtered connection to circuit GND

Remote sensing at connectors for 1V25 and 1V05 rails

Thermally conductive paste placed on top of coils before shield assembly

Additional power connector for PS-ROH 1.25V connection

STATE OF THE PROPERTY OF THE P

PS-POH v2.1 EP-ESE-FE CMSTK-PH2 09/2021

Long flexible tails to adapt to all PS module variants

Output/Input pi filter capacitors in opposite facing pairs

Shield soldering pad and alignment holes

Conformal coating in critical areas to avoid shorts with shield

Custom micro-milled Aluminum shield

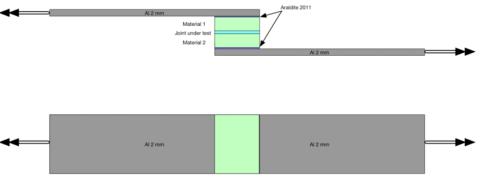

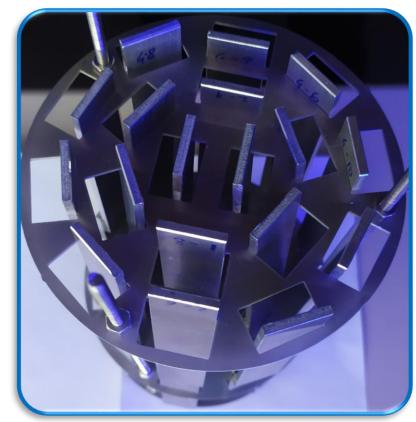

#### 5. The radiation tolerance test plan

- A test plan was created to test the radiation tolerance of all the materials used in the hybrids. Test is focusing on the adhesives and the circuit substrate,

- Shear tests will be done before and after irradiation of samples. Irradiation dose will be 1MGy at 6kGy/h.

Standard size shear test samples will be used

- Materials tested:

- H70E epoxy, Prepreg, EP48TC thermal epoxy, TNP400 and semicosil for PSFEH fold-over, Nitto adhesive proposed for 2S-SEH fold, Therm-a-Gap GEL30 silicone based thermal paste.

- Flex stackup, carbon fibre laminates, AIN spacers, underfills, conformal coatings.

Samples ready for the irradiation in the research reactor in Zagreb

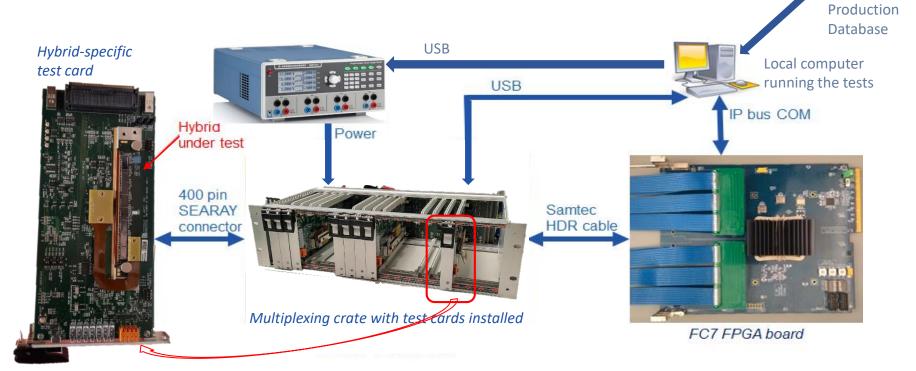

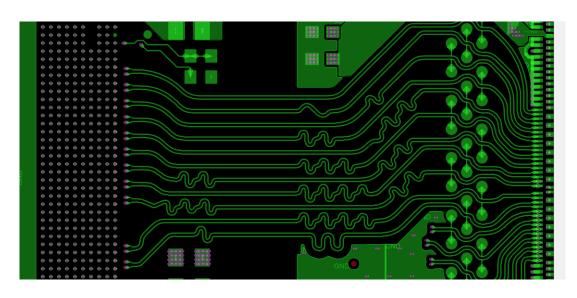

#### 5. The hybrid test system

- A crate based test system was designed in order to provide a platform for the hybrid testing. It is based on a high-speed multiplexer backplane.

- Three backplanes can be mounted in one crate, 12 test card can be inserted.

- Test peripheries are controlled over USB and IOs of the FC7 FPGA board.

- Local database is saved on the test PC and test results are synchronized with the CMS database when network connection is available.

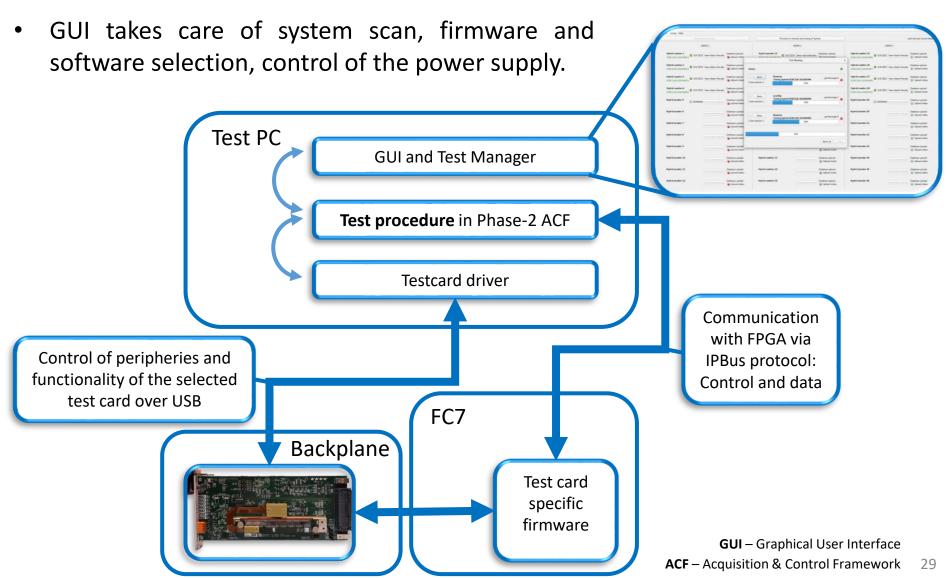

#### 5. Software architecture of the test system

• Common GUI is developed for the testing of all hybrid types. Details are hidden from the operator. Test results are indicated in good/bad format.

#### 5. 2S-FEH test card

Digital tests: All digital communication of the ASICs, I<sup>2</sup>C lines, CLK, Fast command,

Reset lines. Tests can be done at different supply voltages tuned by on-board LDO.

Analogue tests: Supply voltages and consumption, temperature, CBC inputs for

Optional pre-emphasis switches in case of more losses in cables.

Antenna test system

– pulse generation for open finding

Searay 400 pin backplane connector with guide pins

Power connector for standalone operation.

Flex cable, different for L and R hybrids. Mounted with test-grade connector, rated for 3000 cycles 2S-FEH-R 4.0 mm hybrid under test Custom stainless steel socket compatible with all 2S-FEH variants

**LDO** – Low Dropout Regulator

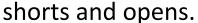

#### 5. 2S-SEH test card

Test card allows for full digital testing of the LpGBT and VTRx+ communication. Performance of the DCDC converters can be fully characterized (efficiency, setup time, voltage levels). HV leakage can be measured as well. Design by RWTH Aachen.

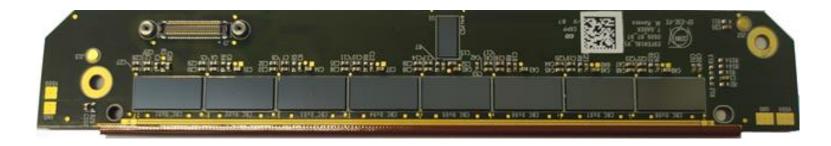

#### 5. PS-FEH test card

Press plates are used to force the hybrids on the POGO pins with up to 7 kgs.

BRD00470 CASS

Custom made plastic pusher is pressing the hybrid on areas without components.

SSA output signals are multiplexed in pairs with high-speed multiplexers Flexible connectors are designed for the L and R hybrid types. The same test card can host all the hybrid types.

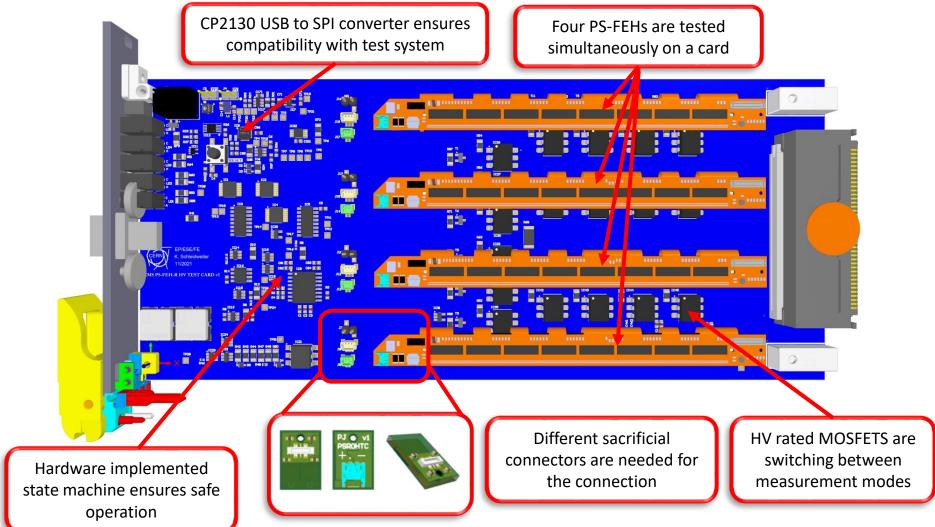

#### 5. PS-FEH HV test card

HV test could not fit in the PS-FEH test card due to the complex geometry needed to press the hybrid on the POGO socket. Routing and fitting of components were also difficult. A separate test card is being designed to carry-out the HV test.

#### 5. PS-POH test card

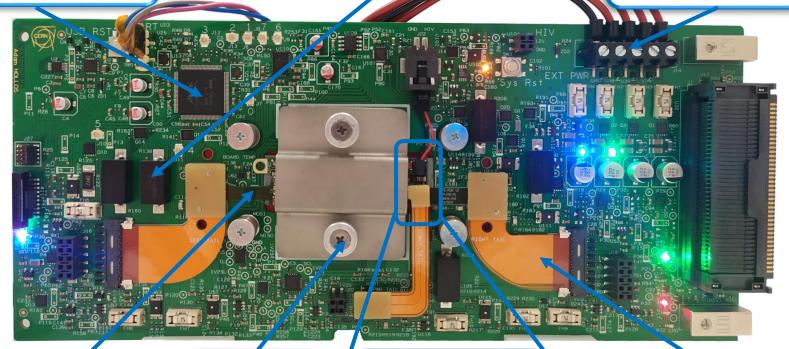

• Test card allows for very precise characterization of the DCDC converters. Measurements: Efficiency, output voltage, output ripple, temperature, setup time.

On-board µcontroller for extended characterization of the DCDC converters

MOSFET and resistor in series to optimize the heat load of the MOSFET.

Standalone operation with the usage of external power connector

PS-POH under test

Special pressure limiting screws are used to tie down the pressure plate

Flexible sacrificial connections to extend the lifetime of the board and compatibility

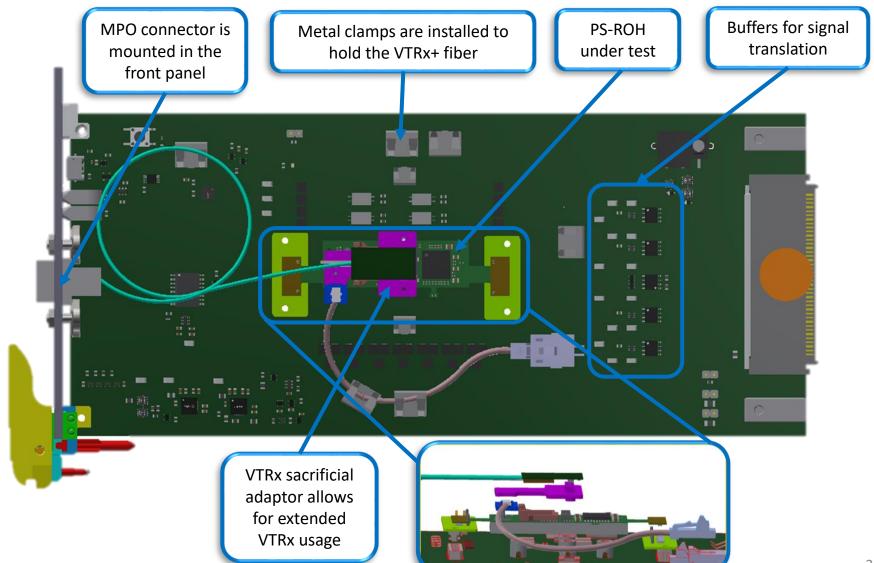

#### 5. PS-ROH test card

• Test card allows for the testing of the digital IOs and fusing of the LpGBT. Functionality of the connectors and the VTRx+ are tested as well.

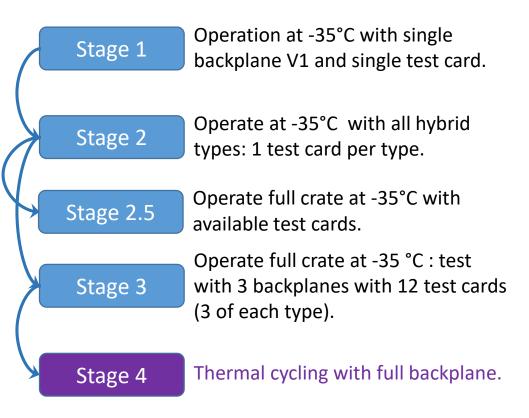

#### 5. Test system verification and cold tests

- The test system was used to test all the prototype hybrids. Test procedures were developed with the prototypes.

- A cold test plan was set-up and currently in progress to validate the operation of the system in cold.

- Currently more than 300 thermal and mechanical cycles are done. No failures were developed during the tests apart from the initial bugs identified.

Test crate in the climatic chamber during the cold testing

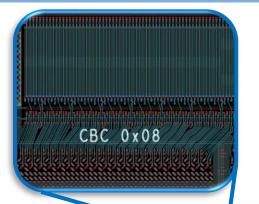

## 6. Design collaboration between ASIC and hybrid design

- Design for testability was a key aspect during the hybrid design phase. The first architecture of the PS module had the clock and FCMD distributed from the MPA.

- As the hybrid has no MPA during the test phase, the buffering was replaced to the SSA. Other test features were implemented in the SSA such as programmable test vectors on the serial outputs.

- The optimization of the SSA and MPA pinout was with high importance. Any of the IOs crossing would have made the design unroutable.

MPA and SSA interconnection was fully optimized in order to help the success of the hybrid design.

- Many hybrid prototypes were developed in the last 10 years. This activity was essential to reach the maturity of the designs and the manufacturing processes.

- Many issues were discovered during the prototyping phase. Most of these issues are resolved today and the hybrids are fully functional and ready for the preproduction.

- Module prototypes are being built from the hybrids. Mechanically and electrically

the modules are functional and no major issues were discovered. Noise

performance of the modules is slightly worse than expected problem is being

explored currently.

- A crate based test system was developed for the production testing of the hybrids. Six test cards were (are) developed for the testing. The verification of the system is currently on-going. No major issues were discovered so far.

- Collaboration between ASIC design and hybrid design was essential during the design phase. The PS-FEH could not be designed without this level of optimization.

- Still a lot of work is ahead to arrive to the mass production of hybrids and modules, but we can see the light in the end of the tunnel!

# Thank you for your attention! Big thanks for the hybrid design team!

#### Davide Ceresa will continue with the ASIC details