# **PASSIVE CMOS SENSORS**

IN 20 YEARS...

ECFA 2021

23.04.2021 11:15 David-Leon Pohl

# SOLID STATE DETECTORS FOR FUTURE (4D) TRACKERS

This talk

### **OUTLINE**

#### 1. Introduction

- What are "passive" CMOS sensors?

- Benefits and challenges

#### 2. Status

- History

- Passive CMOS sensors for silicon trackers at the HL-LHC-pp

- 3. Outlook & Summary

#### PASSIVE CMOS SENSORS

- Current situation:

- Full-wafer lithography with 150 mm wafers for passive sensors in silicon tracking detectors (CMS/ATLAS)

- Area of silicon tracking detectors is increasing

- → Increasing demand for large-scale sensor wafer production

- Only few <u>large-scale suppliers</u> available

- Risk: single-vendor scenario

- Some investigations into 200 mm wafer processes for silicon sensors, e.g.:

- Silicon strip tracker: <u>10.1016/j.nima.2018.06.069</u>

- CMS High Granularity <u>Calorimeter</u>

#### Idea:

- Use a CMOS processing line on large, high-resistivity wafers (kΩ-cm)

- N-well/p-well/metal layers for sensor implantations and biasing

- No active components → "passive CMOS"

- Stitching over reticle boundaries for large sensor tiles

## PASSIVE CMOS SENSORS: CHALLENGES AND BENEFITS

- Find interested CMOS foundry:

- Mainly of interest for the foundry, if a large production run is at the horizon

- Good feedback on design helpful (some design rules might be violated)

- Fast production, cheap large-scale production, expensive engineering runs:

- MPWs allow for design optimizations with small prototypes (guard rings, implant geometry, ...);

custom HR substrates sometimes not available for MPWs

- Engineering runs required (with minimum batch sizes) to develop large sensor tiles and production processes (stitching, back-side processing, thinning, dicing)

- Possible cost reduction: current hybrid pixel costs: 50% hybridization, 40% sensors, 10% readout chip; sensors 3-4 times cheaper

- Easier access to wafer-scale industrial processes, due to wafer size ≥ 200 mm, e.g.:

- Thinning without handling wafer (TAIKO process)

- Wafer-to-wafer bonding > ultra-thin low-cost hybrid pixels?

5/17

### PASSIVE CMOS SENSORS: CHALLENGES AND BENEFITS

- Risk that process is not available after some time (company changes philosophy)

- Less worrying, since integration density is not as important as for active sensors/RO electronics

- → Many companies to select from (AMS/TSI, ESPROS, LFoundry, TowerJazz, Toshiba, XFAB, ...)

- Most design rules are not relevant for the large structures of a sensor (usually no need for fine-pitch patterning)

- Design tools and PDK for the process are available and ease design

- Porting a design to a new process is not too difficult

- Time scale ~ 1 month

- Developing a new large passive sensor (incl. few iterations; back-side processing): 1 2 years

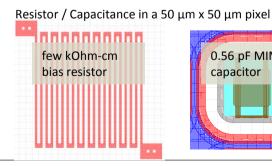

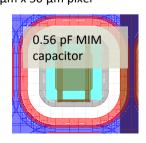

- Enhance sensor design using CMOS process features:

- Poly-silicon resistors → connection to a bias grid

- MIM capacitors for AC-coupling → no leakage current into readout

- Many metal layers for redistribution

#### PASSIVE CMOS SENSORS: BYPRODUCT OF DMAPS EFFORTS

#### (Passive) Test structures

Test structures / passive diode arrays in many CMOS processes produced, e.g.:

- AMS 180/350 nm HV-CMOS

- LFoundry 150 nm CMOS

- TowerJazz 180 nm CMOS

- XFAB 180 nm SOI CMOS

- Different substrates investigated

- Varying designs: guard rings, pixel isolation, implantation geometries

#### **Hybrid pixel prototypes**

Prototype on ATLAS FE-I4

#### Full size, large sensors

- First dedicated submission for vendor qualification for ATLAS/CMS

- "Full-size" pixel sensors and strip sensors

2020

**Byproducts of DMAPS efforts**

**Dedicated submission**

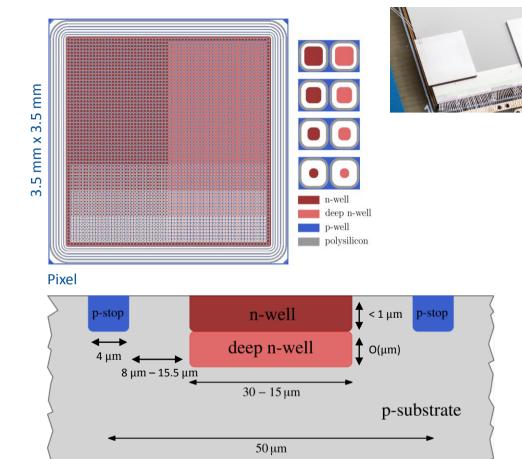

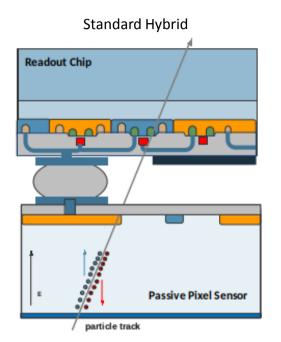

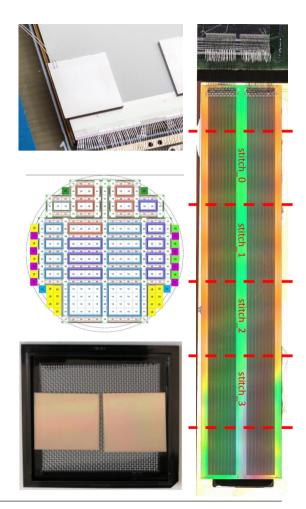

## **SMALL PROTOTYPE**

- High resistivity 4-5 k $\Omega$  cm p-type CZ wafer

- 50  $\mu$ m x 50  $\mu$ m pixels in 64 × 64 matrix

- 100 μm thickness with TAIKO thinning

- Bump bonded to RD53A

- DC coupled pixels:

- No biasing structure

- Variation of implantation width:

15 μm 30 μm

- Variation of n-well depth: n-well (NW) and deep n-well (DNW)

- More info in:

https://doi.org/10.1016/j.nima.2020.164130

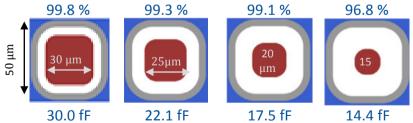

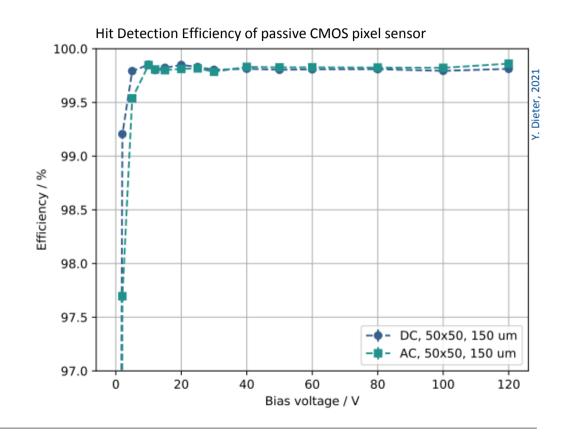

### **EFFICIENCY MEASUREMENT: PIXEL SENSOR**

- R/O chip parameters:

- Linear FE of RD53A

- Threshold: ~1000 e

- Noise occupancy: < 10<sup>-6</sup>

- Before irradiation: > 99.5 % at 5 V only

- $5 \times 10^{15} \, n_{eq}/cm^2$ : > 99 % efficiency (@ 100 V)

- $1 \times 10^{16} \, n_{eq}/cm^2$ : > 99 % efficiency (@ 400 V)

- Mean efficiency and capacitance for different fill-factors

@ 400 V:

Capacitance measurement in:

https://doi.org/10.1088/1748-0221/16/01/P01029

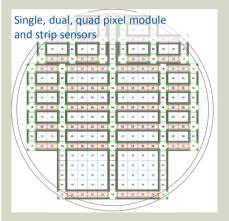

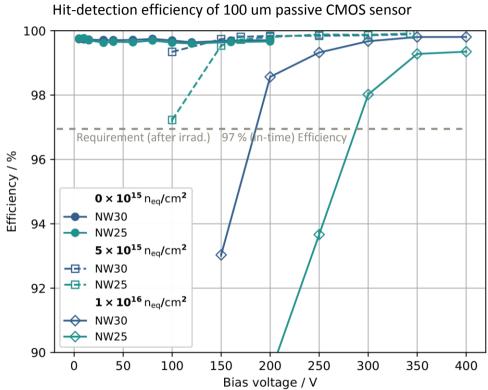

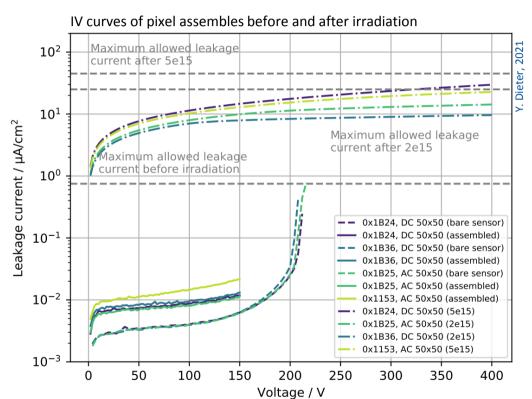

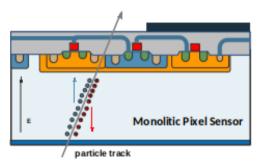

### FULL-SIZE PASSIVE CMOS SENSOR SUBMISSION

- Goal: qualify a CMOS vendor for the production of (pixel-) sensors for ATLAS/CMS

- Design:

- Up to full-size 4 x 4 cm<sup>2</sup> pixel sensor tiles

- Compatible with RD53 R/O chip development

- Different pixel flavors:  $50 \times 50 \mu m^2$ , 25 x 100  $\mu m^2$ ; AC or DC coupled, biasing with > 4 kOhm poly-resistor)

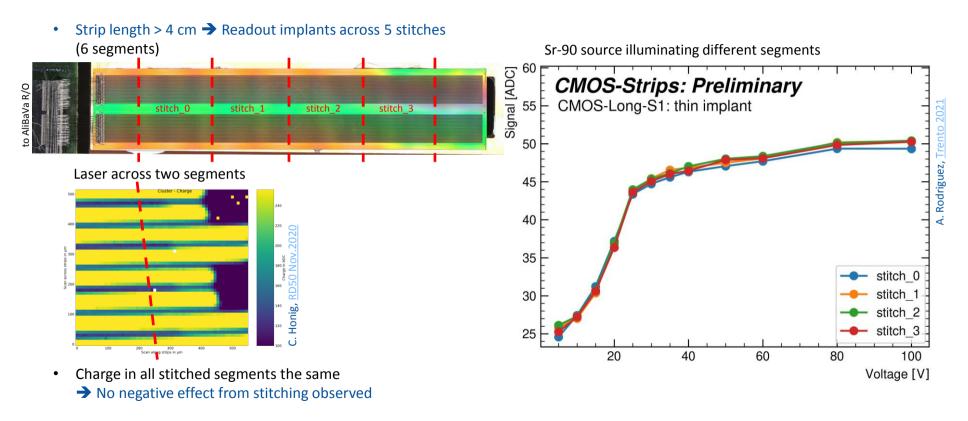

- Strip sensors: > 4 cm; 75.5 um pitch

- Float-zone wafer material

- LFoundry 150 nm 1.8V CMOS process

- Optimization for production:

- Thinning to 150 μm with handling wafer, backside implantation @ CMOS fab

- Backside Al-Si metal, UBM, Flip-chip

@ ATLAS ITk hybridization vendor

Pixel sensors

Strip sensors

"Quad" pixel sensor

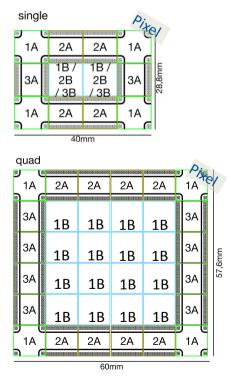

### **STITCHING**

- Sensor size > reticle size

- → Stitching needed

- Additional rules for stitching (no fine-pitch)

- → Not too relevant for sensor designs

- Different blocks:

Edge blocks with guard rings, strip sensors and test structures

Center blocks with different pixel flavors

AC coupled

2B

50 x 50 μm²

DC coupled 3B 25 x 100 μm<sup>2</sup> Different configurations possible

→ arrange and repeat blocks in different order

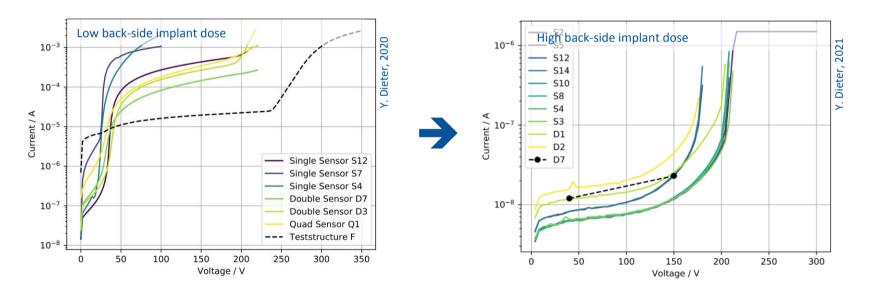

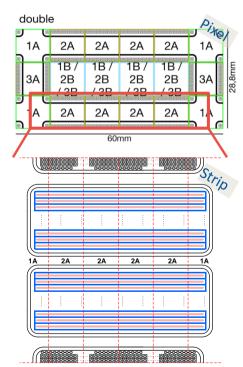

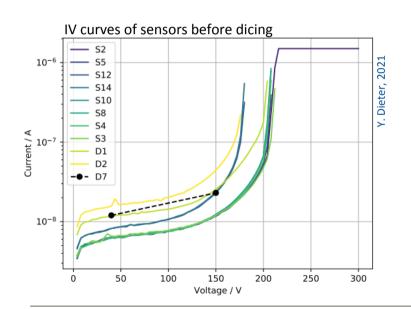

## **IV CURVES**

· Sensor requirements for HL-LHC matched

## **DETECTION EFFICIENCY MEASUREMENT: PIXEL**

- R/O chip parameters:

- Linear FE of RD53A

- Threshold: 1200 e

- Noise occupancy: < 10<sup>-6</sup>

- Efficiency of above requirement (97%)

- DC and AC, 50 x 50 μm<sup>2</sup> pixels measured

- Unirradiated at 80 V (V<sub>dep</sub> + 50 V): 99.85 % efficiency

- For V > V<sub>dep</sub>:

No difference between AC and DC

## **CHARGE MEASUREMENTS: STRIP SENSORS**

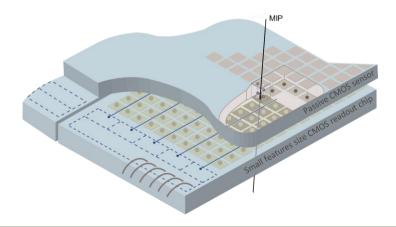

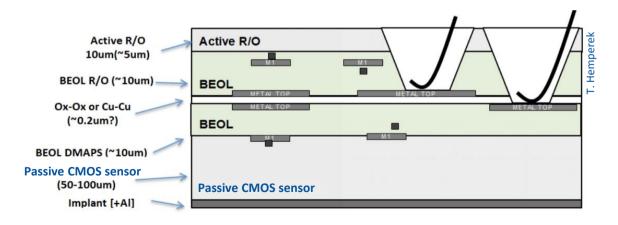

# OUTLOOK: ULTRA-THIN, LOW-COST HYBRID PIXELS?

- Future of hybrid detectors also depends on interconnection technologies:

- Remove costly and complex chip-to-chip bump bonding → chip-to-wafer / wafer-to-wafer

- See ECFA Interconnection Technologies talk by T. Fritzsch today 15:00

- Move to wafer-to-wafer bonding (requires compatible FE and sensor wafers)

- Enables smaller pixel pitches (restricted by bump bonding to ~ 20 um)

- Thinning after bonding (e.g. sensor 50-100 um; FE ~ 20 um)

- Requires access to R/O pads from back side (via-last TSV / etching to metal layer on R/O chip)

- Explored within <u>AIDAinnova WP6</u>

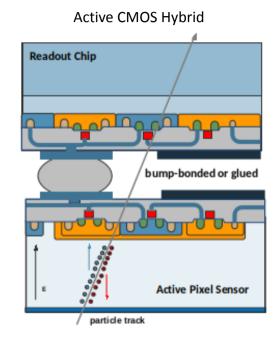

# **OUTLOOK: ACTIVE CMOS HYBRIDS?**

Depleted Monolithic

→ ECFA talk

by P. Riedler today 14:30

- CMOS active hybrids for high performance solutions (extreme irradiation and hit rates):

- Active CMOS sensor (amplification included)

- Digital readout: smaller feature size process for digital logic

### **SUMMARY**

- Passive sensors using a CMOS process:

- Access to more vendors for large-scale silicon sensor production

- Benefits from CMOS process (fast/cheap/process features)

- Relatively simple designs, easy to port

- Status:

- Performance is equally good as for "common" planar sensors (rad. tolerance, detection efficiency, CCE, depletion depth, …)

- Stitching for large sensor tiles successfully demonstrated

- The future of "passive CMOS" depends whether there is a future for passive sensors

- Large-area hybrid detectors? → R&D for cheaper + easier sensor to R/O interconnections

- Monolithic sensors could be the more attractive alternative in some scenarios

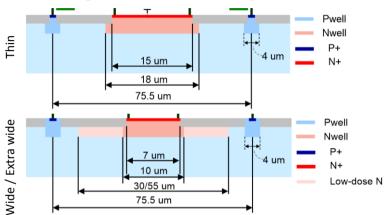

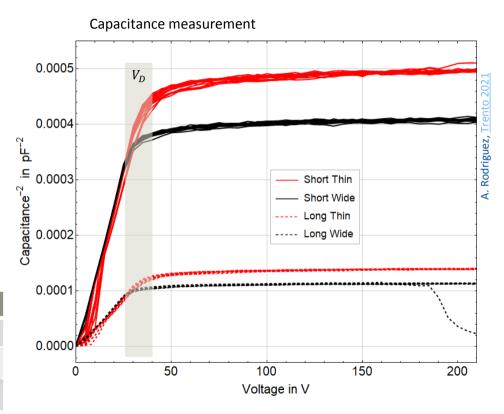

## **CAPACITANCE MEASUREMENTS: STRIP SENSORS**

Different geometries of readout implantation

• Capacitance at full depletion  $(V_D \sim 25 - 40V)$

| Flavor     | C / L [fF / mm] | <u> </u>    |

|------------|-----------------|-------------|

| Thin       | ~ 37            | Drey.       |

| Wide       | ~ 62            | Preliminary |

| Extra wide | ~ 144           |             |

## **BACKSIDE PROCESSING**

- Changed backside processing vendor to simplify potential production for ATLAS

- First-batch: high current at full depletion V<sub>dep</sub> ~ 30V, due to inadequate interface from bulk to backside metal

- Increase of implant dose solved issue