Speaker

Description

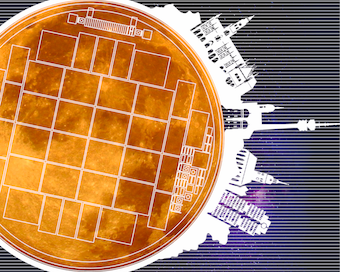

The utilization of radiation-hard CMOS processes for sensors of hybrid pixel-detectors is investigated. The benefit of such an approach is industrial sensor fabrication on large wafers with potential high throughput and yield, and low costs. Further, CMOS processes offer multiple metal and polysilicon layers, as well as metal-insulator-metal capacitors that can be employed for AC-coupling and redistribution layers. Passive CMOS-sensors with $50$ x $250\,\mathrm{\mu m}^2$ pixels are investigated in view of the ATLAS pixel-detector upgrade. They are thinned to $300\,\mathrm{\mu m}$ and $100\,\mathrm{\mu m}$, backside processed, and read out with the ATLAS FE-I4. Break-down behavior, yield, and hit-detection efficiency after irradiation to $1.1 \cdot 10^{15} \mathrm{N_{eq}/cm^2}$ are discussed. The influence of AC-coupling and a small collection node on capacitance and hit efficiency is also investigated. Preliminary findings for $50$ x $50\,\mathrm{\mu m}^2$ pixel-sensors compatible with future pixel readout-chips are presented.